Energy Efficient Digital Electronic Systems Design for Edge-Computing Applications, through Innovative RISC-V Compliant Processors.

By

Abdallah Cheikh عبدالله نبيل الشيخ

A Thesis Submitted to the Department of Information Electronics and Telecommunication Engineering (DIET) La Sapienza Università di Roma

> DOCTOR OF PHILOSOPHY February 2020

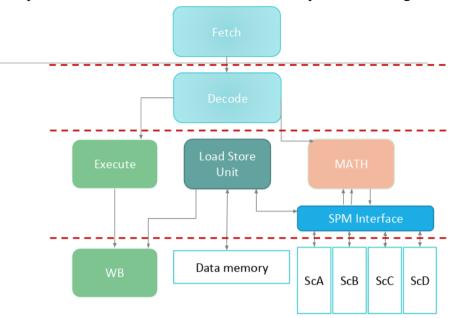

Prof Mauro Olivieri (Thesis Supervisor)

## Acknowledgements

These three years of doing research at the LSD lab at Sapienza have passed like the wind. Throughout my journey on this PhD career, I slowly transformed from being a High-Power Electrical Engineer, into a Low-Power Computer Architect for IoT devices and Embedded Systems. The only thing I regret is the amount of strain I placed on my eyes, caused by staring daily at the computer screen for over 12 hours. However, I am much more thankful than regretful for the things I have experienced in this wonderful journey.

First and foremost, I am thankful to all mighty God الله for giving me everything I have asked for, and more. He facilitated my means to travel to Italy, He surrounded me with kind hearted, and supportive people that helped me in a foreign country in which I barely understood the language, and He was always my guide in the good and the bad moments in life. I never had to beg anyone for anything neither did I feel at any point in time the struggle to sustain myself. God is great, and no matter how many times I thank Him, I feel that it is not enough and that I should be ever more thankful.

Needless to mention, but nonetheless I am thankful for both my parents that had never batted an eye when I asked them for help. They covered any financial shortcomings I had throughout my PhD career. They provided me with every kind of support in order help me succeed in my career. My parents never once have abandoned me, and they always prayed for my success. As they grow into their older days, I wish to support them by giving back at least a fraction of what they'd been giving me my entire life.

Second of all, I would then like to thank my professor and thesis supervisor Mauro Olivieri, as I feel eternally grateful for his support throughout my PhD career. I contacted Mauro in early July 2016 for a chance to pursue a PhD career at Sapienza, and Mauro quickly responded to my request, helping me every step of the way in the application process until I finally got admitted to the PhD program. Mauro continued his support and guidance throughout the years providing me with opportunities to pursue conferences in different parts of Italy and Europe. In May 2018 he again provided me with the unforgettable and wonderful opportunity to move to Barcelona and collaborate on the European Processing Initiative (EPI) project. In Barcelona, I met amazing people and gained a lot of experience in the field of computer architecture. Mauro till this day continues to be a great support, as he constantly provides me with wonderful opportunities at every turn, and for that I am always very grateful, and have very much respect for all what he has done for me.

Furthermore, I am grateful to my amazing friend and mentor Antonio Mastrandrea. Antonio from day one in Italy was there for me. The reason I managed to stay standing on my feet in Italy, without getting lost or stranded was Antonio himself. He helped me literally in anything I asked for. Antonio was basically my guide for everything in Italy. Not to mention throughout my PhD he continuously provided a lot of support in various areas I lacked experience in. Antonio is a great friend, and a great support, and I really enjoyed his company throughout my PhD career. Thank you, Antonio!

I have met a great deal of people in the past three years, among them is my great friend Simone Ponzio. Simone volunteered to help me with my work continuously for more than 8 months. Simone helped, me perform the earlies parts of verification of my work in the second year and he also was a great friend and a very fun guy to be around. Then came along my colleague and my dear friend Stefano Sordillo. Without Stefano's amazing hard work and his collaboration on common areas of interests in our researcher, I would not have had my work results flourish as they had today, Stefano was the software developer that made the complex tests which benchmarked my work. Stefano was a great help at all times, even on the weekends. For all the people that I have met, I want to say you were all amazing, and thank you all for giving me the pleasure of meeting you.

As a final note I would like to express my gratitude to the Italian government, and their vision to provide a career opportunity for a both foreign and national students equally by allowing them to pursue a PhD career all under their expenses, and without any bias in the selection process be it race, nationality, gender, or religion. Italy in that sense I consider to be a model country, and I owe my thanks to all the Italians for their kindness and hospitality towards me, and other foreign researchers as well.

# Table of Contents

### Contents

|             |                                                            | 1  |

|-------------|------------------------------------------------------------|----|

| Table of    | Contents                                                   | 1  |

| List of Fig | gures                                                      | 5  |

| List of Ta  | bles                                                       | 7  |

| Abstract    |                                                            | 8  |

| Organiza    | tion of the Dissertation:                                  | 9  |

| Chapter :   | 1 Preface                                                  | 10 |

| 1.1.        | Internet of things                                         | 10 |

| 1.2.        | Energy efficient IoT devices:                              | 13 |

| 1.3.        | Artificial neural networks                                 | 14 |

| Chapter 2   | 2 RISC-V and the Klessydra Processor Family                | 16 |

| 2.1.        | Motivation behind adopting RISC-V                          | 16 |

| 2.2.        | Background                                                 | 16 |

| 2.3.        | Instruction set architecture briefing                      | 17 |

| 2.4.        | Custom instruction set extensions                          | 19 |

| 2.5.        | RISC-V support in Klessydra                                | 19 |

| 2.6.        | Patches to the riscv-gnu-toolchain:                        | 20 |

| 2.7.        | Concluding remarks                                         | 21 |

| Chapter 3   | 3 The PULPino Microcontroller Platform                     | 23 |

| 3.1.        | Motivation behind choosing PULPino                         | 23 |

| 3.2.        | Background                                                 | 23 |

| 3.3.        | PULPino native processor cores                             | 24 |

| 3.4.        | Embedding non-native Klessydra processing cores in PULPino | 25 |

| Chapter-    | 4 Klessydra T0 Architecture                                | 26 |

| 4.1.        | The Klessydra-T family                                     | 26 |

| 4.2.        | Motivation for choosing interleaved multithreading         | 26 |

| 4.3.        | Klessydra-T0 introduction and background information       | 27 |

| 4.4.        | Choosing the optimal IMT pipeline organization:            | 29 |

| 4.5.        | Deeper pipeline organizations                              | 33 |

| 4.6.        | The T03 core                                               | 35 |

| 4.7.        | Trap handling                                              | 40 |

| 4.8.        | Thread synchronization.                                    | 44 |

| 4.9.      | Conclusion                                                         | 46  |  |  |  |  |

|-----------|--------------------------------------------------------------------|-----|--|--|--|--|

| Chapter   | 5 Klessydra-T1 Architectures                                       | 47  |  |  |  |  |

| 5.1.      | Background                                                         | 47  |  |  |  |  |

| 5.2.      | Motivation for augmenting the T03 core with a hardware accelerator | 47  |  |  |  |  |

| 5.3.      | Special Purpose Mathematical Unit Microarchitecture                | 48  |  |  |  |  |

| 5.4.      | SPMU Implementations                                               | 63  |  |  |  |  |

| 5.5.      | Performance evaluation of the SPMU implementations.                | 69  |  |  |  |  |

| 5.6.      | Area, Power, and Energy Reports                                    | 78  |  |  |  |  |

| 5.7.      | Further Evaluations (memory test, GCC optimizations)               | 81  |  |  |  |  |

| Chapter   | 6 C Language Software Suite                                        | 83  |  |  |  |  |

| 6.1.      | Instruction level testing:                                         | 83  |  |  |  |  |

| 6.2.      | Convolution tests:                                                 | 86  |  |  |  |  |

| 6.3.      | Supplementary VGG16 libraries                                      | 90  |  |  |  |  |

| Conclusi  | ons                                                                | 92  |  |  |  |  |

| Appendi   | х А                                                                | 94  |  |  |  |  |

| Appendi   | х В1                                                               | L24 |  |  |  |  |

| Glossary  | i <b>lossary</b>                                                   |     |  |  |  |  |

| Bibliogra | 1 <b>phy</b>                                                       | 157 |  |  |  |  |

# List of Figures

| Figure.1.1, Graph depicting Moore's Law that predicted the doubling of the transistors per die every two years                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure.1.2. Typical IoT devices in homes                                                                                                                              |

| Figure.1.3. The bandwidth growth with the frequency growth                                                                                                            |

| Figure.1.4. Coverage area for a set of transmission frequencies                                                                                                       |

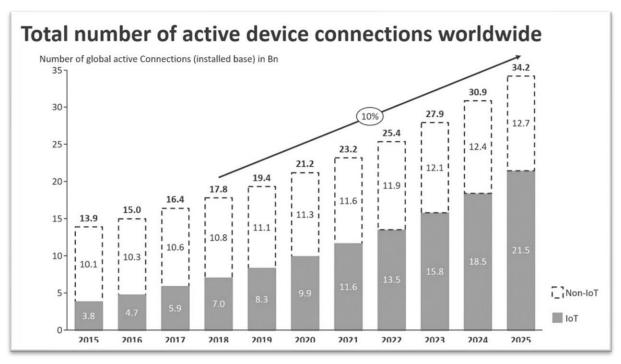

| Figure.1.5. Number of IoT devices to non-IoT and their project growth                                                                                                 |

| Figure.1.6.Typical depiction of an IoT Embedded System                                                                                                                |

| Figure.1.7. Layers in an artificial neural network14                                                                                                                  |

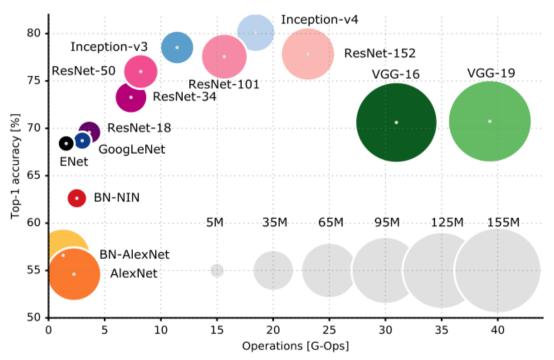

| Figure.1.8. Accuracy versus number of operations single forward pass for a certain class of CNN 15                                                                    |

| Figure.2.1. Base Instruction Formats                                                                                                                                  |

| Figure.3.1. Propagation delay versus power supply voltage                                                                                                             |

| Figure.3.2 Architecture of PULPino                                                                                                                                    |

| Figure.3.3 Klessydra family roadmap25                                                                                                                                 |

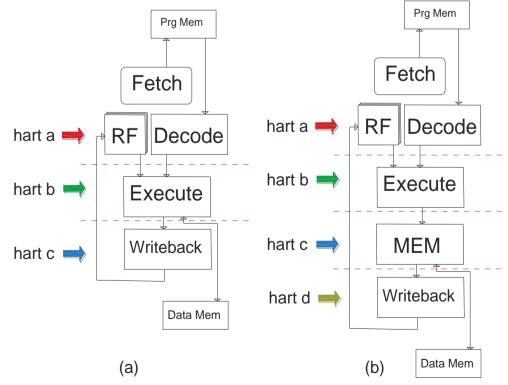

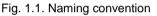

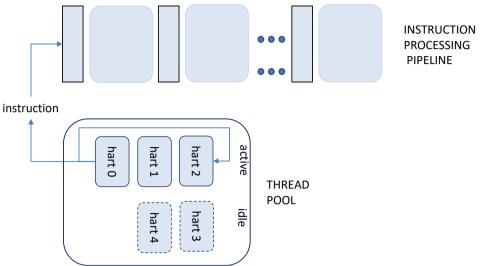

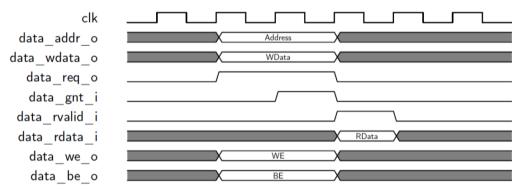

| Figure.4.1. Conceptual view of hardware context counter (harc) interleaved execution                                                                                  |

| Figure.4.2. (a) Klessydra T033 datapath, three harts interleave from RF to WB,                                                                                        |

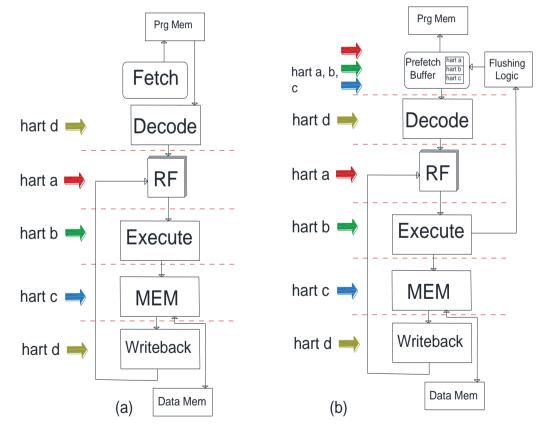

| Figure.4.3 (a) Klessydra T044 datapath five pipeline stage but still works by interleaving only four harts                                                            |

| Figure.4.4 Klessydra T033 block organization, interleaves three harts in the instruction pipeline 35                                                                  |

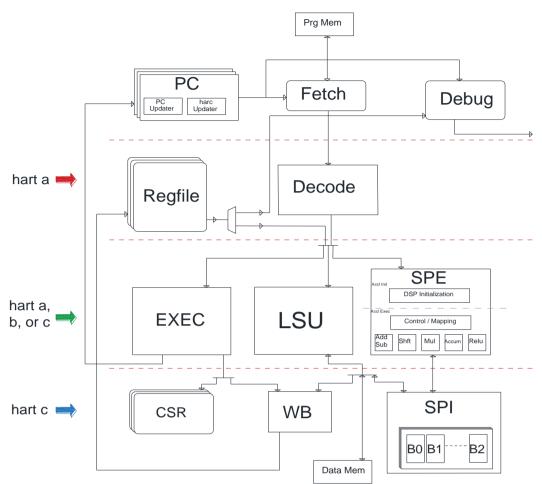

| Figure.5.1. Klessydra T133 block organization, interleaves three harts and has three execution units working in parallel                                              |

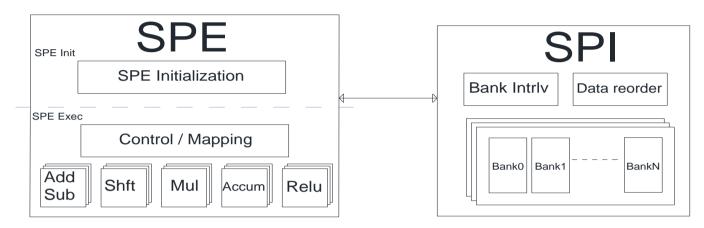

| Figure.5.2. SPMU Block Diagram                                                                                                                                        |

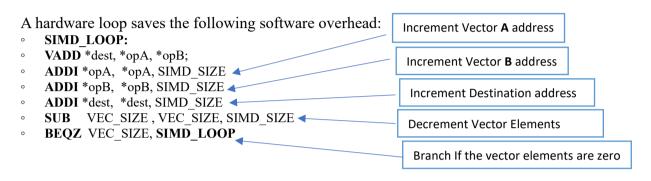

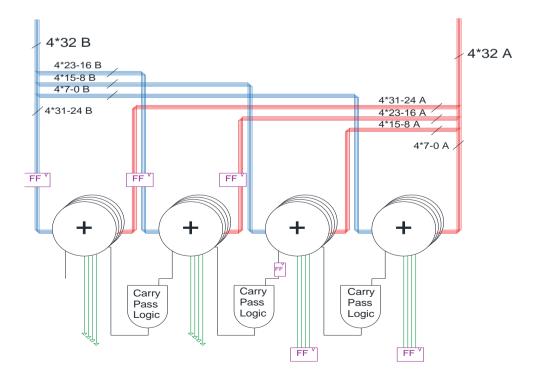

| Figure.5.3. Partial Adder Circuit in SIMD=4                                                                                                                           |

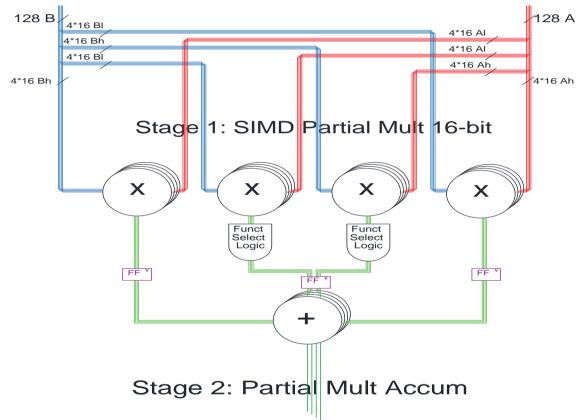

| Figure.5.4. Partial Multiplier Circuit in SIMD=4                                                                                                                      |

| Figure.5.5. Partial Right Shifter Circuit in SIMD=4                                                                                                                   |

| Figure.5.6. Diagram of the Shared-SPMU, all accesses to the SPMU are shared by all the harts64                                                                        |

| Figure.5.7. Diagram of dedicated SPI shared SPE model. Each hart has a dedicated set of scratchpads, busy signals will only block the hart belonging to the same SPMU |

| Figure.5.8. Diagram of Dedicated-SPMU, each hart has a dedicated SPE and SPI, a busy signal will only block the hart belonging to the same SPMU                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

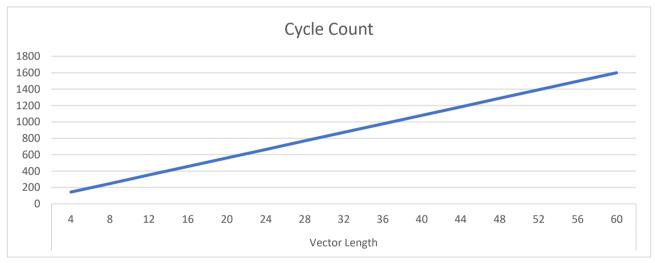

| Figure.5.9. Number of cycles taken to perform an arithmetic vector operation without the SPMU.69                                                               |

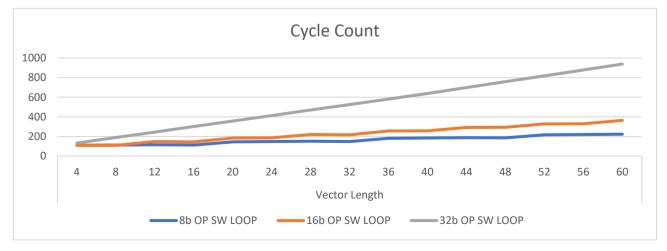

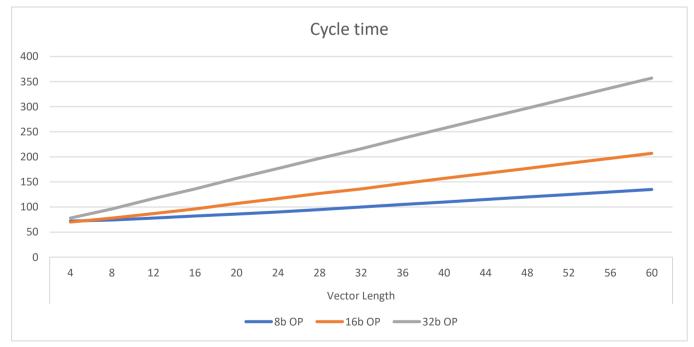

| Figure 5.10. Cycle time using the SPMU with SIMD=1 and hardware loops disabled                                                                                 |

| Figure.5.11. Cycle time using the SPMU with SIMD=1 and hardware loops enabled70                                                                                |

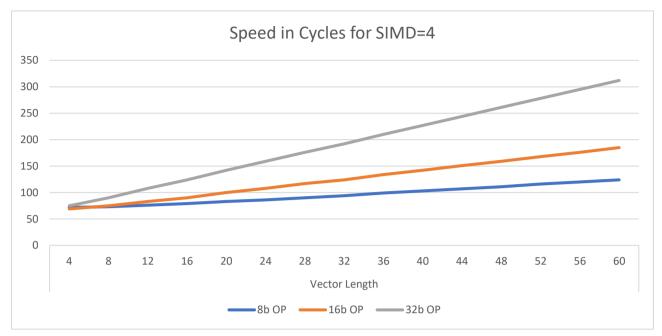

| Figure 5.12. Cycle time using the SPMU with SIMD=4 and hardware loops enabled71                                                                                |

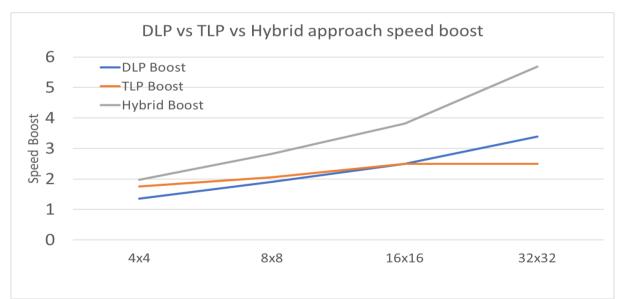

| Figure .5.13. Speed boost from exploiting the DLP, TLP, and both together (Hybrid)                                                                             |

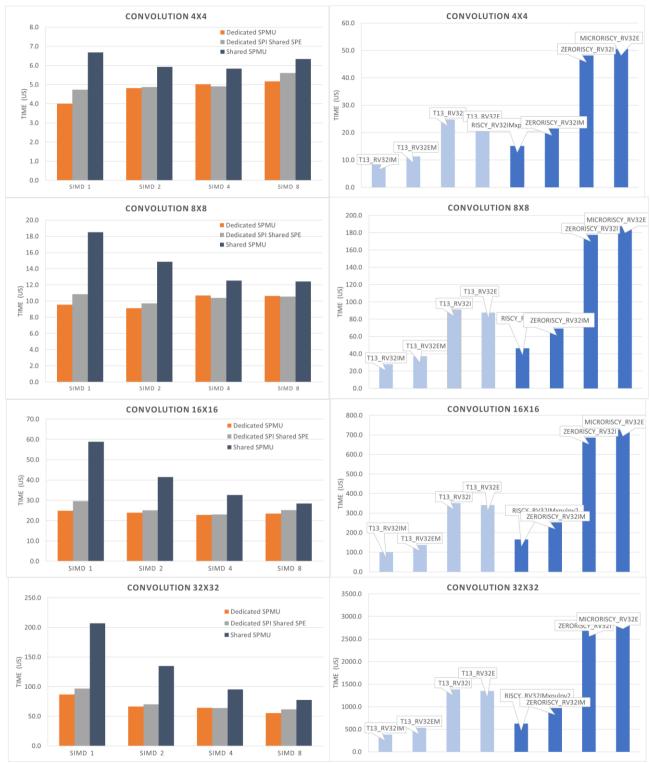

| Figure.5.14. Total execution time to perform convolutions when running at the maximum attainable frequency for accelerated and non-accelerated implementations |

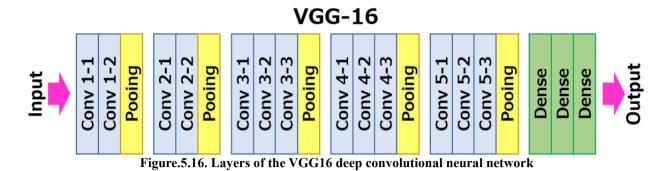

| Figure.5.15. Layers of the VGG16 deep convolutional neural network                                                                                             |

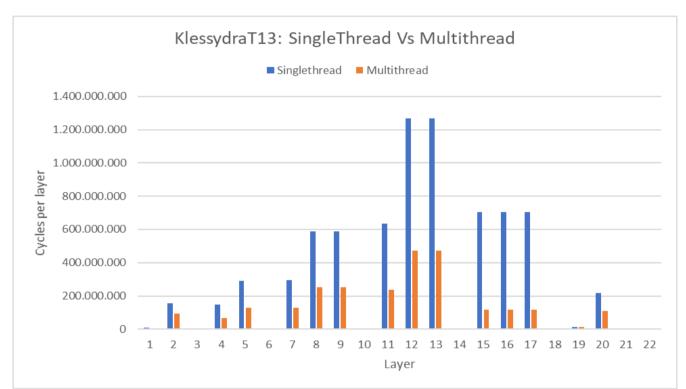

| Figure.5.16. KlessydraT13 Shared-SPMU, Single Thread Vs Multithread cycle count per layer for VGG1677                                                          |

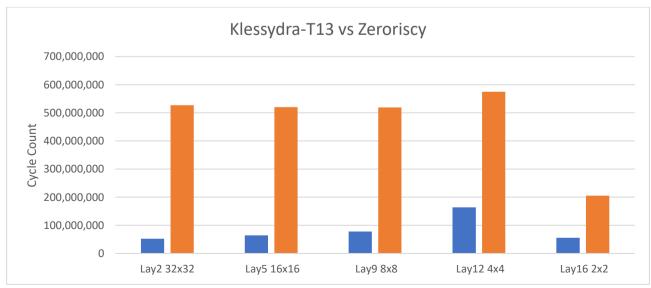

| Figure.5.17. KlessydraT13 Dedicated-SPMU SIMD-2, vs Zeroriscy cycle count per layer for VGG16 execution                                                        |

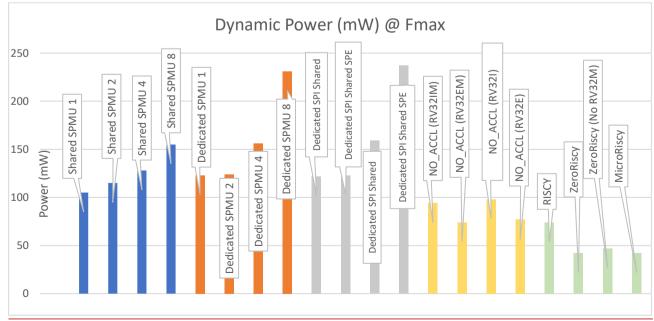

| Figure.5.18. Dynamic Power Consumption of the T13 core running 32x32 convolutions79                                                                            |

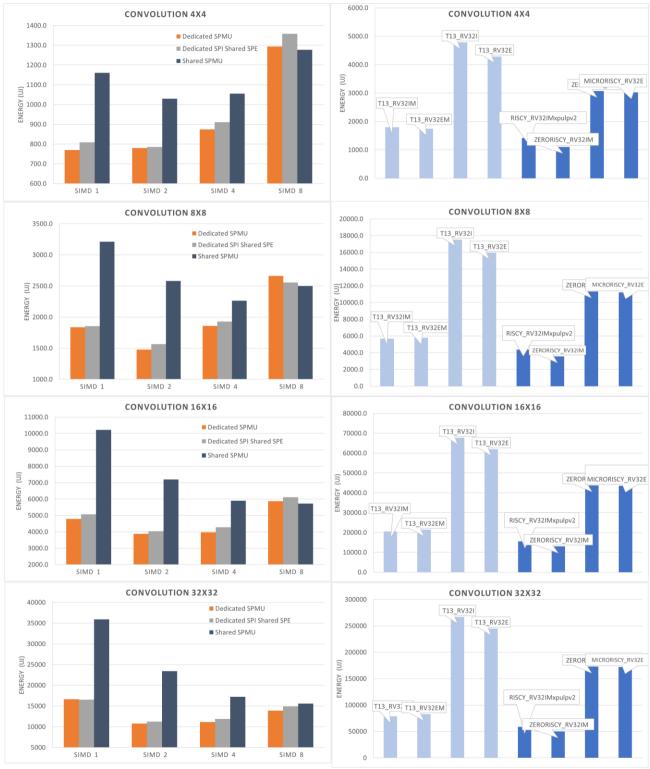

| Figure.5.19. Energy Consumption for running each implementation at the top frequency on the different convolution sizes                                        |

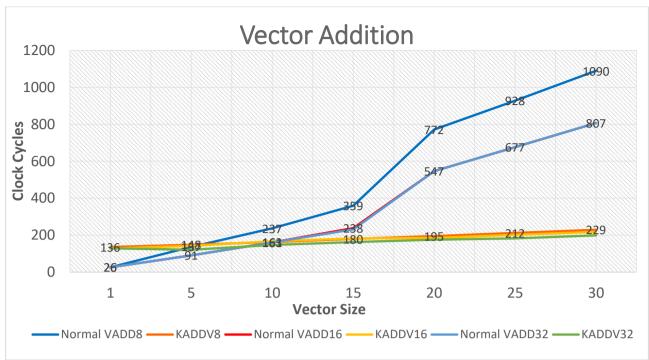

| Figure.5.20. Vector addition C test performed with GCC optimizations disabled                                                                                  |

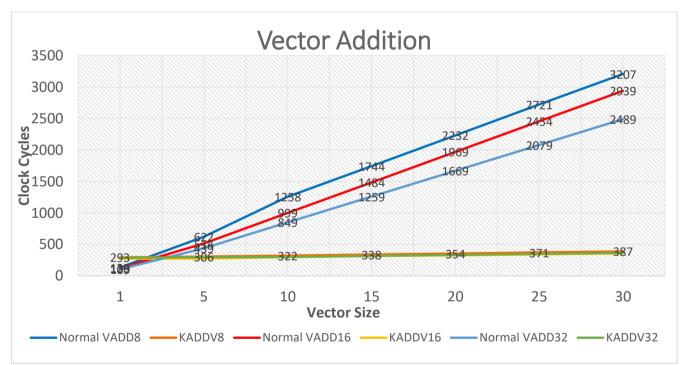

| Figure.5.21. Vector addition C test performed with GCC optimizations enabled                                                                                   |

| Figure.6.1. Convolution of feature map on the left and kernel map on the right           | 87 |

|------------------------------------------------------------------------------------------|----|

| Figure.6.2. Convolution of feature map on the left and kernel map on the right           | 87 |

| Figure.6.3. Division of the sub-kernels. On the left shows the overlap with sub-kernel F | 88 |

| Figure.6.4. Sub-Kernel F executed in the SPMU                                            | 89 |

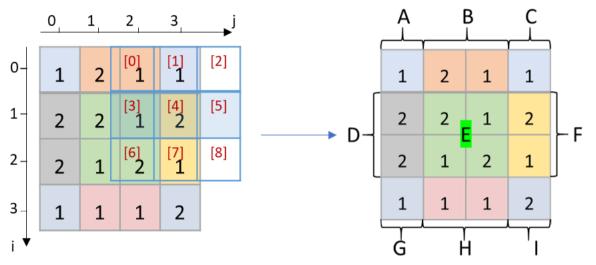

| Figure.6.5. Discrete Kmemlds for zeropadded implementations                              | 89 |

| Figure.6.6. Zero-Padded Convolution method using the SPMU instructions                   | 90 |

## List of Tables

| Table.2. 1 Table.2.1 RISC-V mnemonics for RISC-V integer and floating point registers                     | 17 |

|-----------------------------------------------------------------------------------------------------------|----|

| Table.2.2. RAS stack prediction hints                                                                     | 18 |

| Table.2.3. RISC-V based opcode map, inst[1:0] = 11 i.e. compressed instructions are not include the table |    |

| Table.4.1. Resource Utilization, and Minimum cycle time [ns]                                     | 29 |

|--------------------------------------------------------------------------------------------------|----|

| Table.4.2. Throughput at Maximum Frequency [MIPS] (N.A. = NOT APPLICABLE)                        | 30 |

| Table.4.3. Average Dynamic Power at Maximum Clock Frequency [mW] (N.A. = NOT         APPLICABLE) | 31 |

| Table.4.5. Control and status registers supported by Klessydra cores                             |    |

| Table.5. 1 Type, and parallelism of the functional units in the SPE                | .55 |

|------------------------------------------------------------------------------------|-----|

| Table.5.2. Cycle number to execute a set of convolutions                           | .72 |

| Table.5.3. Top frequency for each T13 configuration and Riscy Cores.               | .72 |

| Table.5.4. T13 Area Utilization on FPGA for all SPMU Configurations                | .78 |

| Table.5.5. Size in Bytes of the program memory and data memory for different tests | .82 |

## Abstract

The number of IoT devices has greatly increased over the years, so that they have invaded the electronic market. IoT describe a device-to-device communication without human interface. A large class of these devices are battery powered, and the energy consumption inside them is considered critical.

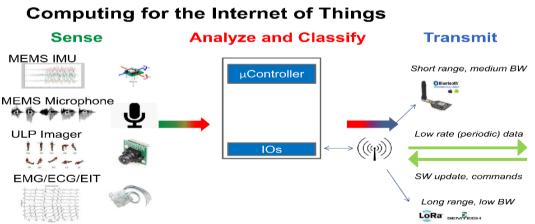

Today's embedded IoT systems interface multiple peripherals such as sensors that perform continuous monitoring of the environment around it, and actuators that are controlled by the embedded systems. Also, they interface wireless devices for data transmissions. A part of their job includes some basic pre-processing of the data before transmitting it over those wireless networks. Such pre-processing "on the edge of the network" minimizes the data to be transmitted over the wireless channels, and only transmits the desired outputs.

In front of the increase demand to support pre-processing, such as computer vision and voice recognition, on small embedded systems on the edge of the network, they cannot completely satisfy those demands due to their little performance

In this study we demonstrate the performance and energy efficiency of interleaved multithreaded architectures, which can be used in an embedded system on the edge of the IoT interfacing multiple sensors and peripherals, each serviced by a different hardware thread. We show the optimal pipeline organization to use in such architectures, and we finally demonstrate how these architectures can be exploited to easily improve instruction level parallelism by integrating a convolutional neural networking accelerator that can perform very fast vector arithmetic operations, and finally benchmarking this accelerator by running a custom implementation of the VGG16 convolutional neural network.

The microprocessors presented are a part of a family of processing cores called *Klessydra*. The Klessydra microprocessors were written such that they have a pinout that are 100 percent identical with Riscy cores from PULPino SoC. The subset of the Klessydra cores presented in this thesis is called the *Klessydra-T*. The letter 'T' indicating that the cores are multithreaded, the Klessydra-T subset has two main implementations used throughout this thesis, they are *Klessydra-T03* and *Klessydra-T13*. *T03* and *T13* for short.

The processor cores have been tested with the Modelsim / Questasim simulators. The cores have been synthesized on the 7-series FPGAs from Xilinx with the Vivado Synthesis tool. Synthesis and Post-synthesis simulations have been made. Dynamic Power estimations were calculated by Vivado from the power report generated by Modelsim after having simulated a post-synthesis Vivado netlist. FPGA synthesis was chosen as our target implementation, as they provide high reconfigurability, which allows the user to easily customize their own accelerator and make it adapt accordingly to their specific applications.

In our assessment throughout this thesis we nominated the T03 interleaved multithreaded processor as our optimal and most balanced pipeline organization. The T03 core had many advantages over other architectures, however it was only suitable to be used in control applications. T13 solves this problem by implementing superscalar hardware accelerators. A hybrid implementation of the hardware accelerator targeting thread level parallelism and slight data level parallelism was the approach yielding the highest performance and still maintaining a relatively low energy consumption for energy critical environments.

### Organization of the Dissertation:

- Chapter 1 This dissertation starts with the preface that provides a brief literature review of IoT devices, and the convergence between cloud computing and embedded systems.

- Chapter 2 The second chapter gives an overview of the RISC-V ISA focusing on the implemented instruction sets in Klessydra-T, and the custom instructions appended to the native RISC-V ISA.

- Chapter 3 The third chapter provides an overview of the PULPino SoC, and describes the modifications made to the Pulpino environment that made it possible for Klessydra to be integrated.

- Chapter 4 The fourth chapter introduces the Klessydra-T0. In this chapter we investigate the optimal pipeline organization to adopt through a series of experimental and analytical studies. Then the building blocks of the Klessydra-T0 will be illustrated, and then we show some basic libraries written to compliment the hardware side with some software code.

- Chapter 5 The fifth chapter introduces the Klessydra-T1, and shows the hardware accelerator added to the T1 core. Then the accelerator is benchmarked when implemented in three different approaches, and we deduce which approach is the most ideal to use. The accelerator is benchmarked with VGG16 DCNN test, and it is shown how it was benchmarked

- Chapter 6 The sixth chapter just shows the software suite of the tests that were used to benchmark the accelerator in chapter 5. They demonstrate how the convolutions were implemented on the accelerator, and a brief display of how the different structures in the VGG16 test were written.

- Conclusion We conclude by summarizing the results presented in chapters four and five.

- Appendix A Contains the Klessydra technical manual detailing the implementation, the ISA support, the architecture, and the CSR instructions in the Klessydra-T cores.

- Appendix B This RTL of the Klessydra-T is here. The T1 and the T0 implementations can be generated from the PKG file, as well as all the configurations detailed in chapter 5.

## **Chapter 1 Preface**

This chapter is a preface to the work being detailed in this study. In the first section we provide a brief introduction on IoT devices and their growth in the current electronic market. In the next section we discuss the artificial neural networks, focusing on the sector of computer vision and convolutional neural networks. In the last section we show the convergence of AI applications from cloud computing to embedded low power IoT devices. Then we discuss the energy efficient digital system developed in this study that target the IoT market, and facilitates the execution of CNNs that are being steadily embedded in IoT devices.

### 1.1. Internet of things

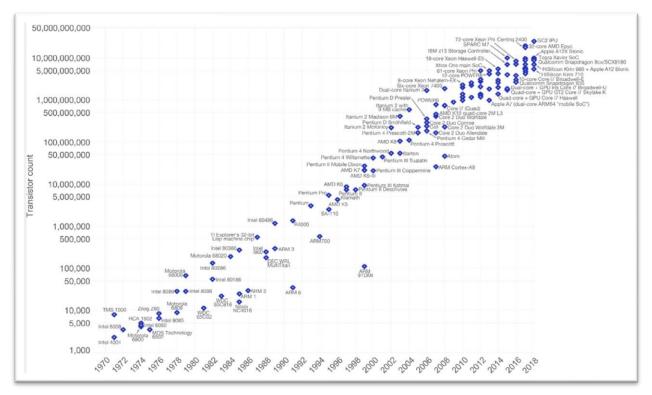

The MOSFET was the main driver for the rise of the Internet of things. The scaling of the MOSFET down to the nanoscale was also followed by the scaling down of the power consumption as well. As of 2019, the smallest MOSFETs in production are 5nm FinFETs manufactured by Samsung and TSMC [1][2]. Gordon Moore observed the shrinking of the transistor and predicted that the number of transistors on an integrated circuit would approximately double every two years (figure 1.1) with the speed doubling every 18 months without increasing the power [3].

Figure.1.1, Graph depicting Moore's Law that predicted the doubling of the transistors per die every two years

However, the world was still farfetched from becoming fully connected. Two main inventions provided the next milestone that facilitated the convergence towards an IoT world, the first was the development of high-performance multi-core processors, and the second was the emergence of high bandwidth wireless technologies.

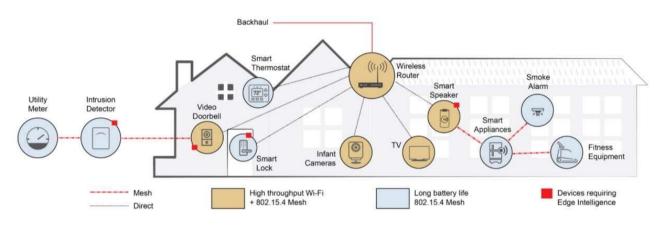

The nanoscale scale parallel microprocessors were capable computing large chunks of data for a very slight energy consumption. This in turn encouraged the incorporation of these smart technologies into all types of electronic devices especially inside battery powered devices (figure 1.2). One main

example for the use of these smart devices other than home automation domains as shown in the figure above was the deployment of smart devices for sensing and monitoring tasks, such as office monitoring, agricultural monitoring, traffic monitoring, defense monitoring, space monitoring, and not to mention even human monitoring through medical devices and wearable technologies. These areas were situated with a handful of sensing instrumentation for temperature, humidity, fire, air pollution, traffic jam, rain wind, storms, etc.) [4].

Figure.1.2. Typical IoT devices in homes

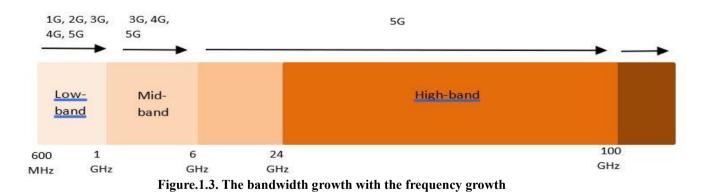

However, these smart devices needed to be accessed over long distances. and this is where the emergence of wireless technologies played a key role in which they were capable of providing a connection between two nodes over large distances. But one main drawback to wireless transmission was that; the larger the distance got between the two nodes; the more transmission power was needed to maintain the nodes connected. Another challenge was the exorbitant increase in the bandwidth over the years, required by certain streaming applications, and in order to provide these large bandwidths, the wireless technologies needed to transmit over higher frequencies in the spectrum as shown in figure 1.3.

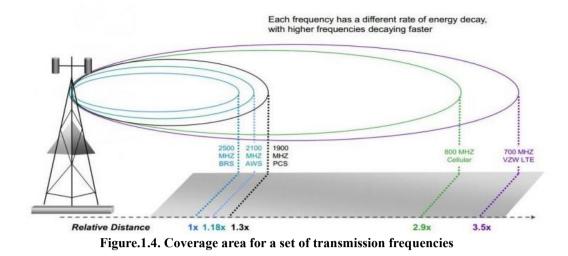

However, the power consumption required to transmit a certain packet of data over a certain distance 'X' is much higher than the power consumption required to transmit the same packet over a lower frequency, and figure 1.3 showed that larger bandwidths broadcasted at higher frequencies. The tradeoff between coverage area and frequency when transmitting over the same frequency is shown in figure 1.4.

Figure 1.4 shows that coverage area for transmitting over the same power (dBm), but different frequency ranges was very different. Such that transmitting over 700MHz covered the 3.5 times the distance for transmitting over 2.5GHz.

The challenge was to accommodate the demand to transmit high bandwidth of data over very large distances, while still maintaining low power consumption. Thus, came the third milestone which was connecting these smart devices to local gateways either through a wire or wirelessly, and the gateways are connected to a global system of interconnected nodes communicating with an open protocol; called TCP/IP otherwise known as the internet.

Providing internet connectivity to smart devices made them capable of transmitting very high data bandwidths over high frequencies to local wireless nodes that are only a few meters away from the transmitter. These communicating nodes are otherwise known as wireless local area networks (WLAN). The WLANs are then connected to the internet and provide access to these smart devices globally. This connection of the various smart devices from over the internet is what is now known as the Internet of Things (IoT).

However, not every device that has IP connectivity is considered IoT. For example, desktops, laptops, cellphones, tablets, game consoles are not considered to be IoT [27]. An IoT device is a network of devices that can communicate without human interactions. In other words, it is a network of things. Figure 1.5 shows the number of IoT devices available till date, and their projected growth over the next five to six years.

IoT encompasses only device-to-device interactions and connectivity. Although human interaction can be present at some endpoint of the IoT network, but all the intermediate device communications are considered IoT. For example, a wearable smart watch interacts with the cellphones over wireless personal area networks (WPAN), and cellular mobile stations through LTE, and connect to GPS systems to provide continuous tracking. All these communications are part of the IoT network, and the final presentation to the human interface would be the non-IoT human factor in this network [27].

Figure.1.5. Number of IoT devices to non-IoT and their project growth

#### 1.2. Energy efficient IoT devices:

Gradual increase in the integration of convolutional neural networks in low power embedded IoT devices by applying image recognition and classification was prevalent in the recent years [5]. IoT devices were able to move AI algorithms from cloud computing down to the edge computing [6]. IoT endpoint SoC refer to a large number of microcontrollers interfacing a various class of sensors on one end, and a wireless device on the other end. The IoT end-nodes might contain specialized units for fast memory access such as scratchpad units [22]. The IoT end-node design demands low-power specialized processors [24][25][26], in which they will be used to collect and pre-processes information from the peripheral devices, and sends the data over the wireless channel (figure 1.6). Preprocessing might include in many cases speech and/or image recognition. This is why we developed a RISC-V processor that can exploit IoT applications which interface multiple peripheral devices, and also, can pre-process images quickly with high performance and energy efficient CNN accelerators.

Figure.1.6. Typical depiction of an IoT Embedded System

### 1.3. Artificial neural networks

#### 1.2.1. Background:

The human brain is a collection of billions of neurons connected to each other through synapses and can pass the signal from one neuron to the next either electrically or chemically. Artificial neural networks although not identical to biological neural networks, however, they were inspired by them. They aimed to loosely imitate the behavior of the brain in order to solve some of the problems the brain does through emulating its learning ability.

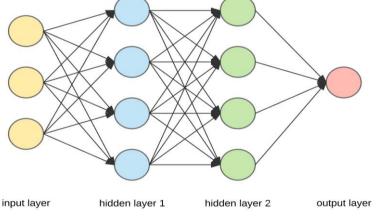

ANNs are a collection of artificial neurons that connect to one another to form a large system of artificial neurons. These systems are an aggregate of layers that are connected to each other, they are capable of learning through continuous feedback loop connections, or through algorithms in single-forward pass networks that modify the weights after the whole operation is done (such as the case in feed-forward networks like convolutional neural networks). During the learning process, the system adjusts the weights which can either strengthen or weaken the connection between the two neurons. Figure 1.7 shows the basic organization of an ANN.

The first layer takes the external data that is known as the input layer, and performs a transformation of these data and sends its output to the next layer. The final layer of the networks is the output layer that infers the final result from all the transformations of the previous layers. Between the input and the output layers, there might exist some intermediate layers also known as hidden layers (figure 1.7).

Figure.1.7. Layers in an artificial neural network

The layers can be fully-connected by having every neuron in layer[i] connect to every other neuron of layer[i+1], or the connections can be pooling by connecting a set of neurons in layer[i] to a single neuron in layer[i+1] thereby reducing the number of neurons in layer[i+1].

#### 1.2.2. Learning in ANN

Learning is a continuous process of adjusting connections between the neurons by modifying the weights, so that the output results will converge towards the correct output after running the network in each iteration. The learning can be considered complete if the error rate ideally becomes zero, or that if each iteration of running the network does not reduce the error rate. In order to try and avoid oscillations of weights inside the neural network during learning, adaptive learning must be implemented to in order to maintain a gradient ascent or descent of the weights.

Final results of the network are mapped into a probability distribution of predicted outputs by using normalizing functions such as *softmax*. However, the actual output might not be the desired output.

The error rate in ANN does not typically reach zero, even after the learning is done. A cost function maps the desired real results to the actual results, and if the error rate determined by the cost function is deemed too high, then the network is basically is not designed very well, and re-designing it must be put into consideration.

#### 1.2.3. Deep Convolutional Neural Networks and Deep Learning

A deep neural network (DNN) is a subset of ANN where there exists a large number of layers between the input the and the output layers. The extra layers in DNN enable the extraction of features from the previous layers. DNN are feedforward in nature. They do not provided feedback to the previous layers, and the adjusting of the weights is done at the end of network after the probability distribution has been calculated.

One of the main fields of DNN is convolutional or deep convolutional neural networks (CNN / DCNN), they are used in computer vision [28], or speech recognition. CNNs are fully-connected networks in which each neuron in one layer connects to all the neurons in the next. CNN employ mathematical convolutions in order to transform the input data into the output. There are a large class of CNN that were developed over the years. Figure 1.8 arranges them in accuracy versus number of operations in a single forward pass. One single forward pass indicates how many operations (G-OPS) are required in order to transform the input data of the network to the output result. The size of the circles indicates the memory footprint of each network.

Figure.1.8. Accuracy versus number of operations single forward pass for a certain class of CNN

## Chapter 2 RISC-V and the Klessydra Processor Family

#### 2.1. Motivation behind adopting RISC-V

The first step in building Klessydra a majorly open source family of processing cores, was through choosing an instruction set. Our choice in that matter considering we are a group of researchers with limited funding was to adopt an open instruction set free from royalties.

Our motivation for adopting the RISC-V instruction set, was basically similar to the motivation of the team from University of California, Berkley when they developed the RISC-V ISA. Which was to make instruction sets free. Another reason encouraged us was that RISC-V was designed to tailor and exploit all types of architectures. In-order, out-of-order, embedded low-power, supercomputers and etc. The third reason was that, RISC-V providing encoding space for custom instructions, helped flourish the research community by allowing students, researchers and industries to test, and experiment their own non-native instruction sets.

Also, comparing both RISC-V and OpenRISC, RISC-V being a more revised and well-studied ISA made the case that they were a better option to adopt than OpenRISC for several reasons, most importantly is that openRISC supports condition codes and branch delay slots which complicate higher performance implementations. Also, OpenRISC supporting fixed sized 16-bit immediates made little encoding space to let the ISA grow.

#### 2.2. Background

RISC-V is an open instruction set architecture, the project was started in 2010 at the University of California, and it still continues to expand the ISA specification till the present day.

The ISA is based on reduced instruction set computing, and it provides two reference manuals. The first being the user-level ISA, and the second being the privileged architecture [7]. The main motivation behind having an open source instruction set, was the availability of the open source Linux operating system, and the open networking protocols TCP/IP [8]. The question came as to why instruction sets cannot be free as well. This motivated the engineers at Berkley to create an ISA being open and royalty free. Commercial ISAs from Intel, ARM, and IBM being proprietary limited the research in computer architectures to those companies themselves. And in order to adopt the standards, one must undergo a rigorous process of negotiations in order to take about six to twenty-four months.

RISC-V till date supported the computer architecture research and education consortium in developing their own proprietary or open-source processors. Currently there are tens of RISC-V implementations, like Rocket, RI5CY, Ariane, Klessydra, BOOM, Taiga, and many more [9]. One of their main future goals is to have the instruction set adopted also in industry implementations.

In the next sections in this chapter we will make a brief summary or the RISC-V instruction sets, then we will discuss one huge advantage provided by RISC-V that enabled researches to innovate even more in the computer architecture domain, by giving more implementation freedom to the user. Finally, we will discuss which architecture and ISA extensions were adopted in the Klessydra-T cores presented in this thesis.

#### 2.3. Instruction set architecture briefing

The RISC-V ISA is the base integer ISA, which must be defined in any implementation. The base integer ISA is the backbone of the entire standard that delivers a minimal set of instructions sufficient to be provided to compilers, linkers, assemblers, and operating systems. The base integer ISA can be implemented for both 32-bit and 64-bit architectures.

The base integer ISA is labeled "I" and is preceded by either one of the following labels. "RV32" or "RV64". It supports 32 general purpose registers from "x0-x31" with "x0" being a read only register hardwired to 0. Table 2.1, shows the application binary interface (ABI) of the integer and floating point registerfiles.

| Register | ABI Name | Description                       | Saver  |

|----------|----------|-----------------------------------|--------|

| x0       | zero     | Hard-wired zero                   |        |

| x1       | ra       | Return address                    | Caller |

| x2       | sp       | Stack pointer                     | Callee |

| xЗ       | gp       | Global pointer                    |        |

| x4       | tp       | Thread pointer                    |        |

| x5       | t0       | Temporary/alternate link register | Caller |

| x6-7     | t1-2     | Temporaries                       | Caller |

| x8       | s0/fp    | Saved register/frame pointer      | Callee |

| x9       | s1       | Saved register                    | Callee |

| x10-11   | a0-1     | Function arguments/return values  | Caller |

| x12–17   | a2–7     | Function arguments                | Caller |

| x18–27   | s2–11    | Saved registers                   | Callee |

| x28-31   | t3-6     | Temporaries                       | Caller |

| f0-7     | ft0-7    | FP temporaries                    | Caller |

| f8-9     | fs0-1    | FP saved registers                | Callee |

| f10-11   | fa0-1    | FP arguments/return values        | Caller |

| f12-17   | fa2-7    | FP arguments                      | Caller |

| f18-27   | fs2-11   | FP saved registers                | Callee |

| f28-31   | ft8-11   | FP temporaries                    | Caller |

Table.2.1. RISC-V mnemonics for RISC-V integer and floating point registers

The return address register "x1" is not hardwired automatically in function calls, but rather jump instruction branching to call environments use register "x1" by default to hold the return address. The stack pointer "x2" is identical to each hardware thread or core, and in RISC-V it always points to the beginning of the stack, and the loads and stores to the stack are relative to the base address (i.e. stack pointer in this case).

The base ISA has four instruction formats, as shown in figure 2.1. All instructions have a fixed length and must be aligned 32-bit aligned.

| 31 25                      | 5 24 20   | ) 19 | 15 14 12 | 2 11 7                    | 7 6    | 0      |

|----------------------------|-----------|------|----------|---------------------------|--------|--------|

| $\mathrm{funct7}$          | rs2       | rs1  | funct3   | rd                        | opcode | R-type |

|                            |           |      |          |                           |        |        |

| imm[11:                    | 0]        | rs1  | funct3   | rd                        | opcode | I-type |

|                            |           |      |          |                           |        |        |

| $\operatorname{imm}[11:5]$ | rs2       | rs1  | funct3   | $\operatorname{imm}[4:0]$ | opcode | S-type |

|                            |           |      |          |                           |        |        |

|                            | imm[31:12 | 2]   |          | rd                        | opcode | U-type |

|                            |           |      |          |                           |        |        |

Figure.2.1. Base Instruction Formats

The source *rs1*, *rs2* and destination *rd* operands always fixed in their positions in order to keep the decoding simple. The immediates are always sign extended except for CSR immediates.

The base ISA is divided into five categories of instructions:

- The **integer computational instructions** have a subset of arithmetic, logic, and shifting operations. That either in majority the I-type or R-type format. LUI/AUIPC use the U-type.

- The **control transfer instructions** have a subset of conditional and unconditional jumps. Conditional jumps are relative to the program counter, and do not link any registers. Unconditional jumps can behave like a *goto* statement if there are no pushes to the return address stack (RAS), or they could behave like function calls, or function returns by pushing and popping to the RAS (Table 2.2).

| rd    | rs1   | rs1=rd | RAS action            |

|-------|-------|--------|-----------------------|

| !link | !link | -      | none                  |

| !link | link  | -      | pop                   |

| link  | !link | -      | $\operatorname{push}$ |

| link  | link  | 0      | push and pop          |

| link  | link  | 1      | push                  |

Table.2.2. RAS stack prediction hints

- The **load and store** instructions get the memory address by adding the base address stored in rs1 to the Immediate in the instruction. Load instructions have the I-immediate, and Store use the S-Immediate. They can fetch/write bytes, half-words, and words.

- The **memory fence** instructions insure that one hart performs its memory access before the other hart by fencing the memory accesses.

- The **control and status instructions** access the CSR registers, and modify the ones that are not read only. A large subset of these are registers used for performance counting.

- The last are **environment call and break points** which transfer the execution to a more privileged environment or to a debugger.

RISC-V supports more extensions that include operations being ubiquitous in the computing world. They include the M-extension for Multiply/Divide, A-extension for Atomic operations that help ensure thread synchronization, and memory region locks, F/D-extension for single and double floating-point instructions, and many more that are still being drafted.

#### 2.4. Custom instruction set extensions

RISC-V has been designed to support extensive customization by providing encoding space for custom-instructions as shown in table 2.3. Any custom implementation is considered to be a part of the *non-standard* extensions. The following table shows the map of the base 7-bit opcode and the spaces reserved for each opcode.

| inst[4:2] | 000    | 001      | 010      | 011      | 100    | 101      | 110               | 111        |

|-----------|--------|----------|----------|----------|--------|----------|-------------------|------------|

| inst[6:5] |        |          |          |          |        |          |                   | (> 32b)    |

| 00        | LOAD   | LOAD-FP  | custom-0 | MISC-MEM | OP-IMM | AUIPC    | OP-IMM-32         | 48b        |

| 01        | STORE  | STORE-FP | custom-1 | AMO      | OP     | LUI      | OP-32             | 64b        |

| 10        | MADD   | MSUB     | NMSUB    | NMADD    | OP-FP  | reserved | custom-2/ $rv128$ | 48b        |

| 11        | BRANCH | JALR     | reserved | JAL      | SYSTEM | reserved | custom- $3/rv128$ | $\geq 80b$ |

Table.2.3. RISC-V based opcode map, inst[1:0] = 11 i.e. compressed instructions are not included in the table

As seen from table 2.3 the are four base opcode spaces reserved for custom instruction extensions: *custom-0, custom-1, custom-2,* and *custom-3.*

#### 2.5. RISC-V support in Klessydra

All Klessydra implementations till date support the "I" base integer instruction set in 32-bit. The introduction of the later multithreaded Klessydra-T0 required at least minimal support of the atomic extensions, by implementing the *AMOSWAP* instruction from the A-extension. The Klessydra-Fx implementation continued to support multithreading thus maintaining the atomic support. Also, the M-extension has been augmented in later releases to provide fast multiplication, especially in the Klessydra-T1 to help execute small vectors quickly in convolutional neural networks.

As for the custom instruction set augmentation, they were included only in the Klessydra-T1, they base opcode encoded for the custom instruction was as follows:

- Custom memory instructions encode the opcode space reserved for "*custom-0*", the opcode[6:0] being "7b'0001011"

- Custom vector arithmetic instructions encode the opcode space for "*custom-1*", the opcode[6:0] being "7b'0101011".

Table 2.4 shows the augmented instructions in Klessydra-T1, and their description will be found in appendix A.

| Name     | Binary format | Assembly syntax       | Opcode   |

|----------|---------------|-----------------------|----------|

| KMEMLD   | R             | kmemld rd, rs1, rs2   | custom-0 |

| KMEMSTR  | R             | kmemstr rd, rs1, rs2  | custom-0 |

| KBCASTLD | R             | kaddv rd, rs1, rs2    | custom-0 |

| KADDV    | R             | kaddv rd, rs1, rs2    | custom-1 |

| KSUBV    | R             | ksubv rd, rs1, rs2    | custom-1 |

| KVMUL    | R             | kvmul rd, rs1, rs2    | custom-1 |

| KVRED    | R             | kvred rd, rs1, rs2    | custom-1 |

| KSVADDSC | R             | ksvaddsc rd, rs1, rs2 | custom-1 |

Table.2.4. Klessydra K custom instruction set extensions

| KSVADDRF | R | ksvaddrf rd, rs1, rs2 | custom-1 |

|----------|---|-----------------------|----------|

| KSVMULSC | R | ksvmulsc rd, rs1, rs2 | custom-1 |

| KSVMULRF | R | ksvmulrf rd, rs1, rs2 | custom-1 |

| KDOTP    | R | kdotp rd, rs1, rs2    | custom-1 |

| KDOTPPS  | R | kdotpps rd, rs1, rs2  | custom-1 |

| KSRLV    | R | ksrlv rd, rs1, rs2    | custom-1 |

| KSRAV    | R | ksrav rd, rs1, rs2    | custom-1 |

| KRELU    | R | krelu rd, rs1, rs2    | custom-1 |

| KBCAST   | R | kbcast rd, rs1        | custom-1 |

| KVCP     | R | kvcp rd, rs1          | custom-1 |

In addition to instructions, also custom CSR registers were added, table 2.5 lists the custom CSR registers.

| Name     | CSR_Addr | TYPE | Reg_Size                    | Description                          |

|----------|----------|------|-----------------------------|--------------------------------------|

| MVSIZE   | 0xBF0    | R/W  | Log <sub>2</sub> (SPM_Size) | Contains the vector size the         |

|          |          |      |                             | maximum being                        |

|          |          |      |                             | the SPM size                         |

| MVTYPE   | 0xBF8    | R/W  | 2-bits                      | Contains the type of data the vector |

|          |          |      |                             | has (8-bit, 16-bit. 32-bit)          |

| MPSCLFAC | 0xBE0    | R/W  | 5-bits                      | Post scaling factor for right shifts |

|          |          |      |                             | (used by kdotpps instruction)        |

Table.2.5. Klessydra K custom CSR extensions

### 2.6. Patches to the riscv-gnu-toolchain:

Two simple modifications were to be made, to the sources in the RISC-V GCC toolchain [35], the first was to "*riscv-opc.c*", where it had all the structures of the RISC-V instruction listings. As seen below:

| 1  | /* Vector Extensions */        |                                                            |

|----|--------------------------------|------------------------------------------------------------|

| 2  | {"kmemld", "I", "d,s,t",       | MATCH_K_MEMLD , MASK_K_MEM , match_opcode, 0 },            |

| 3  | {"kmemstr", "I", "d,s,t",      | MATCH K MEMSTR, MASK K MEM, match opcode, 0 },             |

| 4  | {"kbcastld", "I", "d,s,t",     | MATCH_K_BCASTLD, MASK_K_MEM, match_opcode, 0 },            |

| 5  | {"kaddv", "I", "d,s,t",        | MATCH_K_ADDV, MASK_K_ARITH, match_opcode, 0 },             |

| 6  | {"ksubv", "I", "d,s,t",        | MATCH_K_SUBV, MASK_K_ARITH, match_opcode, 0                |

| 7  | {"kvmul", "I", "d,s,t",        | MATCH_K_VMUL, MASK_K_ARITH, match_opcode, 0 },             |

| 8  | {"kvred", "I", "d,s",          | MATCH_K_VRED, MASK_K_ARITH   MASK_RS2, match_opcode, 0 },  |

| 9  | {"kdotp", "I", "d,s,t",        | MATCH_K_DOTP , MASK_K_ARITH, match_opcode, 0 },            |

| 10 | {"ksvaddsc",   "I",   "d,s,t", | MATCH_K_SVADDSC, MASK_K_ARITH, match_opcode, 0             |

| 11 | {"ksvaddrf",  "I",  "d,s,t",   | MATCH_K_SVADDRF, MASK_K_ARITH, match_opcode, 0 },          |

| 12 | {"ksvmulsc", "I", "d,s,t",     | MATCH_K_SVMULSC, MASK_K_ARITH, match_opcode, 0 },          |

| 13 | {"ksvmulrf", "I", "d,s,t",     | MATCH_K_SVMULRF, MASK_K_ARITH, match_opcode, 0 },          |

| 14 | {"ksrav", "I", "d,s,t",        | MATCH_K_SRAV, MASK_K_ARITH, match_opcode, 0 },             |

| 15 | {"ksrlv", "I", "d,s,t",        | MATCH_K_SRLV, MASK_K_ARITH, match_opcode, 0 },             |

| 16 | {"kbcast", "I", "d,s",         | MATCH_K_BCAST, MASK_K_ARITH   MASK_RS2, match_opcode, 0 }, |

| 17 | {"krelu", "I", "d,s",          | MATCH_K_RELU, MASK_K_ARITH   MASK_RS2, match_opcode, 0 },  |

| 18 | {"kdotpps", "I", "d,s,t",      | MATCH_K_DOTPPS, MASK_K_ARITH, match_opcode, 0 },           |

| 19 | {"kvcp", "I", "d,s",           | MATCH_K_VCP, MASK_K_ARITH   MASK_RS2, match_opcode, 0 },   |

The second modification was made to the "riscv-opc.h", where all the defines were made that include the instruction mask and instruction opcode, as well as the CSR defines.

| /* Klessydra Extensions */             |

|----------------------------------------|

| /* CSR Extensions */                   |

| #define CSR MVSIZE 0xbf0               |

| #define CSR_MVTYPE 0xbf8               |

| #define CSR_MPSCLFAC 0xbe0             |

| _                                      |

| /* Vector Instructions Extensions */   |

| #define MASK K MEM 0xfe00707f          |

| #define MATCH $\overline{K}$ MEMLD 0xb |

| #define MATCH_K_MEMSTR 0x200000b       |

| #define MATCH_K_BCASTLD 0x400000b      |

| #define MASK K ARITH 0xfe00707f        |

| #define MATCH K ADDV 0x200202b         |

| #define MATCH_K_SUBV 0x400202b         |

| #define MATCH_K_VMUL 0x800202b         |

| #define MATCH_K_VRED 0xC00202b         |

| #define MATCH_K_DOTP 0x1000202b        |

| #define MATCH_K_SVADDSC 0x1800202b     |

| #define MATCH_K_SVADDRF 0x1a00202b     |

| #define MATCH_K_SVMULSC 0x1c00202b     |

| #define MATCH_K_SVMULRF 0x1e00202b     |

| #define MATCH_K_SRAV 0x2000202b        |

| #define MATCH_K_SRLV 0x2200202b        |

| #define MATCH_K_RELU 0x3000202b        |

| #define MATCH_K_DOTPPS 0x3200202b      |

| #define MATCH_K_BCAST 0x3c00202b       |

| #define MATCH_K_VCP 0x3e00002b         |

|                                        |

| 1  | DECLARE_CSR(mvsize, CSR_MVSIZE)                       |

|----|-------------------------------------------------------|

| 2  | DECLARE_CSR(mvtype, CSR_MVTYPE)                       |

| 3  | DECLARE_CSR(mpsclfac, CSR_MPSCLFAC)                   |

| 4  |                                                       |

| 5  | DECLARE_INSN(kmemld, MATCH_K_MEMLD, MASK_K_MEM)       |

| 6  | DECLARE_INSN(kmemstr, MATCH_K_MEMSTR, MASK_K_MEM)     |

| 7  | DECLARE_INSN(kbcastld, MATCH_K_BCASTLD, MASK_K_MEM)   |

| 8  | DECLARE_INSN(kaddv, MATCH_K_ADDV, MASK_K_ARITH)       |

| 9  | DECLARE_INSN(ksubv, MATCH_K_SUBV, MASK_K_ARITH)       |

| 10 | DECLARE_INSN(kvmul, MATCH_K_VMUL, MASK_K_ARITH)       |

| 11 | DECLARE_INSN(kvred, MATCH_K_VRED, MASK_K_ARITH)       |

| 12 | DECLARE_INSN(kdotp, MATCH_K_DOTP, MASK_K_ARITH)       |

| 13 | DECLARE_INSN(ksvaddsc, MATCH_K_SVADDSC, MASK_K_ARITH) |

| 14 | DECLARE_INSN(ksvaddrf, MATCH_K_SVADDRF, MASK_K_ARITH) |

| 15 | DECLARE_INSN(ksvmulsc, MATCH_K_SVMULSC, MASK_K_ARITH) |

| 16 | DECLARE_INSN(ksvmulrf, MATCH_K_SVMULRF, MASK_K_ARITH) |

| 17 | DECLARE_INSN(ksrav, MATCH_K_SRAV, MASK_K_ARITH)       |

| 18 | DECLARE_INSN(ksrlv, MATCH_K_SRLV, MASK_K_ARITH)       |

| 19 | DECLARE_INSN(krelu, MATCH_K_RELU, MASK_K_ARITH)       |

| 20 | DECLARE_INSN(kdotpps, MATCH_K_DOTPPS, MASK_K_ARITH)   |

| 21 | DECLARE_INSN(kbcast, MATCH_K_BCAST, MASK_K_ARITH)     |

| 22 | DECLARE_INSN(kvcp, MATCH_K_VCP, MASK_K_ARITH)         |

### 2.7. Concluding remarks

In the end RISC-V is not only an open source ISA available for simulations, it is a real ISA suitable for inherent hardware implementations. The standards were provided to be balanced to be exploited by all types of architectures. It supports 32 and 64-bit address space and IEEE standard floating-point standards, it provides custom instruction encoding space to allow researchers to explore native non-standard custom extensions, or companies to integrate their own specialized instructions and finally it still has a great potential to become even more pervasive throughout the industry.

## Chapter 3 The PULPino Microcontroller Platform

#### 3.1. Motivation behind choosing PULPino

Having already chosen to build a RISC-V processor required also choosing a SoC. Designing our own SoC from scratch was not feasible since our group of researchers were limited. RISC-V being an emerging technology, the choices among the open SoCs available were not many. Pulpino being part of the ultra-low power projects also was a good reason to adopt the Systen. Finally, having close relations and collaborations with the University of Bologna, provided an ongoing communication channel in order to get continuous support from their side. For the above reasons, we can say that Pulpino was our choice.

Pulpino is an open-source System-on-Chip embedding a 32-bit RISC-V based microprocessor. Pulpino targets embedded systems and embeds ultra-low power designs. The Pulpino SoC was adopted by a large group of researchers globally either for research or commercial purposes.

#### 3.2. Background

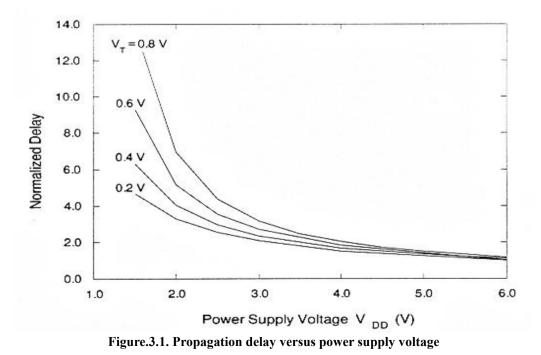

PULPino is a smaller version of PULP which stands for Parallel Ultra Low Power processor. The idea behind starting the PULP project, was that in order to achieve low dynamic power consumption, the processors needed to be operated at near threshold voltage levels [10]. The speed will drop rapidly when operating at near threshold voltages since the delay follows a quadratic curve (figure 3.1). Their solution was to re-ramp up the speed by embedding several processors in PULP to work in parallel.

PULP is a large project with a very wide scope of work, it incorporates a large group of engineers, and specialized experts. The project includes open source processors, peripherals, communication buses, an integrated all-in-one environment to build and test the embedded cores with Modelsim and Vivado and the entire SoC, also adds a custom RISC-V toolchain.

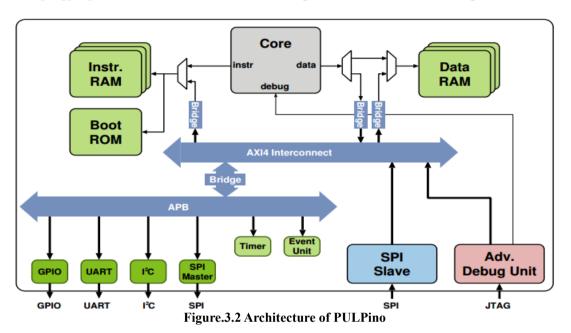

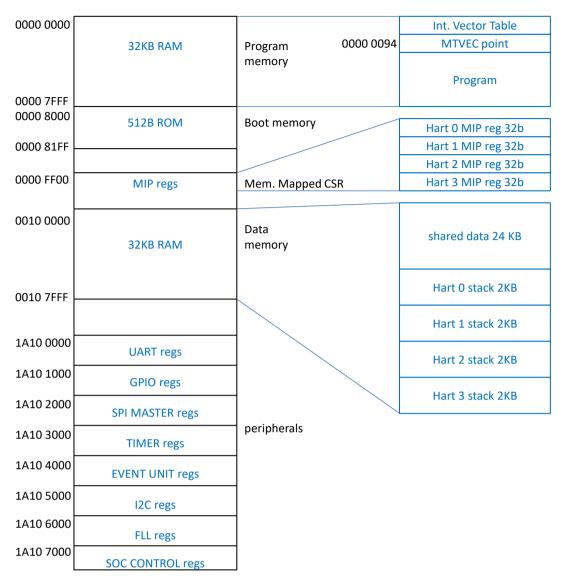

PULPino is a miniaturized version of PULP which embeds only one core. PULPino is completely open source[17][18], and can be found on GitHub. Figure 3.2 shows the building blocks of PULPino.

Pulpino targets RTL simulations, FPGAs, and ASICs. It has by default a 32KB program memory, and a 32KB data memory. The boot ROM is 512B. Peripherals are mapped in the upper region of the core and are dedicated 4KB each. The peripherals in Pulpino communicate through sending interrupts. All the interrupts are saved in an interrupt vector table (IVT). When servicing the interrupt, the core will check the IVT in order to jump to the appropriate interrupt handling routine.

Other than the Peripherals, it features an SPI Slave port that can be used to pre-load programs into the memories without the help of the core. It is connected on the AXI as an AXI master which allows external access to all memories and peripherals. Also, Pulpino has a JTAG debugging interface that accesses all peripherals and memories, and can halt and single step the core.

#### 3.3. PULPino native processor cores

Pulpino integrates two RISC-V processors. They are RI5CY and Zero-Riscy. RI5CY is an in order four pipeline stage processors. It supports the base integer instruction set RV32I, compressed instructions RV32C, multiplication extension RV32M, and single precision floating point extensions RV32F. RI5CY also implements other extensions to the ISA such as hardware loops, bit manipulation instructions, MAC operations, packed SIMD instructions and many more [52][53].

Zero-Riscy is an in-order, single-issue processor with only two pipeline stages. It supports the base integer instruction set RV32I, the compressed instructions RV32C, and the multiplication extension RV32M. The core can be configured to support the embedded extension RV32E, and thus reducing the registerfile to half its size. A tiny version of zero-riscy can be implemented by enabling the

embedded extension (RV32E), and disabling the multipliers and dividers (RV32M). This implementation is called Micro-Riscy which is the smallest version supported.

### 3.4. Embedding non-native Klessydra processing cores in PULPino

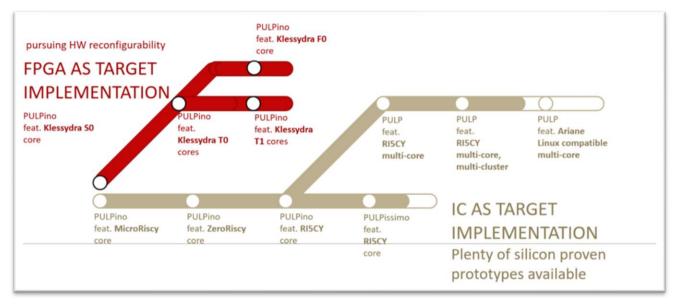

Figure 3.3 shows the Klessydra and Pulpino Roadmap. Klessydra targeting FPGA implementations, while Riscy cores targeting ASIC implementations.

Figure.3.3 Klessydra family roadmap

In order to correctly embed Klessydra core and software libraries inside Pulpino, changes had to be made to the Pulpino environment on many levels:

- **Modifying the Klessydra RTL:** The pinout of the Klessydra was made one hundred percent compatible with the riscy cores from Pulpino. Also, the interrupt handling, and exception, and event handling had to be modified so that it passes the generic tests.

- **Modifying the Pulpino RTL:** The system verilog of the Pulpino RTL and testbench were modified to add the instances of Klessydra cores, and pass the added generic parameter.

- **Modifying the Software Environment:** The CMake files were modified to include the generic Klessydra tests and software libraries. Also, they were modified along with a shell script in order to pass the arguments to the Tcl simulate scripts.

- **Modifying the Modelsim compile and Simulate scripts:** In addition to the software environment and RTL, compile scripts were also modified to compile the different versions of Klessydra among the compiled Pulpino libraries, and similarly the simulate scripts.

## Chapter-4 Klessydra TO Architecture

### 4.1. The Klessydra-T family

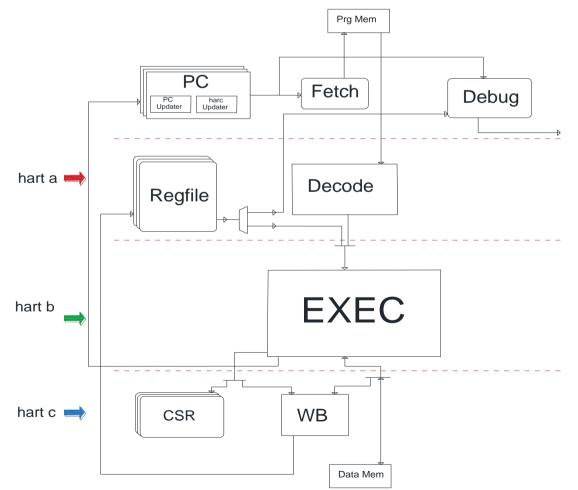

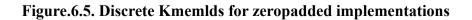

Klessydra is a processing core family that features full compliance with the RISC-V instruction set. Klessydra cores were designed in order to be fitted inside the PULPino SoC. The Klessydra family is composed of a single in-order two pipeline-stage core named Klessydra-S0 [11], a set of multithreaded cores named Klessydra-Tx, and a set of fault tolerant cores named Klessydra-Fx [20][21]. This thesus will cover the Klessydra-Tx family and its different variants. All the Tx cores have been synthesized and tested for FPGAs from XILINX. FPGA synthesis being our main target, was because soft-cores are wildly available on embedded systems [11]. A customizable embedded core is favorable since it can be reconfigured to adapt easily to the user's target applications.

Klessydra cores support RISC-V ISA, all versions support the base integer instruction set in 32-bit |"RV32I" in bare metal, the *Tx* and *Fx* versions extend the ISA with the atomic instruction extension, some *Tx* variants further extend the ISA with multiplication and division extension from RISC-V, and some augment a set of specialized custom instructions augmented to the RISC-V ISA designed to accelerate convolutional neural networking applications. The ports of the Klessydra cores are pin-topin compatible with the RISCY cores inside PULPino. The Tx versions of Klessydra support a multithreading paradigm called interleaved multithreading (IMT) also known as barrel processing. This chapter illustrates the early version of the Tx cores known as the T0 cores, and the different variants of the T0 cores. Chapter 5 upgrades the optimal T0 implementation adopted in this chapter and adds a specialized neural network accelerator that is specifically designed to exploit the IMT architectures. The upgraded version is known as the T1 core.

### 4.2. Motivation for choosing interleaved multithreading

A good guideline to follow in order to increase the energy consumption per instruction of an embedded processor, is through decreasing the idle time of the embedded systems by eliminating the pipeline stalls.

In-order architectures stall the processor's pipeline to fence between same-operand read and write access. These stalls are unfavorable as they degrade the performance of the processor, as well as decrease the energy efficiency by continuously accumulating the total idle time of the processor.

Out-of-order architectures can easily eliminate the pipeline stalls [49][50][51], however in order to do that, they employ highly complex dynamic scheduling logic to resolve the data dependency hazards. These data dependency eliminating schemes give rise to anti-dependency hazards, and again out-of-order architectures employ register renaming approaches to remove those anti-dependencies. In addition, these architectures being highly pipelined must integrate a well-advanced branch predicting logic, since branch miss prediction will greatly impact the overall performance. This type of architecture succeeded in greatly mitigating the pipeline stalls and improves the overall performance. However, these designs being very complex greatly increased the area and the power

consumption of those architectures. In other words, the performance was actually a tradeoff with the power and area.

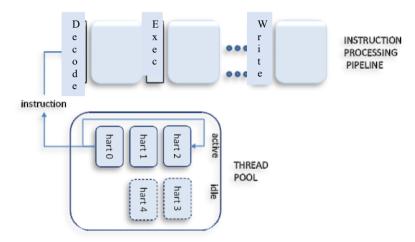

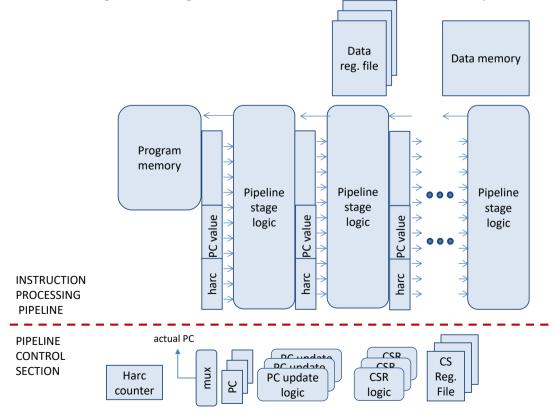

One existing approach named barrel processing or interleaved multithreading (IMT) [16] aimed at replacing the out-of-order processor's highly complex approach to mitigate the pipeline stalls with another relaxed approach. That is by employing hardware threads to utilize the idle time of the core and fence between the registerfile read and write accesses.

An IMT architecture interleaves a hardware thread (hart) to fill the bubbles in the instruction pipeline in order to avoid Read-after-Write (RAW) data hazards. Doing so, it does not introduce a new class of anti-dependency hazards such as Write-after-Read (WAR) and Write-after-Write (WAW) as in the case of *OOO* architectures.

A basic IMT processors emulates a single-core single-issue processor with zero pipeline stalls. IMT processors with their ability to continuously issues instructions without data dependency stalls can converge easily towards 1 IPC in single issue processors, bit for a certain class of applications. The first class being decoupled sequential applications, and the second being balanced parallel applications. Regarding sequential applications, if the IMT processor was running in a way such that the programs are executing only on one hart and the other harts are idle, the overall performance will surely suffer from the overhead of the interleaving the other harts in the core, and the bigger the number of harts an IMT core has, the worse it performs when executing sequential program. Such that the inputs data of one hart are completely independent from the output results of another hart. Such applications might include for example a microcontroller interfacing multiple sensors, and monitoring the changes, then transmitting the data over a wireless channel in order to be interacted by a human interface.

As for the second class of applications easily exploitable by IMT processors, one might quickly deduce that an IMT architecture can perform well in applications with parallel workloads. Although that is partly true, however, the evaluation of how an IMT core performs when running a parallel application is mainly dependent on how balanced the divided workload is between the harts. A balanced workload in a parallel program can have inter-thread dependencies that require thread synchronization; however, the nature of the workload being balanced makes the overhead of thread synchronization unnoticeable. If the parallel applications are balanced and loosely coupled, they will perform better than a balanced workload with tightly coupled applications. Such application classes are very much suitable for IMT architectures since they utilize all the interleaving harts very efficiently. There are many examples of such applications like; data sorting, searching algorithms, Monte-Carlo simulations, computational fluid dynamics (CFD) simulations, molecular modeling and simulations.

### 4.3. Klessydra-TO introduction and background information

The Klessydra-T0 core is a basic IMT microprocessor which supports the RV32IMA instruction set extensions of RISC-V in bare metal. The 'T' symbol indicates that the core architecture is multithreaded. The multithreading paradigm supported is Interleaved Multithreading or IMT. The Klessydra-T0 can be parametrized to run without the M-extension, and also the registerfiles can also be parametrized to support the Embedded E-extension instead for area critical environments. Throughout this chapter, I will refer to the core as "T0" as an abbreviation to the name Klessydra-T0.

The T0 IMT is a single-issue in-order processor which is available in different variants, and the variants each of which has a different instruction pipeline organization, and they are designated by

the following abbreviation: "*T0ab*". Where the letter 'a' following the zero is the identifier for the minimum number of hardware threads needed to be interleaved in a core in order to avoid inserting any bubbles in the pipeline and this is known as the *thread pool baseline*. The 'b' identifier is to indicate the number of harts present in the current version of the core or otherwise known as *thread pool size*.

In order to build an IMT architecture, the following entities must be replicated for each hart:

- Registerfile

- Program Counter

- CSR Unit

After having replicated the above units, a hardware context counter "harc" must be built. The harc interleaves between the harts in the IMT core, such that on every instruction grant, we send to the program memory a request from another hart.

Figure.4.1. Conceptual view of hardware context counter (harc) interleaved execution

Klessydra-Tx cores have a parameterizable number of harts to interleave where the hart count is identified in the package file by a parameter called "THREAD\_POOL\_SIZE". The recommended number of harts to put in a core should be less than or equal to the thread pool baseline. In other words, *T0ab* is recommended to be configured such that 'b' is less than or equal to 'a'.

Configuring 'b' to be greater than 'a' is allowed, however, it will not give any performance boosts, rather it will significantly slow down the performance when running sequential applications. And running parallel applications as well degrade the performance by augmenting bigger stall overheads from idle harts, that will remain idle until all the other harts would have arrived at a thread synchronization barrier. Not to mention the area of the architecture will grow bigger, and as the layouts grow bigger, the elements in the FPGA selected during place and route will be placed ever so farther away from each other, which in turn will yield slower layouts resulted from larger net-delays between the FPGA element slices.

In order to know the minimum thread baseline needed so that no data hazards arise, we have to know how many pipeline stages exist from the read port of the registerfile till the write port of the registerfile. For every pipeline stage separating the read and write ports, a hart must be interleaved, else the user can choose to configure the core to have a hart count less than the minimum baseline and NOP operations will be introduced in the pipeline to fence between instructions belonging to the same hart.

### 4.4. Choosing the optimal IMT pipeline organization:

In this section, we will demonstrate the framework that followed in choosing the optimal pipeline organization to use in interleaved multithreaded processors [15]. In the end of the section we will show which *T0ab* organization was chosen as the most ideal processor to use in our research. This section is oriented around three main keywords:

- **TPS** or Thread pool size, which indicates the total number hardware threads in the core.

- **TPB** or Thread pool baseline that indicates the minimum number of harts needed to avoid data dependency stalls.

- NT or Number of active threads, which indicates the number of active harts M, in a core with a TPS equal to N, such that always: .

The exploration parameters of IMT architectures was first studied by implementing a set of pipeline organizations ranging from two stages to four stage [14]. each being run with a different set of thread pool sizes. The pipeline implementations studied were as follows:

- a. F / RDEW (two pipeline stages)

- b. F / R / DEW (three pipeline stages)

- c. F / RD / EW (three pipeline stages)

- d. F / RD / E / W (four pipeline stages)

- e. F / R / DE / W (four pipeline stages)

In the pipeline schemes listed above, F designates the instruction fetch stage, R is the registerfile reading, D is decoding, E is executing, and W is registerfile writeback. Early T0 versions included a fetch stage, and flushing logic to discard instruction of the same hart in the fetch when a branch is taken. However, later releases ignored the stage and the incoming instruction goes directly to the decode unit. The requested instruction goes directly to the stage after the F. These pipeline structures were designed to study the optimal pipeline organization to use in an interleaved multithreaded bare metal RISC-V processor. Synthesis runs were done on XILINX 7 Series FPGAs [3]. The synthesis timing constraints were set low to make the Vivado compiler generate fast netlists.

The FPGA element utilization from the synthesis runs of the set of configurations is shown in table 4.1. As well as the minimum cycle time of each layout. For instance, *T012* architecture has a TPS of 2 and thread pool baseline of 1.

| Architecture   | TPS | Codename | LUT  | LUT FF |      |

|----------------|-----|----------|------|--------|------|

|                | 2   | T012     | 3264 | 2410   | 12.7 |

| F / RDEW       | 3   | T013     | 4018 | 3577   | 13.9 |

|                | 4   | T014     | 4351 | 4744   | 15.9 |

|                | 2   | T022     | 3211 | 2544   | 8.9  |

| F/R/DEW        | 3   | T023     | 3892 | 3711   | 9.7  |

|                | 4   | T024     | 4217 | 4882   | 9.5  |

|                | 2   | T022_v2  | 3583 | 2653   | 9.6  |

| F/RD/EW        | 3   | T023_v2  | 4461 | 3853   | 9.6  |

|                | 4   | T024_v2  | 4608 | 5052   | 9.4  |

|                | 2   | T032     | 3242 | 2679   | 8.6  |

| F / R / DE / W | 3   | T033     | 4011 | 3914   | 8.9  |

|                | 4   | T034     | 4187 | 5144   | 8.6  |

| F / RD / E / W | 2   | T032_v2  | 3635 | 2725   | 7.1  |

| Table.4.1. Resource Utilization, and Minimum cycle time [ns | 1 |

|-------------------------------------------------------------|---|

|-------------------------------------------------------------|---|

| 3 | T033_v2 | 4520 | 3958 | 7.3 |

|---|---------|------|------|-----|

| 4 | T034_v2 | 4825 | 5189 | 7.4 |

It is evident from table 4.1 that every increment of a hart (TPS) in the core, increased the number of flip-flops count by more than 1024 (32\*32) registers. And every pipeline stage introduced increased the flip-flop count by 100~200 or 5% to 7%. For example, going from the pipeline organization T012 to T022 revealed only a 5% increase in the total flip-flop count and a slight decrease in the total LUT count, and going from the T023\_v2 organization to T033\_v2 increased the flip-flop count by 6% and the LUT count by 1%.

The cycle time of each organization is also shown in table 4.1. One concern we had was that the overhead of the interleaving new harts would increase the area utilization in the FPGA such that during the post-synthesis place and route phase, Vivado would place the elements very far away from each other, making the net delay of the critical path a lot bigger. However, the Vivado timing reports [48] only showed evidence to that situation happening in the *F/RDEW* pipeline organization where the cycle time increased from 12.7ns in the T012 to 13.9ns in the T013, and up to 15.9ns in the T014. However, we don't care about these implementations, since they were only control configurations used for comparative purposes to the other T0 pipeline organizations.

Looking at the other implementations shows only little cycle time increase due to interleaving more harts, and more significant cycle time decrease due to pipelining which is good. Hence, we conclude from the timing report that the increase overhead of adding a new hart to resolve the data dependency problems does not really impact the cycle time, and that with every pipeline the maximum frequency of the core keeps on increasing, such that the cycle time demonstrated a sharp drop from 12.7ns in the T012 down to 7.4ns in the T034 v2.

The throughput of an IMT processor running an integer arithmetic application at maximum frequency is shown in table 4.2. The table shows the number of MIPS for each TPS configuration in every pipeline organization, when the active number of threads NT is less than or equal to the TPS.

- When , the number of MIPS suffers from data dependencies and pipeline flushes.

- When, the number of MIPS will suffer only due to pipeline flushes.

- When , the number of MIPS will not suffer from any pipeline flushes, and data dependency stalls. However, the MIPS will also not increase with the further increase of NT.

| Table.4.2. Throughput at Maximum Frequency [MIPS] (N.A. = NOT APPLICABLE) |     |     |            |                             |      |       |       |  |

|---------------------------------------------------------------------------|-----|-----|------------|-----------------------------|------|-------|-------|--|

| A 1 .                                                                     | TDC | TDD | <b>C</b> 1 | Number of Active threads NT |      |       |       |  |

| Architecture                                                              | TPS | TPB | Codename   | NT=1                        | NT=2 | NT=3  | NT=4  |  |

|                                                                           | 2   |     | T012       | 67.9                        | 78.8 | n.a.  | n.a.  |  |

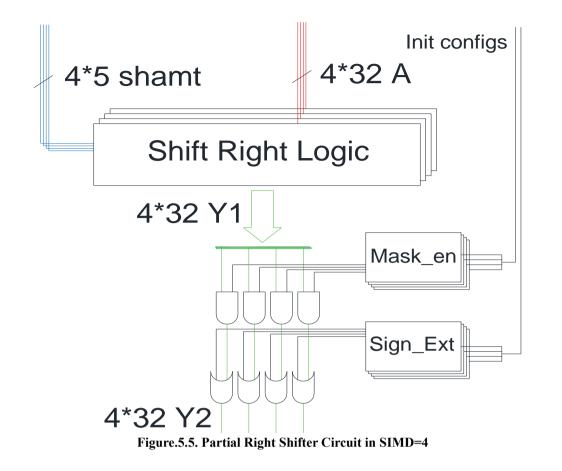

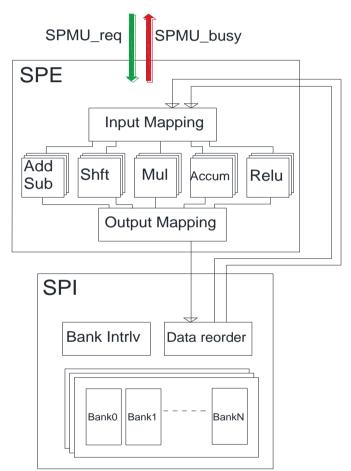

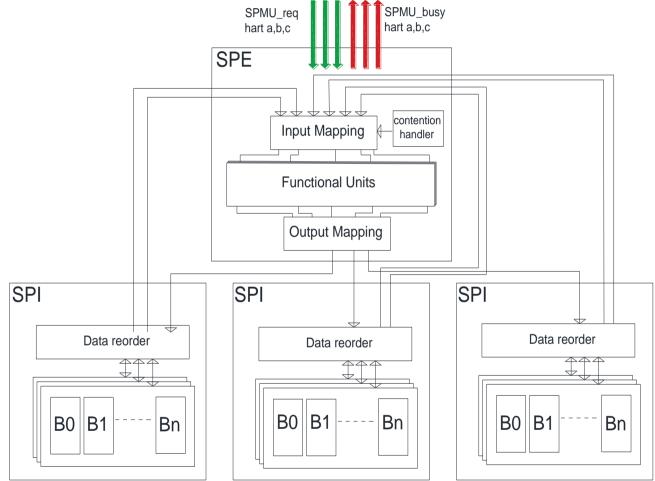

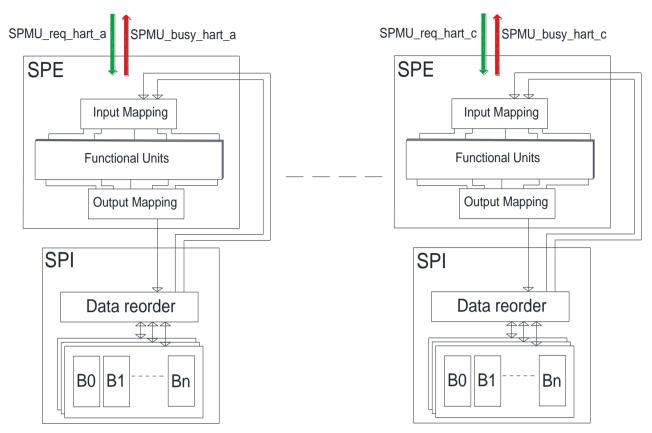

| F / RDEW                                                                  | 3   | 1   | T013       | 61.9                        | 71.8 | 71.8  | n.a.  |  |