# DQN-ROUTING: A NOVEL ADAPTIVE ROUTING ALGORITHM FOR TORUS NETWORKS BASED ON DEEP REINFORCEMENT LEARNING

#### Alessandro Lonardo

A thesis submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Information and Communications Engineering

at

#### SAPIENZA UNIVERSITY OF ROME

DEPARTMENT OF INFORMATION ENGINEERING, ELECTRONICS AND TELECOMMUNICATIONS

Tutor: Prof. Luca De Nardis

Oct 2019

Cycle XXXII

This thesis was evaluated by the two following external referees:

#### **NECTARIOS KOZIRIS**

Professor and Dean of the School of Electrical and Computer Engineering at National Technical University of Athens

### JAVIER NAVARIDAS Lecturer in Computer Architecture at the University of Manchester

The time and effort of the external referees in evaluating this thesis, as well as their valuable and constructive suggestions, are very much appreciated and greatly acknowledged.

#### PhD Advisory Board

#### ANTONIO CIANFRANI Associate Professor at Sapienza University of Rome

STEFANIA COLONNESE Associate Professor at Sapienza University of Rome

ROBERTO CUSANI Professor at Sapienza University of Rome

### Contents

| 1 | Intr | oductio | n                                                    | 1  |

|---|------|---------|------------------------------------------------------|----|

|   | 1.1  | Exasca  | ale Computing: the New Frontier of HPC Architectures | 3  |

|   | 1.2  | The pa  | ath towards Exascale systems and beyond: hurdles and |    |

|   |      | challe  | nges                                                 | 4  |

|   |      | 1.2.1   | Energy efficiency                                    | 5  |

|   |      | 1.2.2   | Reliability                                          | 7  |

|   |      | 1.2.3   | Storage system                                       | 7  |

|   |      | 1.2.4   | Programming models                                   | 8  |

|   |      | 1.2.5   | Interconnection Networks                             | 9  |

|   | 1.3  | Moder   | rn Techniques in Reinforcement Learning              | 12 |

|   |      | 1.3.1   | Enhancements to DQN                                  | 15 |

| 2 | Inte | rconnec | ction Networks for High-Performance Computing        | 17 |

|   | 2.1  | Netwo   | orks classification                                  | 18 |

|   | 2.2  | Netwo   | ork topologies                                       | 20 |

|   |      | 2.2.1   | n-Dimensional torus/mesh                             | 21 |

|   |      | 2.2.2   | Fat-tree and Folded-Clos                             | 22 |

|   |      | 2.2.3   | Dragonfly                                            | 23 |

|   | 2.3  | Route   | r model                                              | 25 |

|   | 2.4  | Packet  | ts, Flits, Phits                                     | 26 |

|   | 2.5  | Packet  | t Switching Techniques                               | 27 |

|   |      | 2.5.1   | Store And Forward (SAF)                              | 27 |

|   |      | 2.5.2   | Wormhole                                             | 29 |

|   |      | 2.5.3   | Virtual Cut-Through (VCT)                            | 30 |

|   | 2.6  | Routin  | ng algorithms                                        | 30 |

|   |      | 2.6.1   | Virtual channels                                     | 31 |

|   |      | 2.6.2   | Deadlock                                             | 32 |

|   |      | 2.6.3   | Livelock                                             | 38 |

|   |      |         |                                                      |    |

|   | 2.7  | Selecti  | on of Routing Algorithms                              | 39 |

|---|------|----------|-------------------------------------------------------|----|

|   |      | 2.7.1    | Dimension-Order Routing (DOR)                         | 39 |

|   |      | 2.7.2    | Star-channel [1]                                      | 41 |

|   |      | 2.7.3    | Min-routing [2]                                       | 42 |

|   | 2.8  | The A    | PEnet Interconnection Network and the ExaNest Project | 44 |

|   |      | 2.8.1    | APEnet                                                | 44 |

|   |      | 2.8.2    | The ExaNeSt project                                   | 48 |

| 3 | DQI  | N-Routi  | ng: a Novel Adaptive Routing Algorithm for Torus      |    |

|   | Netv | works B  | ased on Deep Reinforcement Learning                   | 51 |

|   | 3.1  | Relate   | d Work                                                | 52 |

|   | 3.2  | The D    | QN-Routing Algorithm                                  | 55 |

|   | 3.3  | Consid   | lerations on the Implementation of the Algorithm      | 58 |

| 4 | Exp  | eriment  | tal Setup and Measurements                            | 65 |

|   | 4.1  | The Ex   | xperimental Setup                                     | 65 |

|   |      | 4.1.1    | The Reinforcement Learning Distributed Execution      |    |

|   |      |          | Framework                                             | 66 |

|   |      | 4.1.2    | The Network Simulation Framework                      | 68 |

|   |      | 4.1.3    | Interfacing the Frameworks                            | 69 |

|   |      | 4.1.4    | The Simulated Network Architecture                    | 70 |

|   | 4.2  | Traffic  | Models                                                | 71 |

|   |      | 4.2.1    | Uniform Random Traffic                                | 72 |

|   |      | 4.2.2    | DPSNN Simulator                                       | 72 |

|   | 4.3  | Simula   | ation Results                                         | 74 |

|   |      | 4.3.1    | Metrics and Methods                                   | 74 |

|   |      | 4.3.2    | Uniform Random Traffic                                | 76 |

|   |      | 4.3.3    | DPSNN Traffic                                         | 78 |

| 5 | Con  | clusions | s and Future Work                                     | 81 |

| Aŗ | pend | ices                       |      |  |  |  |  |  |   | 83 |

|----|------|----------------------------|------|--|--|--|--|--|---|----|

| A  |      |                            |      |  |  |  |  |  |   | 85 |

|    | A.1  | Configuration of the Agent | <br> |  |  |  |  |  | • | 85 |

### List of Tables

| 2.1 | The APEnet roadmap to Exascale                           | 45 |

|-----|----------------------------------------------------------|----|

| 2.2 | The ExaNeSt multi-tiered network                         | 49 |

| 4.1 | Measurements obtained simulating the execution of 400 ms |    |

|     | of the DPSNN application distributed on 4x4 processes at |    |

|     | different mean neuron firing rates                       | 79 |

## List of Figures

| 1.1  | Energy efficiency improvement potentials                          | 5  |

|------|-------------------------------------------------------------------|----|

| 1.2  | Bandwidth vs. system distance                                     | 9  |

| 1.3  | Energy vs. system distance                                        | 9  |

| 1.4  | Scheme of a Reinforcement Learning scenario (from Wikipedia)      | 13 |

| 2.1  | Classification of interconnection networks, original image from [ | 3] |

|      | 19                                                                |    |

| 2.2  | Example of a $4 \times 4$ 2D torus (4-ary 2-cube)                 | 21 |

| 2.3  | Fat-tree topology                                                 | 22 |

| 2.4  | Folded-Clos (Fat-tree) network                                    | 22 |

| 2.5  | Fully connected topology example for a dragonfly network          | 23 |

| 2.6  | Internal structure of a generic router model (LC = link con-      |    |

|      | troller). Original image from [3]                                 | 25 |

| 2.7  | Fragmentation of a message into packets, flits and phits          | 27 |

| 2.8  | An example of messages travelling through a wormhole net-         |    |

|      | work. Message A is blocked by message B generating a con-         |    |

|      | tention. Original image from [3]                                  | 28 |

| 2.9  | (a) Unidirectional ring (left) with its channel dependency graph  |    |

|      | (right). (b) Modified deadlock-free unidirectional ring (left)    |    |

|      | with its channel dependency graph (right). Original image         |    |

|      | from [4]                                                          | 35 |

| 2.10 | Path of the DOR algorithm on a 4x4 torus between nodes            |    |

|      | (3,0) and $(0,1)$                                                 | 40 |

| 2.11 | Subsets of the total dependency graph for a fully connected   |    |

|------|---------------------------------------------------------------|----|

|      | dragonfly network. Graph 2.11a depicts a standard configu-    |    |

|      | ration with no additional virtual channels. Graph 2.11b de-   |    |

|      | picts a deadlock-free configuration with extra virtual chan-  |    |

|      | nels (identified by a V letter) for local routing of packets  |    |

|      | coming from other groups                                      | 42 |

| 2.12 | The layered architecture of APEnet                            | 47 |

| 2.13 | A block diagram of APEnet architecture                        | 47 |

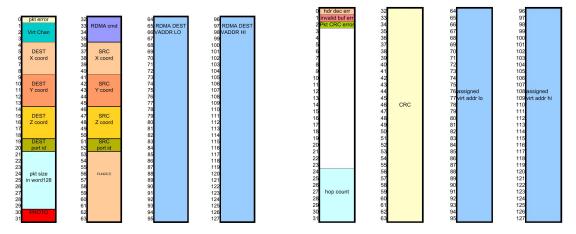

| 2.14 | APEnet packet header                                          | 48 |

| 2.15 | APEnet packet footer                                          | 48 |

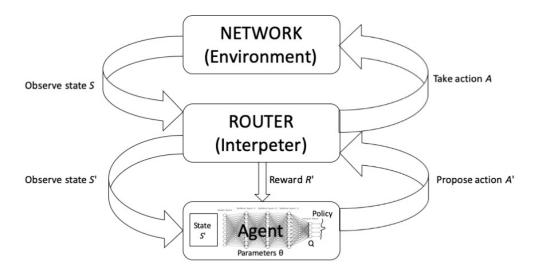

| 3.1  | Reinforcement Learning scenario for DQN-Routing               | 52 |

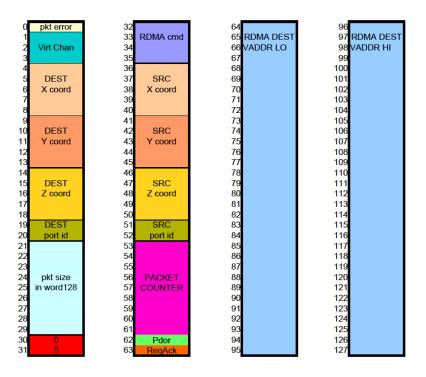

| 3.2  | DQN-Routing table entry                                       | 56 |

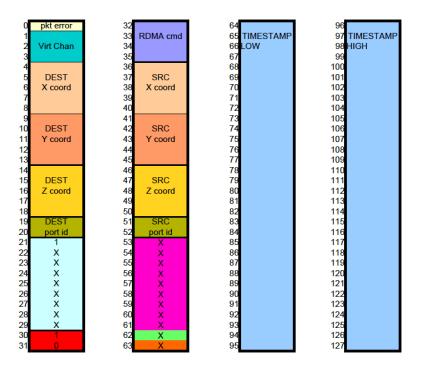

| 3.3  | Header of a DQN-Routing regular traffic packet in the APEnet+ |    |

|      | interconnect                                                  | 58 |

| 3.4  | Header of a DQN-Routing acknowledge traffic packet in the     |    |

|      | APEnet+ interconnect                                          | 60 |

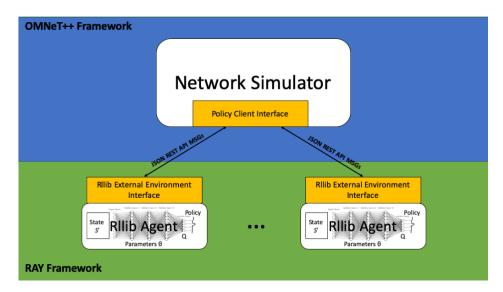

| 4.1  | The integrated simulation framework used as experimental      |    |

|      | setup in this work                                            | 66 |

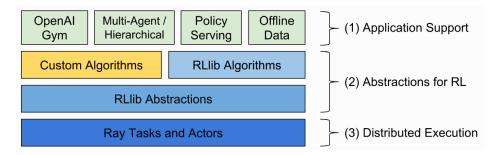

| 4.2  | A stacked modular view of the RLlib library. Original image   |    |

|      | from [5]                                                      | 66 |

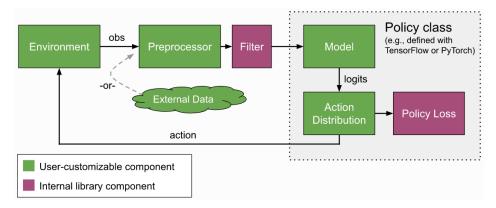

| 4.3  | RLlib components, their relations and customizability. Orig-  |    |

|      | inal image from [5]                                           | 68 |

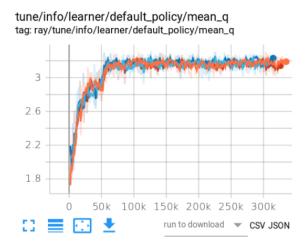

| 4.4  | Monitoring the training of 4 Agents during the simulation     |    |

|      | (mean Q value)                                                | 68 |

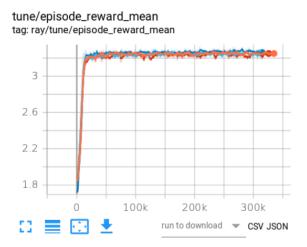

| 4.5  | Monitoring the training of 4 Agents during the simulation     |    |

|      | (mean reward)                                                 | 69 |

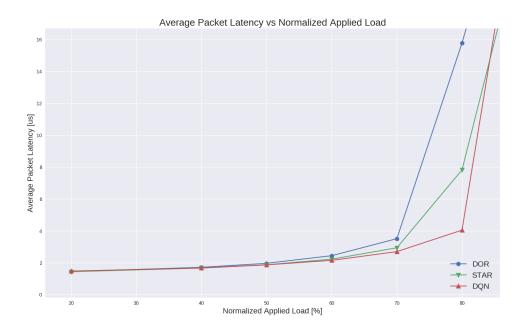

| 4.6  | Average packet latency vs normalized applied load under uni-  |    |

|      | form random traffic                                           | 76 |

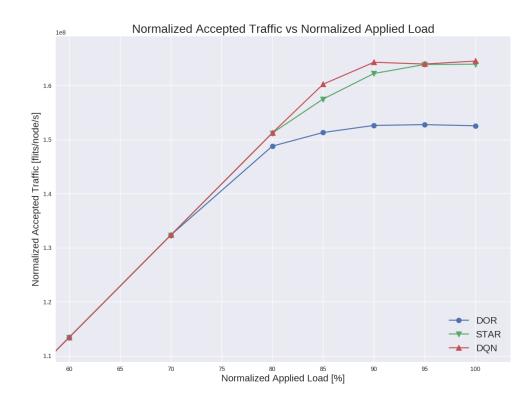

| 4.7 | Normalized accepted traffic vs normalized applied load under |    |  |  |  |  |  |

|-----|--------------------------------------------------------------|----|--|--|--|--|--|

|     | uniform random traffic                                       | 77 |  |  |  |  |  |

## Introduction

Torus networks are widely adopted as custom interconnects in High-Performance Computing (HPC) systems because of a series of interesting features, such as their regular physical arrangement, short cabling at low dimensions, good path diversity and good performance for the rather wide class of workloads characterized by local communication patterns.

One of their main disadvantages is that they have a larger diameter compared to other network topologies, resulting in an increased communication latency at large sizes. Using a relatively small sized torus network as the lowest tier of a multi-tiered hybrid interconnect allows exploiting all the advantages of this class of networks while circumventing their inherent limitations, as demonstrated by recent works [6].

A large number of routing algorithms for this class of networks has been proposed throughout the years, ranging from deterministic to fully adaptive ones, with the aim of improving performance – especially under non uniform traffic conditions – and fault-tolerance.

This thesis describes DQN-Routing: a novel, distributed, unicast, fully adaptive non-minimal routing algorithm for torus networks. The idea behind the algorithm is to leverage the constantly ever-increasing availability of ubiquitous computing power to delegate the routing decision to an agent trained by reinforcement learning [7]. The agent is implemented, according to the Deep Reinforcement Learning approach [8, 9], with a convolutional

neural network trained with a variant of Q-learning (DQN), having local and first-neighbour routers states and packet source and destination coordinates as inputs, and the value functions estimating future rewards for all possible routing actions as output. The agents calculate the reward corresponding to their routing action using the receive timestamp contained in the acknowledge message sent along the reverse path from destination to source node. These rewards are used to guide the training process toward better performance, *i.e.* to perform routing actions that try to minimize the communication latency of the routed packets given the experienced network state.

In our experimental setup, the routing problem is represented as an independent multi-agent reinforcement learning problem, where the environment is provided by the OMNeT++ [10] discrete event simulator framework modeling a torus network under different traffic conditions. The reference network architectures for our investigation have been APEnet [11] and its latest incarnation, the ExaNet [12] multi-tier hybrid network dedicated to HPC. In this context, we focused on the configuration characterized by a number of nodes in the sub-torus tiers equal to sixteen in a 4x4 bi-dimensional torus, which allowed to effectively simulate the network by means of a single, although powerful, GPU-accelerated workstation.

We compare the performance of DQN-Routing as measured on this experimental setup for different traffic conditions with those obtained by state-of-the-art routing algorithms, using traffic patterns generated both synthetically and by our reference application, the Distributed Polychronous Spiking Neural Network simulator - DPSNN [13].

## 1.1 Exascale Computing: the New Frontier of HPC Architectures

Next-generation computing systems are being designed to surpass the speed of today's most powerful supercomputers by five to ten times. We will then enter the domain of Exascale computing, when integrated computing system capable of performing at least a exaFLOPS, or  $10^{18}$  floating point operations per second, will enable scientists to tackle problems that were not solvable in terms of their complexity and computation time (the so-called scientific HPC grand-challenges). A not exhaustive list of such problems includes: lattice QCD simulations, ab initio quantum chemistry, high-resolution climate simulations, extreme scale cosmology, and fluid dynamics.

A problem of particular interest is represented by the simulation of the activity of the human brain, as this would pave the way to the understanding of the inner mechanisms of its functioning, and hopefully to the cure of its diseases. On average, a neuron in the brain connects to about  $10^4$  other neurons. In the human brain, there are approximately  $10^{11}$  neurons and so around  $10^{15}$  connections. Understanding the way the brain works requires the simulation of each of these connections (called synapses). Even a cat brain, which is less than a few percent of a human one, requires a huge data set to be represented, at least a seventh of an exabyte. As of today, with top-tier HPC computing systems in the petaFLOPS range the simulation of the cat brain is just about attainable, but with significantly simplified neurophysiological features [14].

Besides these problems that are fundamental for the advancement of science, there are more application-oriented computing applications in the Exascale domain from which the whole society could have an immediate benefit. To give an idea of the potential disruptive Exascale aftermaths we will mention just a couple of them. Considering the impact on the environment, Exascale systems could enable the development of refined simulation models

of advanced engines and gas turbines increasing by 25-50% the efficiency of combustion, and thus reducing the pollution caused by fossil fuels [15]. Focusing on health, the combination of Exascale computing and Deep Learning techniques is expected to enable precision medicine for treatment of cancer by understanding the molecular basis of key protein interactions, developing predictive models for drug response, and extraction of information from millions of cancer patient records to determine optimal cancer treatment strategies [16].

## 1.2 The path towards Exascale systems and beyond: hurdles and challenges

For decades, the introduction of each new semiconductor manufacturing process led to smaller and faster transistors, and to the doubling in the number of components per integrated circuit approximately every two years, as described by the famous Moore's law. Today, semiconductor process technology has been extended to below 10 nm. Arranging transistors at a smaller scale with the existing materials and technologies represents a big challenge, that involves leaving the classical physics domain and entering the quantum mechanics one. So current technology roadmap, based on the shrinking of the transistor size, may end after three or four generations, posing tremendous challenges to the design of post-Exascale systems. On the other hand, the naive expectation that an Exascale system can be obtained simply enlarging a current Petascale one is readily dispelled by a more thorough examination of the proposals for emerging computing architectures and the common traits of the challenges they are all faced with.

#### 1.2.1 Energy efficiency

The primary constraint for Exascale and post-Exascale systems is their energy efficiency. The number one system in the June 2019 Top500 list [17] of the more powerful HPC deployments in the world is the IBM Summit supercomputer installed at the Oak Ridge National Laboratory, with a 148.6 petaFLOPS maximal achieved performance at a power budget of 10.1 MW. This corresponds to an energy efficiency of 14.7 gigaFLOPS/W, ranking the machine in the second position of the June 2019 Green500 list [18] of the most energy efficient supercomputers in the world, very close to the 15.1 gigaFLOPS/W of the best performing DGX SaturnV Volta. Trying to achieve an exaFLOPS machine simply scaling the IBM Summit supercomputer, assuming it is possible, would yield a ~70 MW power requirement, with associated unsustainable environmental impact and cost of operation.

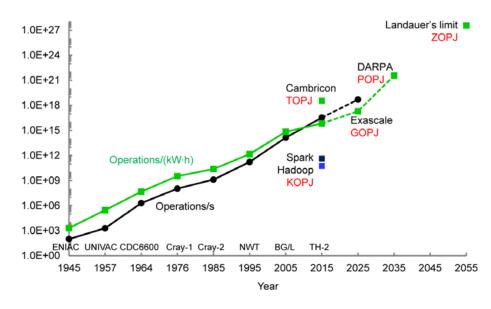

Figure 1.1: Energy efficiency improvement potentials [19]

This energy efficiency bottleneck is the key aspect to take into account in the design and development of Exascale, and post-Exascale, systems. The maximum attainable energy efficiency is dictated by the physical limit proposed by Landauer [20, 21] of  $kT \ln 2$  for the energy needed to perform one-

bit irreversible operation (e.g. reset to one), corresponding to an energy of  $3 \times 10^{-21}$  J at room temperature and a limit for the energy efficiency of about 0.3 zetta operations per joule (ZOPJ). For comparison, the US DoE's exascale research program has the goal of deploying a 1 exaFLOPS machine in the 20-40 MW range of power consumption, corresponding to 25-50 gigaFLOPS/W around year 2022, while the US DARPA's JUMP program targets a long-term goal of 3 peta operations per joule (POPJ) –not necessarily 64-bit IEEE floating point operations— by around 2035. So there is a gap, and a corresponding space of improvement, of roughly six order of magnitudes before reaching the Landauer's limit, as shown in Figure 1.1 [19].

New technologies are to be explored to progress towards this limit: low-power devices and components, energy-aware system scheduling and compilation chains, low-power systems and cooling technology, and low-power heterogeneous computer architectures characterized by the presence of application specific computing accelerators. For the development of the latter class of devices, a hardware and software co-design approach and the maturation of proper cross-layer design methodologies will be necessary.

One last point that has to be mentioned here, is the fact that thanks to the growth in parallelism at all system scales, even performance of today's systems is increasingly determined by how data is communicated among the numerous devices rather than by the total computation resources available. So, as we will discuss in section 1.2.5, perhaps the most critical aspect to consider for the realization of Exascale and post-Exascale systems is the fundamental challenge of energy efficient data movement. With the energy cost of data movement dominating the total energy consumption and representing a key constraint on the final performance, the interconnection architecture plays a fundamental role towards the design of sustainable future HPC systems.

#### 1.2.2 Reliability

With the end of Dennard scaling around 2005, i.e. when processors stopped getting faster as thermal limitations put an end to frequency scaling, the only way to keep increasing their performance was to increment the number of processing units. As a result, the degree of parallelism for a post-Exascale architecture will likely be very high: a ballpark figure of hundreds of millions concurrency is to be expected. Reliability and resiliency will be critical at this scale of parallelism: errors caused by the failure of components and manufacturing variability will creep in and more drastically affect systems operation. It is highly probable that a post-Exascale system will have an even shorter mean time between failures than current HPC systems, which is only hours [22]. Besides software failures (e.g., file system and kernel related failures), hardware related errors (e.g., uncorrectable memory errors) will be equally or more dominant [23]. Progresses in the fields of systemic fault-awareness and fault-reaction coupled with smart checkpointing and task migration strategies will be mandatory to reach post-Exascale performance.

#### 1.2.3 Storage system

Currently, there is a significant gap between performance of processors and memory systems. This is the consequence of their very different rate of increase during the last 20 years: 50% per year for processors performance vs. 10% per year for memory access performance. As a result, the latency of current processors is below 1 ns, while that of current memory systems is around 100 ns; this performance gap is surely one of the main limiting factors to the development of sustainable HPC systems. The traditional approach to improve storage bandwidth of memory systems by increasing both the clock frequency and the width of the storage bus is bounded by physical limits [24]. The emerging 3D stack memory technologies represent a

promising opportunity to break the so-called memory wall, permitting faster clock rates – with suitable processor logic – or permitting multicore access to shared memory using a large number of vertical vias between tiers in the stack [25]. In post-Exascale systems hundreds of millions of processes will perform I/O operations concurrently, requiring hundreds of petabyte (PB) data and dozens of TB/s aggregated bandwidth. Furthermore, this impressive requirements will be combined with the emerging request to support a more complex and diverse set of application domains including, besides traditional HPC, Artificial Intelligence and High Performance Data Analytics. Novel hybrid hierarchy storage architectures will be required to enable high scalability of I/O clients, I/O bandwidth and storage capacity. The extensive use of Non-volatile storage media (NVM) and the integration of storage and Remote Data Memory Access (RDMA) interconnection, along with the development of more scalable and robust distributed filesystems, are promising strategies to significantly improve the efficiency of future storage systems [26].

#### 1.2.4 Programming models

Programming models will have to deal with the very high degree of parallelism expected, allowing the development of software frameworks, possibly domain-specific ones, that will enhance users' productivity in programming, debugging and tuning the applications.

In the the June 2019 Top500 list, the top four systems, and eight in the top ten, integrate some kind of heterogeneous accelerator device in their computing node. This trend will most likely continue in the next years due to performance, energy efficiency, density and costs considerations, so it is essential for Exascale and post-Exascale programming models to fully support heterogeneity of computing devices. Besides this, support for the explicit control of hierarchical parallelism and data locality, to minimize data movement overhead, and the integration of specific functionalities for fault detec-

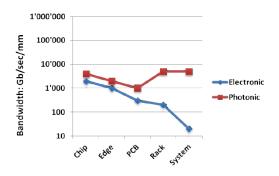

Figure 1.2: Bandwidth vs. system distance

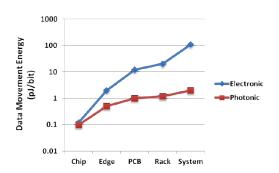

Figure 1.3: Energy vs. system distance

tion and recovery will be mandatory for the full exploitation of the computing resources [27].

#### 1.2.5 Interconnection Networks

The increasing energy consumption and the bandwidth decrease associated with data movement as data propagates from on-chip, across the module (Edge), over the printed circuit boards (PCB), and onto the racks and the whole system is one of the main limiting factor to the scalability of current system architectures. Figure 1.2 shows the bandwidth taper (in blue) for conventional electronic interconnect technology (the units are Gbps/mm of horizontal cross-section), while figure 1.3 shows the relationship between the energy cost of data movement and system distance. For conventional electronic interconnect technology (in blue), off-chip and inter-node communications experience an order of magnitude energy wall and an associated shrinking in bandwidth, while optical photonic interconnect technology (in red) does not face this problems [28].

This spurs the research for interconnection architectures achieving adequate rates of data transfer, or bandwidth, and curtailing the delays, or latency, between the levels while keeping energy consumption under control.

A good design strategy for Exascale and post-Exascale systems interconnect would involve the implementation of a hierarchical network (e.g. intra-

node, inter-node, intra-rack, and inter-rack) and the adoption of the technology (wireless, optical photonic and electronic), network topology, and routing algorithms most suited for each level, considering energy efficiency, latency and bandwidth.

The performance increase needed to reach the forthcoming Exascale systems will be determined by the enhancement of the computing node processing capability along with the increase in the number of computing nodes; considering that the single node processing power should be around 10 teraFLOPS, the focus for this systems is on the architecture of an interconnection network of about 100,000 nodes. The required single node communication bandwidth for this architecture can be easily calculated through the bandwidth to processing performance ratio of a current HPC system. Taking the Tiahne-2 [29] as an example of a well-balanced architecture, with its single-node computing performance of 3 teraFLOPS and node communication bandwidth of 112 Gbps, this ratio is around 0.04 bit/FLOP, so for the Exascale node a communication bandwidth of al least 400 Gbps will be needed to maintain the same ratio [30]. However, for some communicationintensive HPC application like for example computational fluid dynamics or graph processing, a higher ratio and so a even higher network bandwidth would be needed to reach optimal performance.

Silicon photonics interconnects technology offers the possibility of delivering the needed communication bandwidths with extremely scalable energy efficiency, although the lack of practical buffering and the fundamental circuit switched nature of optical data communications require a holistic approach to designing system-wide photonic interconnection networks. New network architectures are required and must include arbitration strategies that incorporate the characteristics of the optical physical layer [31]. For this reasons, they will be probably adopted in later post-Exascale systems, while forthcoming Exascale ones will still be based on conventional electronic interconnects.

Besides bandwidth, it's well known that the mean network communication latency is another critical parameters to be addressed in the design of a network interconnect for a HPC system: using a low-latency interconnect minimizes the impact on application's time-to-solution when scaling the system to a large number of computing nodes [32, 33, 34]. However, efficient communication does not come for free. Traditionally, the handling of network protocols deplete precious processor and memory cycles; more specifically, a common rule-of-thumb states that one CPU clock cycle is needed to process one bit of incoming data. Furthermore, by copying the message payload to intermediate buffers at send or receive side, memory bandwidth is needlessly consumed, the caching subsystem is stressed and the communication latency is increased. Another relevant aspect to be taken in consideration in the design of HPC interconnection networks is the fact that for communicationintensive applications, changes in performance are more highly correlated with changes of variation in network latency than with changes of mean network latency alone [34].

The implementation of host offloading functionalities, such as zero-copy [35] and Remote Direct Memory Access (RDMA) [36], in *smart network inter-faces* has proven to be an effective approach to face these problems, and will be most likely further developed for next generations HPC interconnection networks. Dedicated or configurable computation engines embedded in the network devices have already started to appear: for example the Mellanox Scalable Hierarchical Aggregation and Reduction Protocol (SHARP) [37] is based on dedicated compute engines located on the Infiniband switch data path dedicated for performing data reduction and aggregation operations. These hardware enhancements are referred to as In-Network Computing.

The network topology defines the way in which the computing nodes are connected, and has also a great impact on the performance of the system. For HPC interconnection networks, besides the traditional torus and fat-tree

topologies, more recent ones have been proposed, such as Dragonfly [2]. The properties of these topologies are well-known and they have been used in the design of supercomputers over the last decades. All these topologies are characterized by a rigid structure; recently Jellyfish, a network interconnect adopting a random graph topology and featuring better incremental expandability, shorter paths, and better resilience to failures, has been presented [38]. Again, a multi-tiered network design characterized by the best match between network topology (along with the corresponding routing algorithms) and the network tier (intra-node, inter-node, intra-rack, and inter-rack), will be needed to reach optimal performance for next generations HPC interconnection networks. For example, a two-tiered hybrid interconnect having a torus network as the lower tier and a fat-tree as the upper one can outperform state-of-the-art pure torus and fat-tree networks as long as the density of connections between the two tiers is high enough and the size of the subtori is limited to a few nodes per dimension [6].

#### 1.3 Modern Techniques in Reinforcement Learning

Since this work is heavily based on the exploitation of recent achievement in the branch of Artificial Intelligence known as Deep Reinforcement Learning, we provide here a short overview on the topic [7, 39].

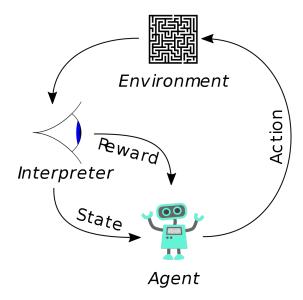

Reinforcement learning is about the problem of an *agent* learning to act, in the sense of mapping situations to actions, in an *environment* in order to maximize a scalar *reward* signal. This is a *closed-loop* problem, as the agent actions have an effect of its later inputs. No direct supervision is provided to the agent, for instance it is never directly told what is the best action in a given situation, instead it must find-out which actions will provide the highest rewards by *exploration*.

Figure 1.4: Scheme of a Reinforcement Learning scenario (from Wikipedia)

Agents and environments. At each discrete time step  $t=0,1,2\ldots$ , the environment provides the agent with an observation  $S_t$ , the agent responds by selecting an action  $A_t$ , and then the environment provides the next reward  $R_{t+1}$ , discount  $\gamma_{t+1}$ , and state  $S_{t+1}$ . This interaction is formalized as a Markov Decision Process, or MDP, which is a tuple  $\langle \mathcal{S}, \mathcal{A}, T, r, \gamma \rangle$ , where  $\mathcal{S}$  is a finite set of states,  $\mathcal{A}$  is a finite set of actions,  $T(s,a,s')=P[S_{t+1}=s'\mid S_t=s,A_t=a]$  is the (stochastic) transition function,  $r(s,a)=\mathbb{E}[R_{t+1}\mid S_t=s,A_t=a]$  is the reward function, and  $\gamma\in[0,1]$  is a discount factor. In our experiments MDPs will be episodic with a constant  $\gamma_t=\gamma$ , except on episode termination where  $\gamma_t=0$ , but the algorithms are expressed in the general form.

On the agent side, action selection is given by a policy  $\pi$  that defines a probability distribution over actions for each state. From the state  $S_t$  encountered at time t, we define the discounted return  $G_t = \sum_{k=0}^{\infty} \gamma_t^{(k)} R_{t+k+1}$  as the discounted sum of future rewards collected by the agent, where the discount for a reward k steps in the future is given by the product of discounts before that time,  $\gamma_t^{(k)} = \prod_{i=1}^k \gamma_{t+i}$ . An agent aims to maximize the expected discounted return by finding a good policy.

The policy may be learned directly, or it may be constructed as a function of some other learned quantities. In value-based reinforcement learning, the agent learns an estimate of the expected discounted return, or value, when following a policy  $\pi$  starting from a given state,  $v^{\pi}(s) = E_{\pi}[G_t|S_t = s]$ , or state-action pair,  $q^{\pi}(s,a) = E_{\pi}[G_t|S_t = s, A_t = a]$ . A common way of deriving a new policy from a state-action value function is to act  $\epsilon$ -greedily with respect to the action values. This corresponds to taking the action with the highest value (the *greedy* action) with probability  $(1-\epsilon)$ , and to otherwise act uniformly at random with probability  $\epsilon$ . Policies of this kind are used to introduce a form of *exploration*: by randomly selecting actions that are suboptimal according to its current estimates, the agent can discover and correct its estimates when appropriate. The main limitation is that it is difficult to discover alternative courses of action that extend far into the future; this has motivated research on more directed forms of exploration.

Deep reinforcement learning and DQN. Large state and/or action spaces make it intractable to learn Q value estimates for each state and action pair independently. In deep reinforcement learning, we represent the various components of agents, such as policies  $\pi(s,a)$  or values q(s,a), with deep (i.e., multi-layer) neural networks. The parameters of these networks are trained by gradient descent to minimize some suitable loss function.

In DQN [8, 9] deep networks and reinforcement learning were successfully combined by using a convolutional neural net to approximate the action values for a given state  $S_t$  (which is fed as input to the network in the form of a stack of raw pixel frames). At each step, based on the current state, the agent selects an action  $\epsilon$ -greedily with respect to the action values, and adds a transition  $(S_t, A_t, R_{t+1}, \gamma_{t+1}, S_{t+1})$  to a replay memory buffer, that holds the last million transitions. The parameters of the neural network are optimized by using stochastic gradient descent to minimize the loss

$$(R_{t+1} + \gamma_{t+1} \max_{a'} q_{\overline{\theta}}(S_{t+1}, a') - q_{\theta}(S_t, A_t))^2, \qquad (1.1)$$

where t is a time step randomly picked from the replay memory. The gradient of the loss is back-propagated only into the parameters  $\theta$  of the *online network* (which is also used to select actions); the term  $\overline{\theta}$  represents the parameters of a *target network*; a periodic copy of the online network which is not directly optimized. The optimization is performed using RMSprop [40], a variant of stochastic gradient descent, on mini-batches sampled uniformly from the experience replay. This means that in the loss above, the time index t will be a random time index from the last million transitions, rather than the current time. The use of experience replay and target networks enables relatively stable learning of Q values, and led to super-human performance on several Atari games.

#### 1.3.1 Enhancements to DQN

Several extensions to DQN have been proposed to overcome the limitations that have become evident with its wide adoption. Here we describe three extensions that have been used in this work.

**Double Q-learning.** Conventional Q-learning is affected by an overestimation bias, due to the maximization step in Equation 1.1, and this can harm learning. Double Q-learning [41], addresses this overestimation by decoupling, in the maximization performed for the bootstrap target, the selection of the action from its evaluation. It is possible to effectively combine this with DQN [42], using the loss

$$(R_{t+1} + \gamma_{t+1}q_{\overline{\theta}}(S_{t+1}, \underset{a'}{\operatorname{argmax}} q_{\theta}(S_{t+1}, a')) - q_{\theta}(S_t, A_t))^2.$$

This change was shown to reduce harmful overestimations that were present for DQN, thereby improving performance.

**Prioritized replay.** DQN samples uniformly from the replay buffer. Ideally, we want to sample more frequently those transitions from which there is much to learn. As a proxy for learning potential, prioritized experience replay [43] samples transitions with probability  $p_t$  relative to the last encountered absolute  $TD\ error$ :

$$p_t \propto \left| R_{t+1} + \gamma_{t+1} \max_{a'} q_{\overline{\theta}}(S_{t+1}, a') - q_{\theta}(S_t, A_t) \right|^{\omega},$$

where  $\omega$  is a hyper-parameter that determines the shape of the distribution. New transitions are inserted into the replay buffer with maximum priority, providing a bias towards recent transitions. Note that stochastic transitions might also be favoured, even when there is little left to learn about them.

**Dueling networks.** The dueling network is a neural network architecture designed for value based RL. It features two streams of computation, the value and advantage streams, sharing a convolutional encoder, and merged by a special aggregator [44]. This corresponds to the following factorization of action values:

$$q_{\theta}(s, a) = v_{\eta}(f_{\xi}(s)) + a_{\psi}(f_{\xi}(s), a) - \frac{\sum_{a'} a_{\psi}(f_{\xi}(s), a')}{N_{\text{actions}}},$$

where  $\xi$ ,  $\eta$ , and  $\psi$  are, respectively, the parameters of the shared encoder  $f_{\xi}$ , of the value stream  $v_{\eta}$ , and of the advantage stream  $a_{\psi}$ ; and  $\theta = \{\xi, \eta, \psi\}$  is their concatenation.

# Interconnection Networks for High-Performance Computing

The research in High-Performance Computing (HPC) architectures tries to give an answer to the ever-increasing demand for computing power. Today, the target for top-notch systems is in the range of the exascale computing, that means an integrated computing system capable of performing at least a exaFLOPS, or a billion billion floating-point operations per second (the prefix exa- denotes a factor of  $10^{18}$ ).

As we discussed in section 1.2.5, the design of a scalable and low-latency interconnection network is one of the main challenges in developing such distributed-memory multiprocessor systems: the communication subsystem turns out to be the bottleneck in most applications, with the *inter-node* communication latency, and its stability, being one of the most critical parameters of the overall parallel computing architecture.

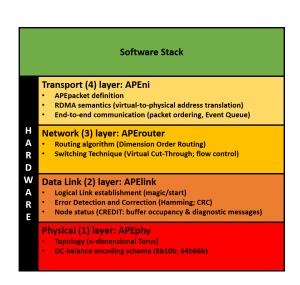

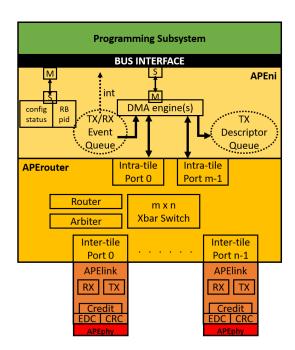

After providing a summary of nomenclature and concepts used in the domain of interconnection networks according to the reference books from J. Duato et al. [3] and W. Dally et al. [45] we describe the architecture of the APEnet interconnection network [46] implementing, in its latest incarnation, the physical, data link and network layers of the ExaNeSt [12, 47] HPC architecture.

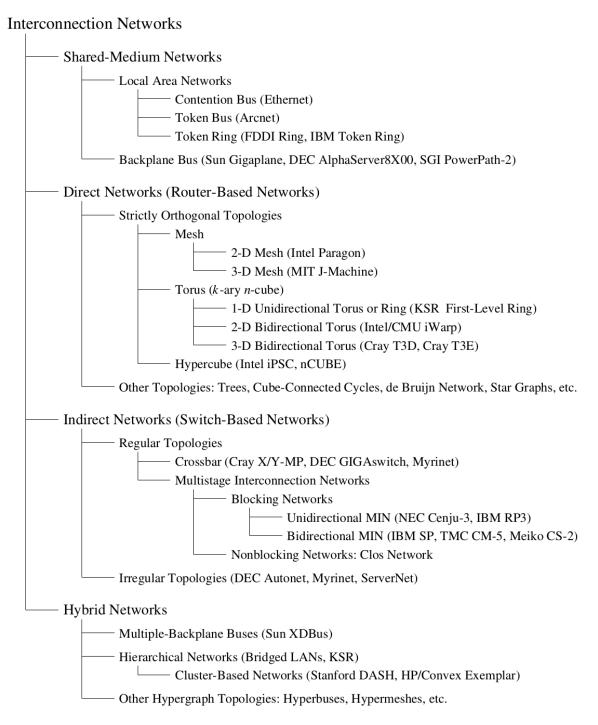

#### 2.1 Networks classification

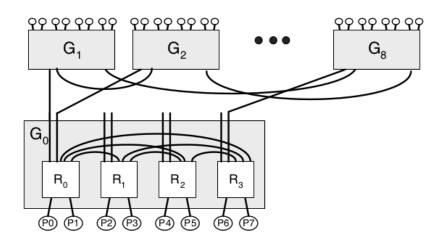

A classification of interconnection networks is shown in Figure 2.1; this scheme is not fully exhaustive but it is more than adequate for our purposes. According to this schema we can categorize networks in four main categories: *shared-medium* networks, *direct* network, *indirect* network and *hybrid* networks.

Shared-medium networks use a common medium to connect all the devices. Due to its shared nature the network experiences a severe performance degradation when the number of nodes increases. They usually provide good multicast/broadcast<sup>1</sup> performance and are used in small systems like multi-CPU nodes.

Direct networks uses a point-to-point node-to-node interconnection. Every node is a compute unit with its own processor, memory and peripherals. Each node has a router block which handles the communication with a subset of the nodes called neighbours and all the nodes are connected according to a given network topology. To establish communication between non-neighbour nodes intermediates steps are used according to a routing function. Direct networks offer good scalability and are used in many HPC systems.

Indirect networks are made of nodes interconnected through switches. Every node is a compute unit but it has no routing capability, the only network functionality of the node is carried out by the network adapter which connects the node to a switch. Every switch has a fixed number of ports and every port can be connected to: a node, another switch or not connected. The connection of the switches generates the network topology and the routing algorithm selects the path between the nodes. Having the compute node outside of the switch increases the distance across two nodes by two producing higher net-

<sup>&</sup>lt;sup>1</sup>A multicast is a special send of a message from a node to many nodes, a broadcast is a particular case of multicast in which a message is sent to all the nodes

Figure 2.1: Classification of interconnection networks, original image from [3]

work latency<sup>2</sup>. Indirect networks are commonly used in data centres because they are easier to maintain and do not require specialized network capabilities from the compute nodes.

Hybrid networks combine the use of direct and indirect network to achieve better performance. To mitigate the performance degradation of direct networks a hierarchical structure can be used, generating islands of direct networks interconnected using indirect networks. This approach is gaining acceptance into the HPC community.

#### 2.2 Network topologies

In both direct and indirect networks the topology can be modelled by a directed graph G(N, C), where the edges of the graph represent the C unidirectional communication channels<sup>3</sup> and the vertices the N switches or nodes for indirect and direct networks respectively. Using this simple model we can define some basic network properties from the graph representation:

- *Node degree/Switch radix:* Number of channels connecting a specific node/switch to its neighbours.

- Distance: The distance d(a, b) between node a and node b of the network is defined as the minimum number of hops required for going from a to b. Since graph is directed the distance may not be commutative.

- *Diameter:* The maximum distance between two nodes in the network.

- *Regularity:* A network is *regular* when all the nodes have the same degree.

- Symmetry: A network is symmetric when it looks alike from every node.

<sup>&</sup>lt;sup>2</sup>Network latency is defined as the time to wait before receiving the data over the network.

<sup>&</sup>lt;sup>3</sup>Bidirectional channels can be represented as a couple of unidirectional ones.

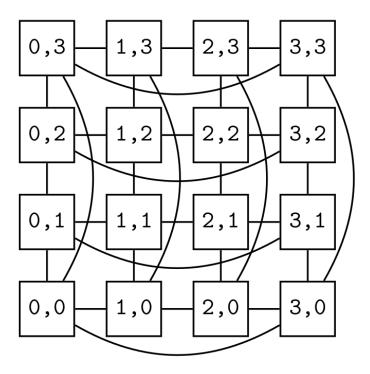

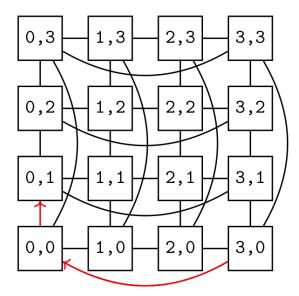

Figure 2.2: Example of a  $4 \times 4$  2D torus (4-ary 2-cube).

We will now present some relevant network topologies and characterise their properties with a special focus on scalability.

#### 2.2.1 n-Dimensional torus/mesh

In a n-dimensional torus having k nodes along each dimension, referred also as k-ary n-cube, there are  $N=k^n$  nodes, each one connected to 2n neighbours, as depicted in Figure 2.2, therefore the nodes can be imagined as distributed on an n-dimensional grid<sup>4</sup>. The nodes at the boundaries of the grid are connected across the borders of the network providing: periodic boundary conditions, symmetry and regularity. The diameter of the network depends on the shape of the grid and on the torus dimensions, for an n-dimensional cubic grid of N nodes the diameter is:

$$d = n\frac{\sqrt[n]{N}}{2} = n\frac{k}{2} \tag{2.1}$$

<sup>&</sup>lt;sup>4</sup>The network topology specifies only the connection between the nodes and not their position in space.

Figure 2.3: Fat-tree topology

Figure 2.4: Folded-Clos (Fat-tree) network

From a scalability point of view this topology has a fixed node degree and a variable diameter, increasing the number of dimensions of the network provides a better scalability at the cost of more connectivity. Thanks to its fixed degree this topology is widely used in HPC's direct networks since adding more nodes does not change the structure of the node itself.

Meshes are similar to tori but they have open boundary conditions, so the network is asymmetric and irregular. The degree of the nodes is not constant, the diameter is  $n(\sqrt[n]{N}-1)$ .

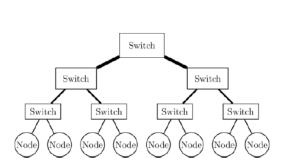

#### 2.2.2 Fat-tree and Folded-Clos

Fat-tree topology was proposed by Leiserson in 1985 as an interconnection network for general-purpose parallel supercomputers with provably efficient communication [48]. In a tree topology, the traffic loads on the links increase moving towards the root: the main idea behind fat-tree network is to have higher capacity links as we approach the root, as shown in figure 2.3. To implement this concept, fat-tree networks requires switches with an increasing number of ports, to support more links, moving from leaf nodes to the root. This translates into a high cost of deployment when scaling the number of nodes, since high-radix switches are expensive devices.

Figure 2.5: Fully connected topology example for a dragonfly network.

To overcome this limitation to the scalability of the network, a variation of the fat-tree can be build with a Folded-Clos [49] topology, using smaller radix switches, as shown in Figure 2.4. With this approach, it is possible to replace each high-radix switch close to the root with a set of low-radix switches, that logically behaves like a high-radix one.

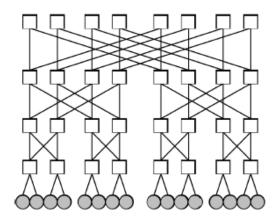

#### 2.2.3 Dragonfly

This topology aggregates routers in an efficient way to make them behave as higher radix ones [2]. The hierarchical structure of the network is composed by three levels: router, group and system. The *intra-group* and *inter-group* interconnection network topologies can be selected to achieve the system requirements.

In a dragonfly network we have:

- p Terminals connected to each router using terminal channels<sup>5</sup>

- N Network terminals

- a Routers in each group

<sup>&</sup>lt;sup>5</sup>This connection can be done internally for a direct network or externally using a port of the switch for an indirect network.

- 24

- h Channels within each router used to connect to other groups

- q Groups in the system

Every router is connected to p terminals, a-1 local channels and h global channels, therefore the radix of every router is k=p+a+h-1. Because every group consists of a routers connected via intra-group channels it can be considered as a virtual router with an effective radix k'=a(p+h). This very high radix (k'>>k) enables the system level network to be realized with very low global diameter, defined as the maximum number of expensive global channels on the minimum path between any two nodes. The parameters a, p and h can have any value; however, to get the optimal load balancing of the network traffic the parameters should respect the following relation:

$$a = 2p = 2h \tag{2.2}$$

This ratio is derived from the fact that each packet traverses two local channels along its route (one at each end of the global channel) for one global channel and one terminal channel. The basic topology is depicted in Figure 2.5 and uses a fully connected topology for both the inter-group and intragroup networks: if we make this particular choice the network is *regular* and *symmetric*. The *diameter* of the network is 3 for a direct configuration and 5 for an indirect one using the relation (2.2) for the parameters with p = h = 2, a = 4 the networks scales to N = 72 with k = 7 routers. By using virtual routers, the effective radix is increased from k = 7 to k' = 16. Different topologies can be used to reduce the radix of the nodes at the cost of an increase in network *diameter*.

2.3. Router model

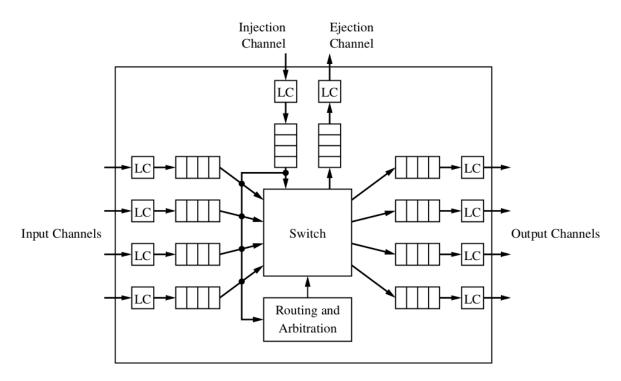

Figure 2.6: Internal structure of a generic router model (LC = link controller). Original image from [3]

#### 2.3 Router model

Before going any further in this brief introduction to interconnection networks it is fundamental to define and describe a router model. A comprehensive and clear model is the one proposed in [3] which is a good representation of the real hardware architecture of a router. The internal architecture shown in Figure 2.6 is divided into the following main components:

- **Buffers:** *FIFO* buffers are used for storing messages in transit. The model in Figure 2.6 has buffers for input and output channels but alternative designs may have input or output buffers only.

- Switch: This component connects input buffers to output buffers.

- Routing and arbitration unit: Those components implement the routing algorithm, selecting the appropriate output channel for an incoming message and setting the switch accordingly. If the same output chan-

nel is requested by multiple messages at the same time the arbitration unit must resolve the contention. The arbitration policy can be a simple round robin or a complex priority algorithm.

- LC (Link Controller): It implements the control flow logic for the messages across the channel between two routers.

- **Processor interface:** This component is a channel interface to the local processor instead of an adjacent router. It consists of one or more injection and ejection channels.

This router model is designed for direct networks but can be used as a switch model for indirect networks if we remove the processor interface.

#### 2.4 Packets, Flits, Phits

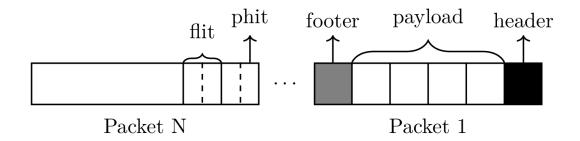

In order to transfer data over the network, they must be prepared and they may be split in chunks. This process is called packetization and it is done in the following way: the *message* to be transferred over the network is split in to chunks of a fixed size and all of the chunks are then encapsulated into *packets*. Packets are made of two parts a data one called *payload* and a protocol part called *header*.

The *packet* is the smallest unit of information that can be sent over the network, therefore the *header* must contain all the addressing data needed to deliver the payload to its destination; this information is crucial for the delivery, so the *header* is stored into the first part of the packet. Other useful protocol information, like error correction codes, can be stored into the optional *footer* which is stored into the last part of the packet.

The *packet* is then divided into smaller sub-units called *flits* (flow-control units), those units are the ones whose transfer is requested by the sender and acknowledge by the receiver. *Flits* may be divided into *phits* (physical units)

Figure 2.7: Fragmentation of a message into packets, flits and phits.

which are the units of information that can be physically transferred in a single cycle between two nodes. All the different sub-units of information are depicted in Figure 2.7.

#### 2.5 Packet Switching Techniques

A crucial aspect of a network infrastructure is how the packets are switched and saved into intermediate nodes during their path. In both direct and indirect networks some switching action is required but we have not yet defined a policy for switching the packets. In this section three of the main switching techniques are presented: *store and forward*, *wormhole* and *virtual cut through*. Whatever policy we decide to adopt, we need to manage a critical physical resource: the receiving/sending buffers. Every switching technique has to decide how to manage the free space in the buffers and when to start and stop forwarding packets. When the network is in a congested state, a large fraction of the packets are waiting for resources.

#### 2.5.1 Store And Forward (SAF)

This switching technique is very simple and works as follows:

• The node receives all the flits of the packet and stores them into the receiving buffer of the channel.

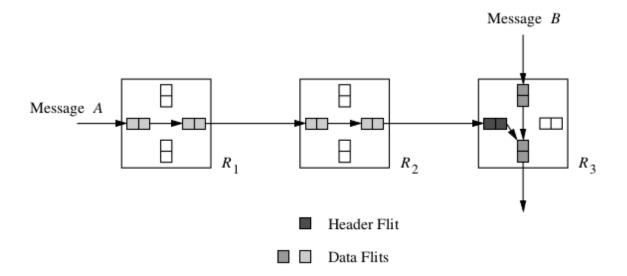

Figure 2.8: An example of messages travelling through a wormhole network. Message A is blocked by message B generating a contention. Original image from [3]

- The header is parsed by the router and the output port is calculated.

- If the receive buffer of the next node has enough free space to store the full packet and the channel is free the packet is forwarded, otherwise it waits.

This approach let the router deal only with complete packets. The main draw-back of this switching technique is latency: at every hop the switch has to wait for the full transfer of the packet before forwarding the information. In absence of congestion the latency L of a packet is given by the (2.3) where:  $n_{flits}$  is the number of flits of the packet,  $n_{hops}$  is the number of hops between source and destination and  $t_{flit}$  is the time needed to transfer a single flit<sup>6</sup>.

$$L = t_{flit} \cdot n_{flits} \cdot n_{hops} \tag{2.3}$$

#### 2.5.2 Wormhole

This technique is the opposite of the SAF one. The switch forwards the packet a flit at the time as depicted in Figure 2.8 following this schema:

- The first flits of the packet containing the header are received and stored into the receiving buffer.

- The header is parsed by the router and the output port is calculated.

- If the receive buffer of the next node has enough free space to store a single flit and the channel is free the first flit is forwarded, otherwise it waits.

- Every new flit is forwarded as soon as available if the buffer and the channel are free.

In order to take the routing decision the router has to parse the entire header, this makes crucial keeping the header into the smallest possible number of flits, preferably one. The main advantage of this approach is the reduced latency by pipelining of the full packet transmission time across the hops. The latency L in absence of congestion can be calculated as follows:

$$L = t_{flit} \cdot (n_{flit} + n_{hops}) \tag{2.4}$$

Wormhole routing requires a more complex flow control system which has to be able to stop and resume the transfer of the packet if congestion occurs, and it is more prone to congestion because a packet uses resource of multiple nodes at the same time.

<sup>&</sup>lt;sup>6</sup>We are neglecting the time spent by the router to make the routing decision, this time is common to all the switching techniques and therefore not interesting in this comparison.

#### 2.5.3 Virtual Cut-Through (VCT)

In this case we want to take the best from both wormhole and SAF and combine them into a single technique. A VCT network behaves like a wormhole one apart from the forwarding requirements: to forward a packet the receiving buffer must have enough free space to store the full packet. In this way we have the same flow control simplicity and resources occupancy as in a SAF network but the same latency of a wormhole network in absence of congestion. The main drawback is an higher buffer capacity requirement than a wormhole network: in a wormhole network the buffers must provide at least enough free space to store a single flit; in VCT and SAF networks the buffers must provide at least enough free space for a full packet.

#### 2.6 Routing algorithms

A *routing algorithm* defines which route a packet should take while travelling from its source to its destination. The selection of the algorithm can heavily affect network performance, therefore we have to select it carefully. In this section we will discuss the minimum requirements for a routing function and we will discuss different approaches to the problem of routing a packet.

It is useful to give some basic definitions. A *routing function* calculates the next step that a packet has to take in its path towards its destination: in principle we could use information gathered across the whole network to calculate the path but, if we want to achieve a good scalability of the system, this approach is not practical. In this work we will consider routing functions that use only local information, coming from the packets, the node, and its first-neighbour nodes.

The routing action is modelled as a two stage process implemented by two separated functions: routing and selection. The routing function provides a set of output channels based of the current node and the destination of the packet. The selection among the provided channels is made by the selection function based on the status of the output channels of the current node. To be selected a channel must be free according to the switching technique in use, if all the channels are busy the packet will wait for an available one. Because the routing function selects the subset of output channels it will be the only part responsible for granting the delivery of the packet, while the selection function will only affects performance. In this routing model the domain of the routing function is NxN for an N nodes network, because the function considers only the destination and the current nodes.

A routing function is *connected* if any node of the network can reach any other node, and because we want all the packets to be delivered on the network, every routing function must be *connected*. The routing function can select always the same path between two nodes or can choose between multiple ones according to the network traffic, the algorithms in the first case are called *deterministic*, the ones in the second case are called *adaptive*. An algorithm is *fully adaptive* if has the possibility to use all the possible paths. A routing function is *minimal* if it only supplies channels that bring the packet closer to its destination.

The minimum requirement for a routing algorithm is to deliver packets in a finite amount of time regardless of the network traffic, an in-depth study of this condition will be done especially for what concerns *deadlock* and *livelock*. Before introducing the problem we need to introduce one useful instrument to solve it: virtual channels.

#### 2.6.1 Virtual channels

In section 2.5 we learned that the critical resources while sending packets over a network are the receiving buffers. A common strategy consists of optimizing the channel usage and reducing congestion using virtual channels [50]. Virtual channels consist on a set of duplicated buffers multiplexed

and demultiplexed into the same physical channel by the link control logic. From the switch point of view there is no difference between a physical channel and a virtual one because the switch sees only the buffers, all the physical layer is handled by the link controller. By adding a virtual channel we can effectively increase the number of channels in the network without adding the extra cost and complexity of the real hardware link. All the virtual channels share the bandwidth of the physical link with a certain policy, for example round robin. If we select a non uniform policy it is possible to implement QoS into the network using several virtual channels with different priority levels. In this work virtual channels will be used only to implement deadlock-free routing.

#### 2.6.2 Deadlock

A deadlock occurs when some packets cannot advance toward their destination because the buffer requested by them are full. A *configuration* is an assignment of a set of packets or flits to each buffer. A deadlocked configuration occurs when some packets are blocked for an infinite amount of time because they are waiting for resources that will never be granted because they are held by other packets. This condition must be avoided since it breaks the functionality of the network itself.

A deadlocked configuration is called *canonical* if all of the packets present into the network are blocked. We will study only canonical configurations because any other deadlocked configuration has a corresponding canonical one. To obtain a canonical deadlock configuration it is sufficient to stop injecting new traffic into the network and wait for the delivery of all the non blocked packets.

The presence or the absence of potentially deadlocking configurations is a property of the routing algorithm in use. The same topology with the same number of virtual channels may be deadlock-free or not depending on the selected routing algorithm. On the other hand this property is independent of the network traffic and must be verified without making any assumption on the traffic pattern.

To avoid deadlock we will focus on two opposite approaches: the detection of and the reaction to a deadlock configuration, and the impossibility of deadlock configurations to occur. The first method requires the network to be aware of being in a deadlocked state and to react breaking the deadlock condition. If we want to certainly detect a deadlock configuration we need to use non local information which is usually difficult to collect and analyse in large networks. If we want to use only local information we can guess if a packet is deadlocked by using a time-out system. This approach can lead to misidentification of congested packets into deadlocked ones if the network is heavily congested, leading to performance degradation. The reaction to a detected deadlock requires the capability of retransmitting packets that need to free resources. The network must detect and react to the deadlocked configurations faster than they occur, otherwise different deadlocked configurations can pileup generating network malfunctions. The second method consists of providing a routing algorithm that cannot generate deadlocked configurations. Because this property must be traffic-independent it is not trivial to proof that a routing algorithm is deadlock-free, but this problem can be approached using some graph theory and a bunch of theorems.

**Definitions** We introduce now the concept of *channel dependency* [4] and the *channel dependency graph*: there is a dependency between channels i and j, if the routing algorithm can forward a packet holding resources on channel i to channel j; the channel dependency graph is a directed graph D = G(C, E) which vertices are all the unidirectional channels in the network I and arcs represents the pairs  $(c_i, c_j)$  such that there is a channel dependency from  $c_i$  to  $c_j$ .

We define the routing subfunction  $R_1$  for a given routing function R as a routing function defined on the same domain as R that supplies a subset of the channels supplied by R. The channels supplied by  $R_1$  for a given packet destination are indicated as escape channels for the packet; let's refer to the set of the escape channels with  $C_1$ . The extended channel dependency graph of  $R_1$  is defined as the channel dependency graph in which all vertices belong to  $C_1$ , the graph is constructed taking into account a wider class of dependencies between channels (direct, indirect, direct cross and indirect cross) [51]. In the case of VCT and SAF networks, only direct and direct cross dependencies must be considered in building the extended channel dependency graph.

**Necessary and Sufficient Condition** The previous definitions finally allow us to enunciate the following important theorem[51] proposing a necessary and sufficient condition for a routing function to be deadlock-free:

**Theorem 1.** A connected routing function R for an interconnection network I is deadlock-free if and only if there exists a routing subfunction  $R_1$  that is connected and has no cycles in its extended channel dependency graph.

If the routing algorithm is deterministic the only connected subfunction is R itself, so in this case the channel dependency graph and the extended channel dependency graph of  $R_1$  are identical. Therefore the resulting condition for deadlock-free routing for non adaptive routing can be stated in the following corollary, originally proposed as a theorem [4]:

**Corollary 1.** A deterministic routing function R for an interconnection network I is deadlock-free if and only if there are no cycles in its channel dependency graph D.

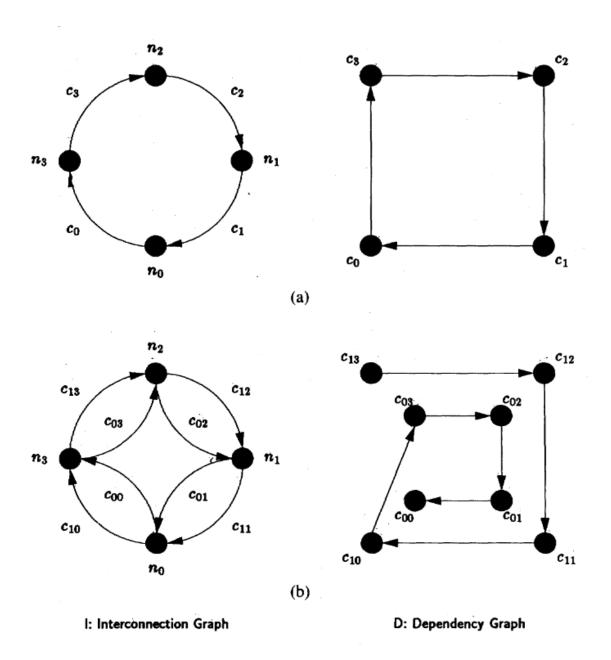

This corollary can be used to generate deadlock-free deterministic routing functions, as in the following example. Consider a ring network of four nodes connected by unidirectional channels, as the one depicted in Figure 2.9(a), its

Figure 2.9: (a) Unidirectional ring (left) with its channel dependency graph (right). (b) Modified deadlock-free unidirectional ring (left) with its channel dependency graph (right). Original image from [4]

### Algorithm 1: Deadlock-free routing for unidirectional ring using high and low virtual channels

```

1: if curr = dest then

2: Channel := Internal;

3: else if curr < dest then

4: Channel = c_{1curr}

5: else

6: Channel = c_{0curr}

7: end if

```

channel dependency graph D is shown on the right. Because of the simplicity of this network the only connected routing function is the one that forwards the packet through the only available channel if the destination is different from the current node. The channel dependency graph for this algorithm is not acyclic, therefore the network is not deadlock-free. In this trivial example it is very easy to find a deadlocked configuration: any configuration with all the buffers from all the nodes filled up with packets and zero packets arrived at destination is deadlocked.

We can make this network deadlock-free by splitting each physical channel into two groups of virtual channel: high virtual channels ( $c_{10}$ , ...,  $c_{13}$ ) and low virtual channels ( $c_{00}$ , ...,  $c_{03}$ ) as shown on the left of Figure 2.9(b).

The routing function 1 and the introduction of two virtual channels per physical channel modify the channel dependency graph into the one depicted on the right of Figure 2.9(b) which is acyclic, therefore the network is now deadlock-free.

Sufficient Condition for VCT and SAF Switching Networks If we focus on VCT and SAF switching networks, only direct and direct cross dependencies must be considered in building the extended channel dependency graph [51]. Direct cross-dependencies are due to the fact that some channels are used either as escape channels or as regular channels depending on packet destination. To avoid this situation, we can define the  $R_1$  subfunction using the  $C_1$  subset

of channels as follows:

$$R_1(x,y) = R(x,y) \cap C_1 \forall x, y \in N \tag{2.5}$$

With this definition of  $R_1$  a channel that belongs to  $C_1$  will be used always as an escape channel for all possible destinations for which it can be supplied by R, so the cause of direct cross-dependencies is eliminated: the channel dependency graph and the extended channel dependency graph of the routing subfunction are identical. This allows to define the following corollary, that provides a direct manner to check whether a routing function is deadlock-free (sufficient condition):

**Corollary 2.** A connected routing function R for an interconnection network I is deadlock-free if there exixts a channel subset  $C_1 \subseteq C$  such that the routing subfunction  $R_1(x,y) = R(x,y) \cap C_1 \forall x,y \in N$  is connected and has no cycles in its channel dependency graph  $D_1$ .

Finally, the following theorem proposes a relevant property of routing subfunctions defined according to expression 2.5:

**Theorem 2.** A connected routing function R for an interconnection network I is deadlock-free if there exists a channel subset  $C_1 \subseteq C$  such that the routing subfunction  $R_1(x,y) = R(x,y) \cap C_1 \forall x,y \in N$  is connected and deadlock-free.

**Duato's Protocol for VCT or SAF Networks** Theorem 2 is at the basis of a methodology, referred as Duato's Protocol (DP), that provides fully adaptive minimal and nonminimal routing algorithms, starting from a deadlock-free connected routing algorithm. Given a VCT or SAF switching interconnection network  $I_1$ , the DP is accomplished in two stages:

1. Select one of the existing routing functions for  $I_1$ , let it be  $R_1$ .  $R_1$  must

be deadlock-free and connected, it can be deterministic or adaptive.  $C_1$  is the set of channels supplied by  $R_1$ .

2. Split each physical channel into a set of additional virtual channels, C is the set of all the virtual channels in the network.  $C_{xy}$  represents the set of output channels from node x that belongs to a path from node x to node y. The new routing function R can then be defined as:

$$R(x,y) = R_1(x,y) \cup (C_{xy} \cap (C - C_1)) \forall x, y \in N$$

(2.6)

So the new routing function can use any of the added virtual channels or, in alternative, the channels supplied from the starting routing function R1, but new routing options to  $C_1$  are not allowed.

In this work we followed the DP methodology to guarantee that DQN-Routing is deadlock-free, as we will see in chapter 3.

#### 2.6.3 Livelock

Livelock is a misbehaviour of the routing algorithm which forwards packets along a path that does not contain their destination, resulting in not delivered packets and wasted network bandwidth. Any minimal routing function is automatically livelock-free, the distance d between any couple of nodes into the network is a finite quantity, therefore every minimal path algorithm delivers any packets in d steps. For non minimal algorithm extra attention to avoid livelock must be paid, especially if the algorithm uses only local information to calculate the path.

A simple technique to avoid livelock, that has been used for this work, is to limit the number of non minimal hops that a packet can take; this limitation reduces the flexibility of the algorithm but avoids infinite looping.

#### 2.7 Selection of Routing Algorithms

In this section several routing algorithms for tori and dragonfly will be presented. For each algorithm we provide proof of the absence of livelock and deadlock.

#### 2.7.1 Dimension-Order Routing (DOR)

DOR [4] is a minimal non adaptive routing algorithm for n-dimensional tori and meshes. Because of the simplicity of this algorithm it is often used as a base for more complex ones.

The position of the nodes in the network is indicated by n integers giving the Cartesian coordinates of the node into the grid. The algorithm starts comparing the node coordinates against the packet destination coordinates from dimension 0 up to dimension n-1. If the coordinates are different the packet is forwarded following the minimal path to the destination, if the coordinates are equal no action is required: the packet has arrived to its destination. The critical point of the algorithm is to manipulate the n dimensions in a fixed order<sup>7</sup>. Figure 2.10 depicts an example of path selected by the dimension-order algorithm on 2D torus.

The algorithm uses minimal paths so it is livelock-free by definition. Before considering the deadlock freedom of the algorithm it is useful to divide the channels into classes:

- A channel belongs to the class  $d^+$  if it connects two node in the dimension d in the increasing coordinates direction.

- A channel belongs to the class  $d^-$  if it connects two node in the dimension d in the decreasing coordinates direction.

<sup>&</sup>lt;sup>7</sup>The order relation can be any total one and it can be selected only once. To change the order relation the network has to be completely empty.

Figure 2.10: Path of the DOR algorithm on a 4x4 torus between nodes (3,0) and (0,1).

To proof the absence of deadlock configurations, we can use the corollary 1 and discuss the channel dependency graph. Thanks to the dimension order any channel of class  $i^{\pm}$  cannot depend on any channel of the class  $i^{\pm}$ where j > i, this removes all the possible loops between channels belonging to different dimensions. The algorithm selects the minimum path to the destination, for a given dimension d the shortest path can be either in the direction + or in the direction - but it cannot be in both directions. Therefore it is impossible to generate dependencies between channels  $d^+$  and  $d^-$  in the same dimension. The only possible source of cyclic dependency left is within channel of the same class. If we consider a mesh network, packets are not allowed to cross the boundaries of the network, preventing deadlock. The torus topology requires more attention because the algorithm is not deadlock-free in the form presented before. A single channel class of a torus is exactly the same topology as the circular network depicted on the left in Figure 2.9(a), therefore adding one extra channel dedicated to the packets that have crossed the border is enough to remove any deadlocking situation. The extra virtual channels are only required for half of the nodes in the class. In the real implementation it is good practice to keep the nodes symmetric and add the extra virtual channel for all the nodes in the class.

#### **2.7.2** Star-channel [1]

This is a minimal path, fully adaptive routing algorithm for *n*-dimensional tori and meshes based on the dimension-order routing. This algorithm adds an extra virtual channel to the ones used by the DOR to achieve full adaptivity. The idea behind this routing function is to use the DOR as an *exhaust valve* for any possible deadlock configuration originated by the adaptive behaviour.

The network is divided into two sub-networks: one is the *star* subnet made of all the channels used by the dimension-order algorithm, the other is the *nonstar* one which has one virtual channel on every link<sup>8</sup>. The routing algorithm uses the two subnetworks according to the following rules:

- A packet can use a free channel of the *nonstar* subnet to follow a minimal path to its destination in any dimension.

- A packet can use a *star* channel only if it respects the dimension order criterion.

Livelock can be excluded because the algorithm uses minimal paths. To exclude deadlock we can use the channel dependency graph. Packets can only use the *star* channels if they meet all the dimensional requirements imposed by the algorithm. Because the dimension-order routing function has an acyclic graph, the extra dependency added by the presence of the *nonstar* subnet cannot generate deadlock configurations. For VCT and SAF switching networks, we can use theorem 2, where  $C_1$  is the subset provided by the

<sup>&</sup>lt;sup>8</sup>Every algorithm can have more virtual channels to implement QoS or other traffic control features, here we are discussing the minimum requirements for deadlock and livelock free routing.

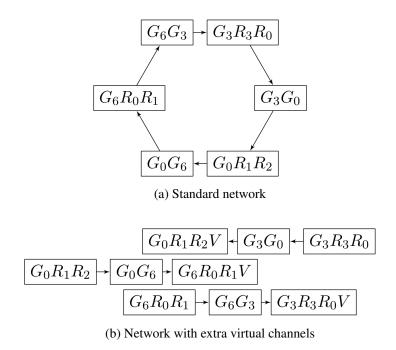

Figure 2.11: Subsets of the total dependency graph for a fully connected dragonfly network. Graph 2.11a depicts a standard configuration with no additional virtual channels. Graph 2.11b depicts a deadlock-free configuration with extra virtual channels (identified by a V letter) for local routing of packets coming from other groups.

star channels and the associated routing subfunction  $R_1$  is the connected and deadlock-free DOR.

#### **2.7.3** Min-routing [2]

This is a near-minimal non adaptive routing algorithm for dragonflies and it can be considered as a base algorithm for adaptive or more complex ones.

Packets in a dragonfly network can be identified by three number:

- **Group index** (G): it indicates the group

- Router index (R): it indicates the router within the group

- Node index (N): it indicates the node within the router

The min-routing algorithm uses a three step process to forward the packet

using the corresponding local or global channel, for better clarity the algorithm can be described using this pseudo code:

```

if (G_node != G_destination)

if (is_connected (G_node, G_destination))

forward_g (G_destination);

else

forward_l (global_to_local (G_destination));

else    if ( R_node != R_destination )

forward_l (R_destination);

else

forward_i (N_destination);

```