# Ingegneria dell'informazione, informatica e statistica

# PhD IN ELECTRONIC ENGINEERING XXIII CYCLE

# SIDE-CHANNEL ATTACKS AND COUNTERMEASURES IN THE DESIGN OF SECURE IC'S DEVICES FOR CRYPTOGRAPHIC APPLICATIONS

Ing. Luca Giancane

Tutor: Prof. Alessandro Trifiletti

# Contents

| 1 | $\mathbf{Intr}$   | oduction                                        | 1        |

|---|-------------------|-------------------------------------------------|----------|

|   | 1.1               | History of Cryptography                         | 1        |

|   | 1.2               | Smart Card                                      | 2        |

|   | 1.3               | An overview on side-channel attacks             | 6        |

|   |                   | 1.3.1 Timing analysis attacks                   | 7        |

|   |                   | 1.3.2 Power analysis attacks                    | 8        |

|   |                   | 1.3.3 Electromagnetic analysis (EMA) attacks    | 9        |

|   |                   |                                                 | 10       |

|   | 1.4               | An Overview on countermeasures                  | 11       |

|   |                   |                                                 | 12       |

|   |                   | 9                                               | 14       |

|   |                   |                                                 | 14       |

|   |                   | v                                               | 16       |

|   |                   |                                                 | 18       |

|   | 1.5               |                                                 | 19       |

|   |                   |                                                 |          |

| 2 | Pow               |                                                 | 21       |

|   | 2.1               | I .                                             | 21       |

|   | 2.2               | ·                                               | 22       |

|   |                   | r v                                             | 24       |

|   |                   | 2.2.2 Differential Power Analysis               | 26       |

|   |                   | 2.2.3 An overview on Correlation Power Analysis | 30       |

| 3 | The               | Supply and Current Measurement 3                | 12       |

| • | 3.1               | supply and carrens measurement                  | -<br>32  |

|   | 3.2               |                                                 | 33       |

|   | $\frac{3.2}{3.3}$ | 1 1                                             | 37       |

|   | 3.4               | 0 1                                             | 37       |

|   | $\frac{3.4}{3.5}$ | <u>.</u>                                        | 39       |

|   | ა. ა              |                                                 | วย<br>43 |

|   |                   | 0 1 11                                          |          |

|   | 9.6               | 0                                               | 46<br>46 |

|   | 3.6               | Conclusions                                     | ₽Ŋ       |

CONTENTS ii

| 4 | $\mathbf{Lea}$ | kage Power Analysis Attack                                        | <b>49</b> |

|---|----------------|-------------------------------------------------------------------|-----------|

|   | 4.1            | Introduction                                                      | 49        |

|   | 4.2            | Review of leakage sources in nanometer CMOS logic gates           | 51        |

|   |                | 4.2.1 Leakage in bit-sliced logic circuits                        | 53        |

|   |                | 4.2.2 Leakage dependence on the Hamming weight: simulation        |           |

|   |                | and experimental results                                          | 53        |

|   | 4.3            | Leakage power analysis: a novel class of side-channel attacks     | 56        |

|   | 4.4            | Practical considerations on LPA attacks                           | 59        |

|   | 4.5            | An analytical model of the correlation coefficient in LPA attacks | 62        |

|   | 4.6            | Examples of LPA attacks                                           | 66        |

|   | 4.7            | Analysis of LPA effectiveness under process variations            | 70        |

|   | 4.8            | Analysis of LPA in presence of DPA resistant logic styles under   |           |

|   |                | process variations                                                | 78        |

|   |                | 4.8.1 Analysis of results for the WDDL logic style                | 79        |

|   |                | 4.8.2 Analysis of results for the TDPL logic style                | 82        |

|   | 4.9            | Conclusions                                                       | 87        |

| 5 | Tra            | nsistor Level Countermeasures                                     | 89        |

|   | 5.1            | Logic families for cryptographic applications                     | 89        |

|   | 5.2            | The 3-state Differential Dynamic Logic Family                     | 92        |

|   |                | 5.2.1 3sDDL cells library: design and simulations                 | 94        |

|   |                | 5.2.2 Interfacing 3sDDL and standard CMOS                         | 98        |

|   | 5.3            | The Three-Phase Dual-Rail Pre-Charge Logic Family                 | 98        |

|   |                | 5.3.1 TDPL flip-flop implementation                               | 103       |

|   |                | 5.3.2 Case study                                                  | 105       |

|   | 5.4            |                                                                   | 107       |

|   |                | 5.4.1 A combinational case study                                  | 112       |

|   |                | 5.4.2 DDPL flip-flop implementation                               |           |

|   |                |                                                                   | 115       |

|   | 5.5            |                                                                   | 117       |

| 6 | Ran            | dom Number Generator                                              | 119       |

|   | 6.1            | RNG and PRNG                                                      | 119       |

|   | 6.2            | Attacking a Random Number Generator                               | 123       |

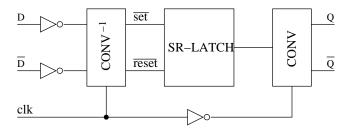

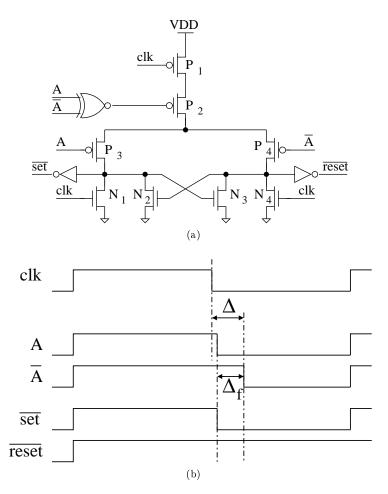

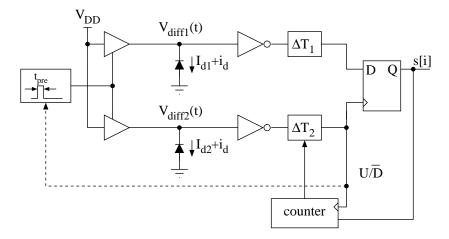

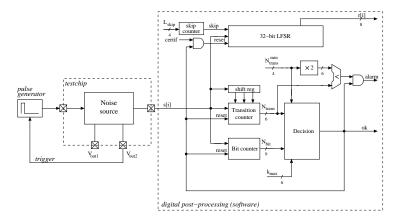

|   |                | 6.2.1 Architecture of the designed RNG                            |           |

|   |                |                                                                   | 126       |

|   |                | 6.2.3 Conclusions                                                 |           |

|   | 6.3            |                                                                   | 130       |

|   |                |                                                                   | 130       |

|   |                |                                                                   | 134       |

|   |                | 6.3.3 Experimental results                                        |           |

|   |                | •                                                                 | 139       |

| 7 | Con            |                                                                   | 140       |

# List of Figures

| 1.1        | An example of banking smart card                                                     | 3  |

|------------|--------------------------------------------------------------------------------------|----|

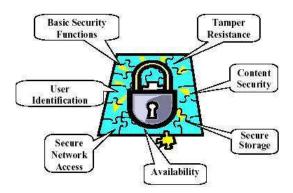

| 1.2        | Common security requirements of embedded system from an end-                         |    |

|            | user perspective                                                                     | 6  |

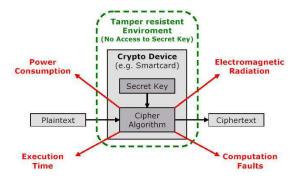

| 1.3        | Side-channel attack types                                                            | 8  |

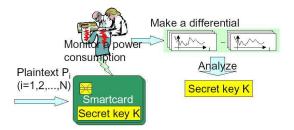

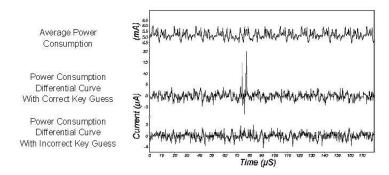

| 1.4        | Differential Power Analysis to discover the secret key                               | 9  |

| 1.5        | DPA behaviour                                                                        | 9  |

| 1.6        | An example of electromagnetic analysis setup                                         | 10 |

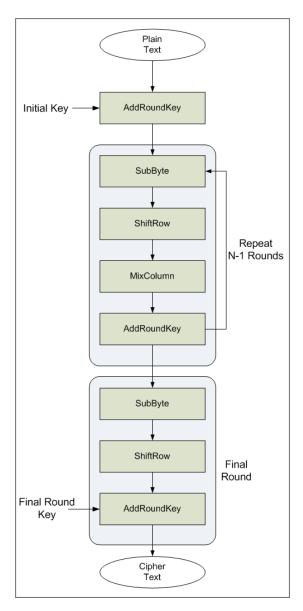

| 1.7        | Basic operations of the Advanced Encryption Standard algorithm.                      | 13 |

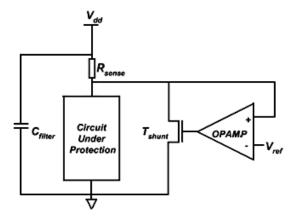

| 1.8        | Block diagram of the suppression circuit                                             | 15 |

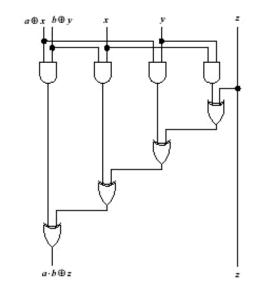

| 1.9        | Example of masked AND                                                                | 17 |

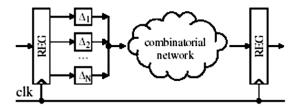

| 1.10       | Pipeline stage with random delays                                                    | 17 |

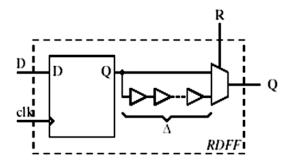

| 1.11       | Random D flip-flop (RDFF)                                                            | 18 |

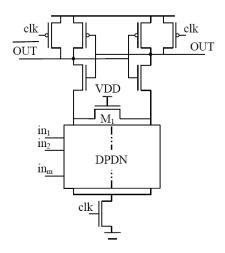

| 1.12       | SABL inverter                                                                        | 19 |

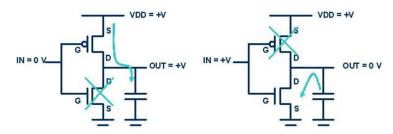

| 2.1        | CMOS inverter power dissipation: 0-1 (left) and 1-0 (right) out-                     |    |

|            | put transition.                                                                      | 22 |

| 2.2        | Power attack in practice                                                             | 23 |

| 2.3        | An SPA trace of an RSA signature operation                                           | 25 |

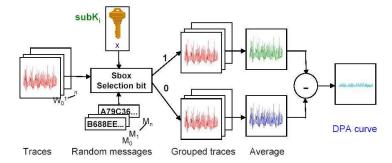

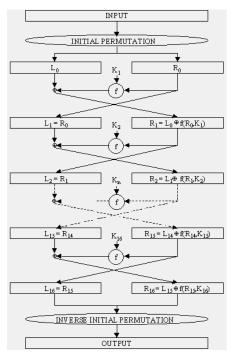

| 2.4        | DPA basic operations                                                                 | 26 |

| 2.5        | Enciphering computation of the DES algorithm.                                        | 28 |

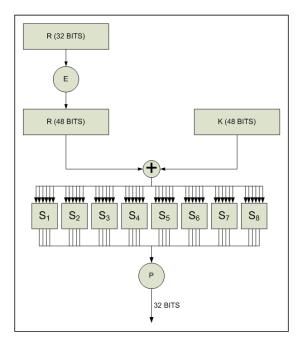

| 2.6        | Calculation of $f(R_{i-1}, K_i)$ in the DES algorithm                                | 29 |

| 2.7        | DPA traces examples                                                                  | 30 |

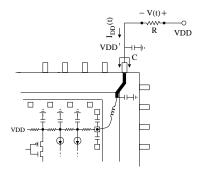

| 3.1        | Model of the power supply interconnection                                            | 33 |

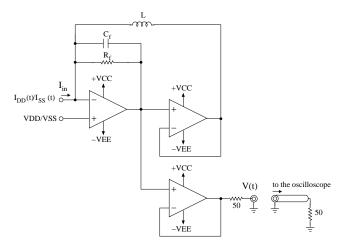

| 3.2        | Supply and current measuring circuit (SCM)                                           | 34 |

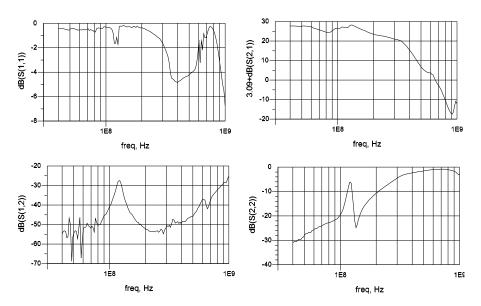

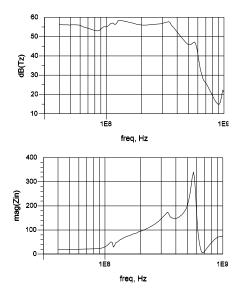

| 3.3        | S-parameters of the supply and current measuring circuit                             | 36 |

| 3.4        | Measured transimpedance gain (above) and input impedance frequency response (below). | 36 |

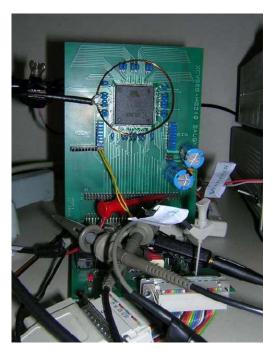

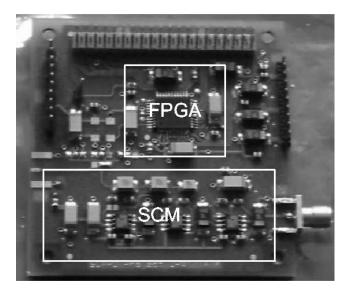

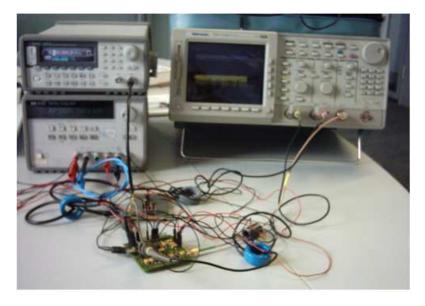

| 3.5        | Prototype board with the SCM and an Altera MAX3000A FPGA.                            | 39 |

| 3.6        | Measurement setup                                                                    | 40 |

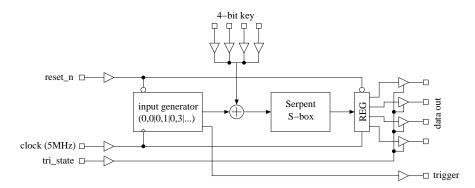

| 3.7        | Circuit used as a case study                                                         | 40 |

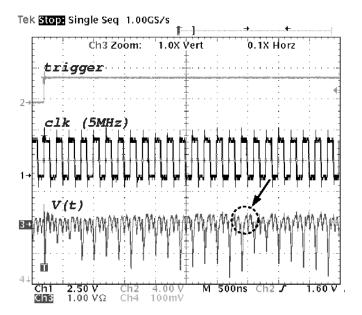

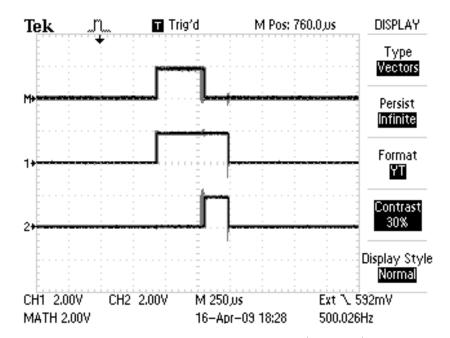

|            | Oscilloscope screenshot.                                                             | 41 |

| 3.8<br>3.9 | •                                                                                    | 41 |

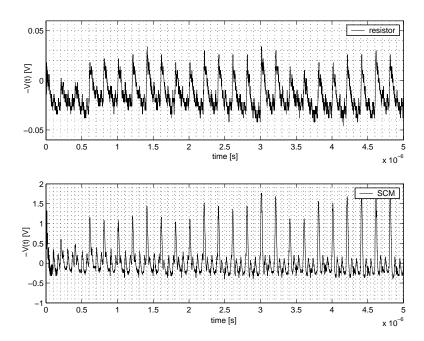

|            | Waveform using a $50\Omega$ resistor (above) vs. SCM (below)                         |    |

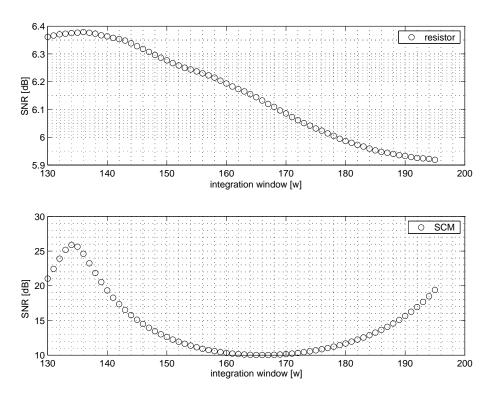

| 3.10       | SNR comparison - resistor (above) vs. SCM (below)                                    | 44 |

LIST OF FIGURES iv

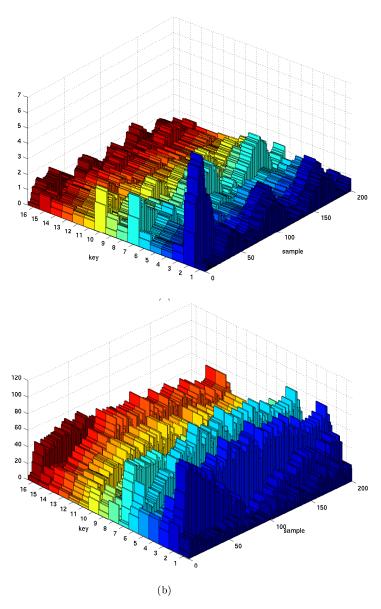

| 3.11  | Result of the differential power analysis using the SCM (a) and       | 4.5 |

|-------|-----------------------------------------------------------------------|-----|

| 0.10  | a $50\Omega$ resistor (b).                                            | 45  |

| 3.12  | Result of the differential power analysis using the SCM (a) and       | 4 = |

|       | a $50\Omega$ resistor (b)                                             | 47  |

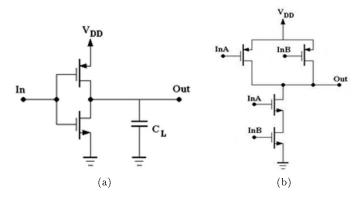

| 4.1   | Schematic of the CMOS Inverter (a) and NAND2 gate (b)                 | 52  |

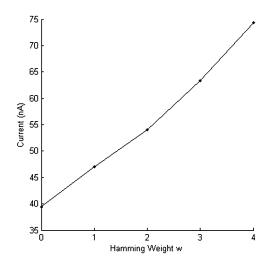

| 4.2   | Simulated leakage vs. Hamming weight in 4-bit registers at $T =$      | 02  |

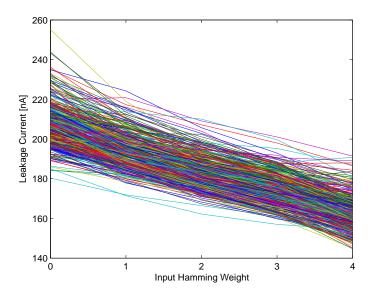

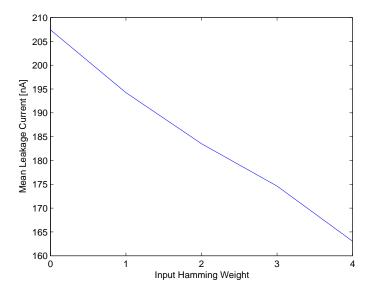

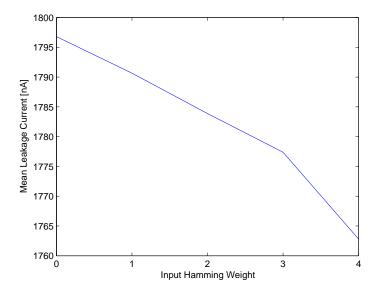

| 1.2   | 27C (65nm technology)                                                 | 55  |

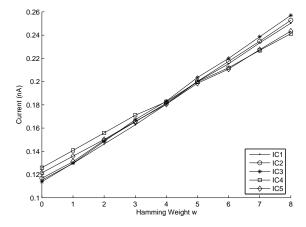

| 4.3   | Measured leakage vs. Hamming weight in an ON Semiconductor            | 00  |

| 1.0   | 8-bit register for five different chips $(T = 43C)$                   | 55  |

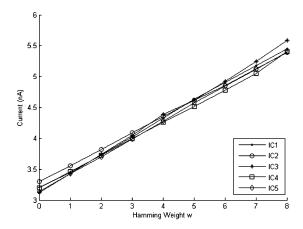

| 4.4   | Measured leakage vs. Hamming weight in an ON Semiconductor            | -   |

|       | 8-bit register for five different chips $(T = 85C)$                   | 56  |

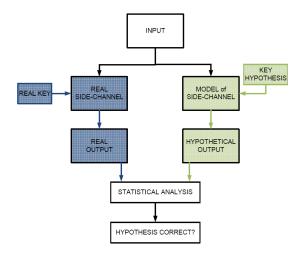

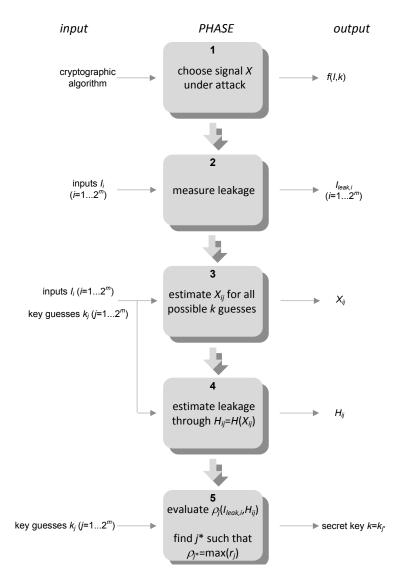

| 4.5   | LPA attack procedure                                                  | 58  |

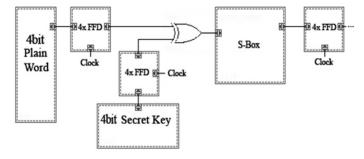

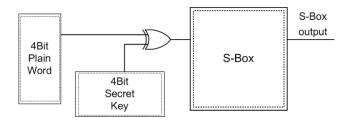

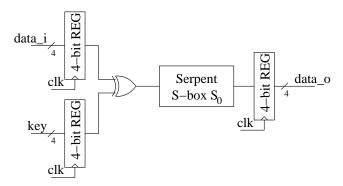

| 4.6   | Crypto core based on Serpent S-Box                                    | 67  |

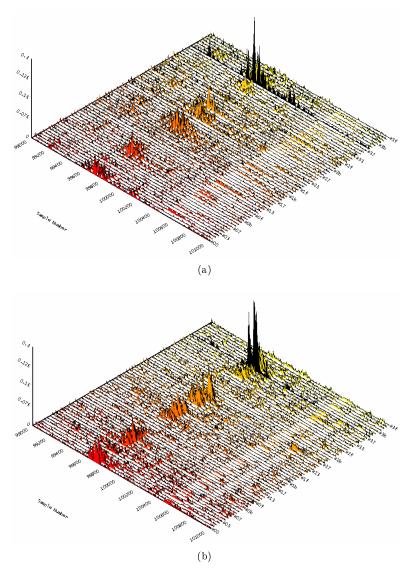

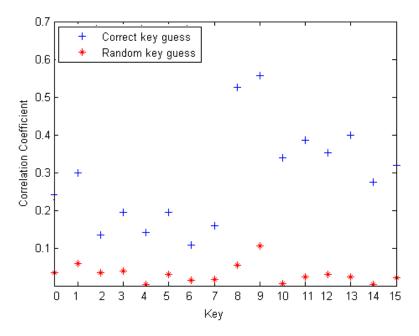

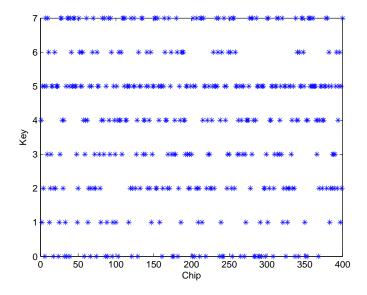

| 4.7   | Correlation coefficient in a simulated attack                         | 68  |

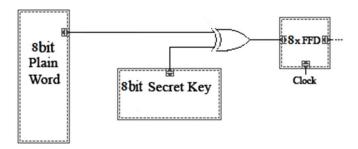

| 4.8   | Cryptographic circuit under experimental attack                       | 68  |

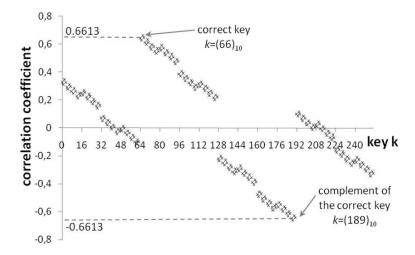

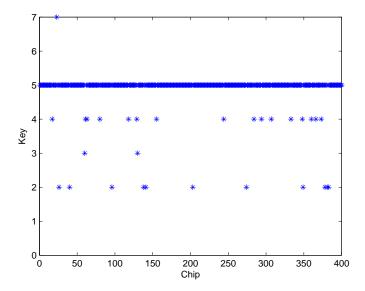

| 4.9   | Correlation coefficient $\rho_i$ for all possible key guesses         | 69  |

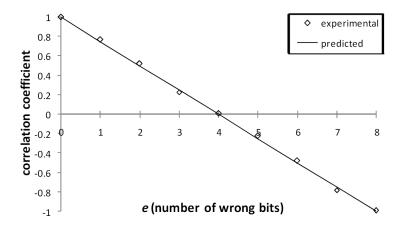

| 4.10  | Experimental and predicted correlation coefficient vs. e              | 70  |

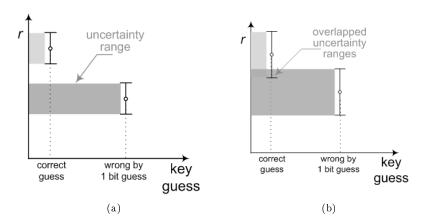

|       | Correlation coefficient statistical distribution under moderate in-   |     |

|       | tradie variations in the case of a successful attack (a) and a un-    |     |

|       | successful attack (b)                                                 | 72  |

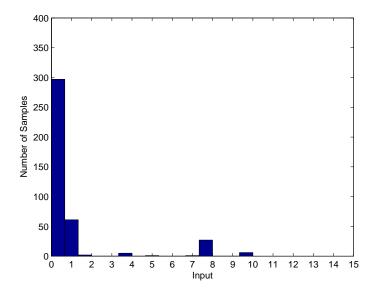

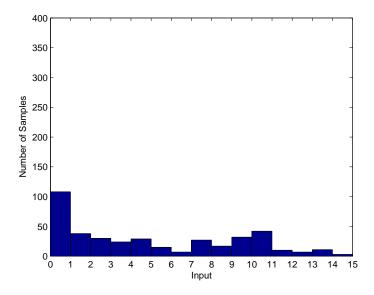

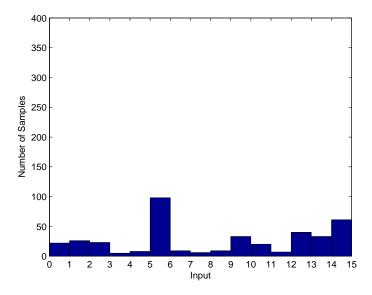

| 4.12  | Histogram distribution of highest leakage current versus the S-       |     |

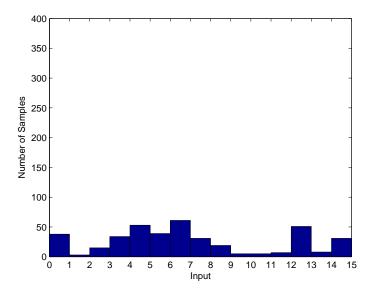

|       | Box input (standard CMOS logic style)                                 | 74  |

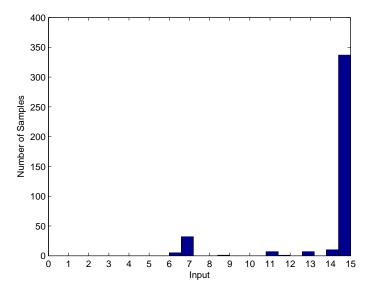

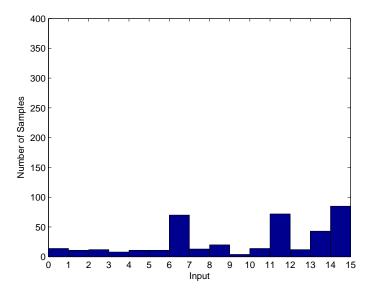

| 4.13  | Histogram distribution of lowest leakage currents versus the S-       |     |

|       | Box input (standard CMOS logic style)                                 | 74  |

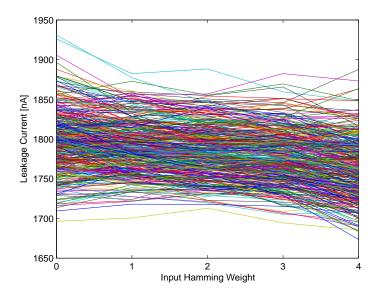

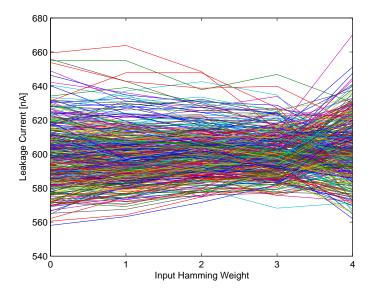

| 4.14  | S-Box leakage current trend versus input Hamming weight for           |     |

|       | standard CMOS logic style                                             | 75  |

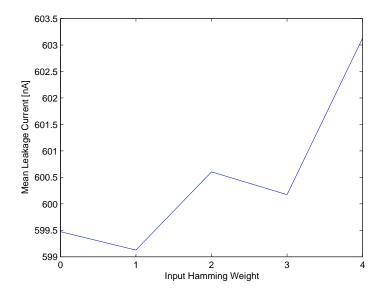

| 4.15  | S-Box leakage current trend versus input Hamming weight for           |     |

|       | standard CMOS logic style (average over 400 Monte Carlo itera-        |     |

|       | tions)                                                                | 75  |

| 4.16  | Crypto core used to perform the LPA attack under process vari-        |     |

|       | ations                                                                | 77  |

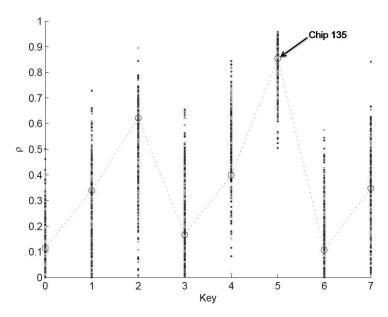

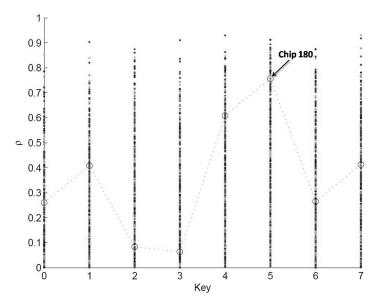

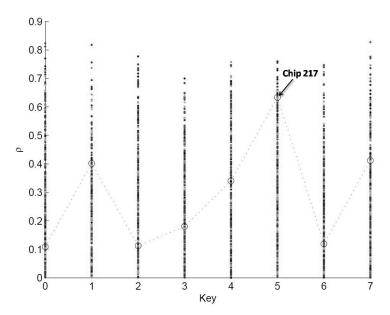

| 4.17  | Correlation coefficients versus the key guess for all the considered  |     |

|       | sample circuits (standard CMOS logic style).                          | 77  |

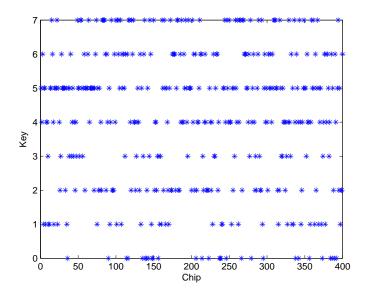

| 4.18  | Plot of the key leading to the highest correlation coefficient versus | -   |

| 4.10  | the considered sample circuit (standard CMOS logic style)             | 78  |

| 4.19  | Histogram distribution of highest leakage current versus the S-       | 0.0 |

| 4.00  | Box input (WDDL logic style)                                          | 80  |

| 4.20  | Histogram distribution of lowest leakage currents versus the S-       | 0.0 |

| 4.0.1 | Box input (WDDL logic style)                                          | 80  |

| 4.21  | S-Box leakage current trend versus input Hamming weight (WDDL         | 01  |

| 4.00  | logic style)                                                          | 81  |

| 4.22  | standard WDDL logic style (average over 400 Monte Carlo iter-         |     |

|       |                                                                       | 81  |

|       | ations)                                                               | OI  |

LIST OF FIGURES

| sample circuits (WDDL logic style).  4.24 Plot of the key leading to the highest correlation continuous the considered sample circuit (WDDL logic style).  4.25 Histogram distribution of highest leakage currents Box input (TDPL logic style).  4.26 Histogram distribution of lowest leakage currents Box input (TDPL logic style).  4.27 S-Box leakage current trend versus input Hamming logic style).  4.28 S-Box leakage current trend versus input Hamming standard TDPL logic style (average over 400 Morntions).  4.29 Correlation coefficients versus the key guess for all sample circuits (TDPL logic style).  4.30 Plot of the key leading to the highest correlation continuous the considered sample circuit (TDPL logic style). | refficient versus                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| <ul> <li>4.24 Plot of the key leading to the highest correlation continuous the considered sample circuit (WDDL logic style)</li> <li>4.25 Histogram distribution of highest leakage current Box input (TDPL logic style)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | refficient versus                                                                                                    |

| the considered sample circuit (WDDL logic style) 4.25 Histogram distribution of highest leakage current Box input (TDPL logic style)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 85  5 versus the S-  6 versus the S-  7 versus the S-  84  85 versus the S-  86  87  88  88  88  88  88  88  88  88  |

| <ul> <li>4.25 Histogram distribution of highest leakage current Box input (TDPL logic style).</li> <li>4.26 Histogram distribution of lowest leakage currents Box input (TDPL logic style).</li> <li>4.27 S-Box leakage current trend versus input Hamming logic style).</li> <li>4.28 S-Box leakage current trend versus input Hamming standard TDPL logic style (average over 400 Mortions).</li> <li>4.29 Correlation coefficients versus the key guess for all sample circuits (TDPL logic style).</li> <li>4.30 Plot of the key leading to the highest correlation coefficient sample circuit (TDPL logic style).</li> <li>5.1 Schematic of the generic 3sDDL gate.</li> </ul>                                                              | t versus the S                                                                                                       |

| Box input (TDPL logic style)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | s versus the S- s versus the S- s weight (TDPL s saing weight for atte Carlo itera- the considered sefficient versus |

| <ul> <li>4.26 Histogram distribution of lowest leakage currents Box input (TDPL logic style).</li> <li>4.27 S-Box leakage current trend versus input Hamming logic style).</li> <li>4.28 S-Box leakage current trend versus input Hamming standard TDPL logic style (average over 400 Mortions).</li> <li>4.29 Correlation coefficients versus the key guess for all sample circuits (TDPL logic style).</li> <li>4.30 Plot of the key leading to the highest correlation coefficients dample circuit (TDPL logic style).</li> <li>5.1 Schematic of the generic 3sDDL gate.</li> </ul>                                                                                                                                                           | s versus the S                                                                                                       |

| Box input (TDPL logic style)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | weight (TDPL  weight for the Carlo iterathe considered  sefficient versus                                            |

| <ul> <li>4.27 S-Box leakage current trend versus input Hamming logic style).</li> <li>4.28 S-Box leakage current trend versus input Hamming standard TDPL logic style (average over 400 Morntions).</li> <li>4.29 Correlation coefficients versus the key guess for all sample circuits (TDPL logic style).</li> <li>4.30 Plot of the key leading to the highest correlation continuous the considered sample circuit (TDPL logic style).</li> <li>5.1 Schematic of the generic 3sDDL gate.</li> </ul>                                                                                                                                                                                                                                           | weight (TDPL                                                                                                         |

| <ul> <li>logic style).</li> <li>4.28 S-Box leakage current trend versus input Hamm standard TDPL logic style (average over 400 Mortions).</li> <li>4.29 Correlation coefficients versus the key guess for all sample circuits (TDPL logic style).</li> <li>4.30 Plot of the key leading to the highest correlation coefficients described the considered sample circuit (TDPL logic style).</li> <li>5.1 Schematic of the generic 3sDDL gate.</li> </ul>                                                                                                                                                                                                                                                                                         | ing weight for the Carlo iterate Carlo iterate the considered the considered sefficient versus                       |

| <ul> <li>4.28 S-Box leakage current trend versus input Hamm standard TDPL logic style (average over 400 Mortions).</li> <li>4.29 Correlation coefficients versus the key guess for all sample circuits (TDPL logic style).</li> <li>4.30 Plot of the key leading to the highest correlation coefficients described the considered sample circuit (TDPL logic style).</li> <li>5.1 Schematic of the generic 3sDDL gate.</li> </ul>                                                                                                                                                                                                                                                                                                                | ning weight for the Carlo itera                                                                                      |

| standard TDPL logic style (average over 400 Mortions).  4.29 Correlation coefficients versus the key guess for all sample circuits (TDPL logic style).  4.30 Plot of the key leading to the highest correlation coefficients the considered sample circuit (TDPL logic style).  5.1 Schematic of the generic 3sDDL gate.                                                                                                                                                                                                                                                                                                                                                                                                                         | nte Carlo itera-<br>                                                                                                 |

| <ul> <li>tions).</li> <li>4.29 Correlation coefficients versus the key guess for all sample circuits (TDPL logic style).</li> <li>4.30 Plot of the key leading to the highest correlation coefficients the considered sample circuit (TDPL logic style).</li> <li>5.1 Schematic of the generic 3sDDL gate.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                      |

| <ul> <li>4.29 Correlation coefficients versus the key guess for all sample circuits (TDPL logic style).</li> <li>4.30 Plot of the key leading to the highest correlation coefficient the considered sample circuit (TDPL logic style).</li> <li>5.1 Schematic of the generic 3sDDL gate.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                              | the considered                                                                                                       |

| sample circuits (TDPL logic style)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                      |

| <ul> <li>4.30 Plot of the key leading to the highest correlation continuous the considered sample circuit (TDPL logic style).</li> <li>5.1 Schematic of the generic 3sDDL gate</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | efficient versus                                                                                                     |

| the considered sample circuit (TDPL logic style).  5.1 Schematic of the generic 3sDDL gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                      |

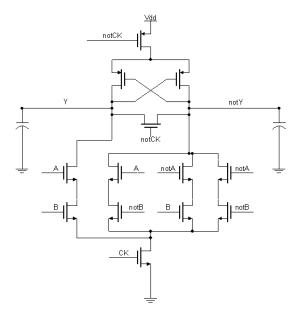

| 5.1 Schematic of the generic 3sDDL gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 80                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 95                                                                                                                   |

| 5.2 XOR-XNOR gate in 3sDDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                      |

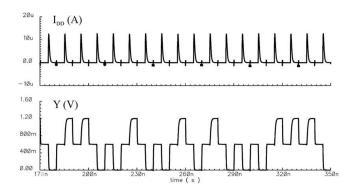

| 5.3 Output voltage and current drawn from the suppl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                      |

| 5.4 Proposed AND-NAND gate schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                      |

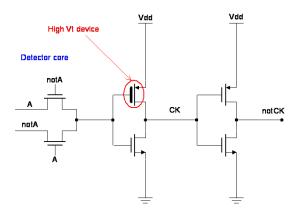

| $5.5 	ext{ } 3^{rd} 	ext{ state detector circuit.} 	ext{ } \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                      |

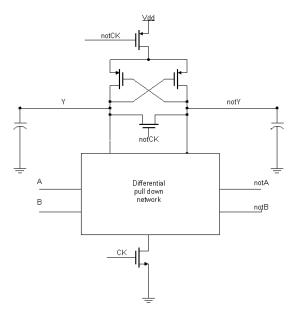

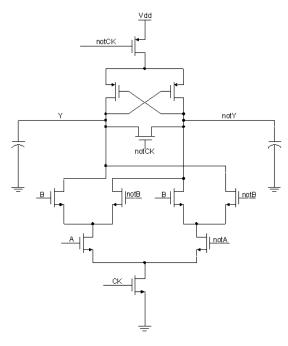

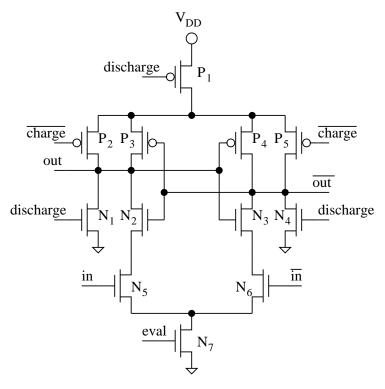

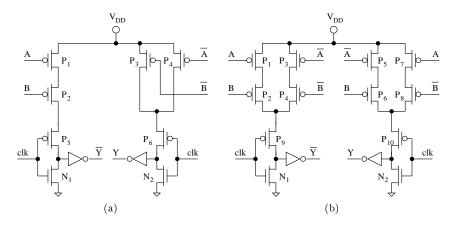

| 5.6 TDPL inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                      |

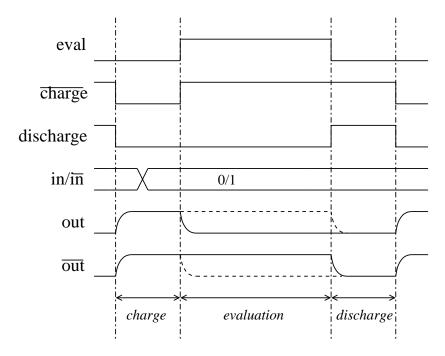

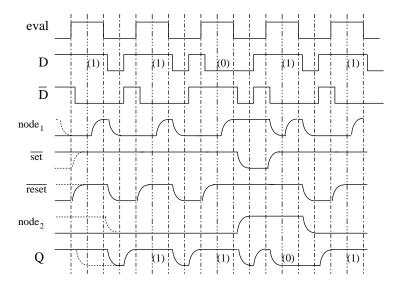

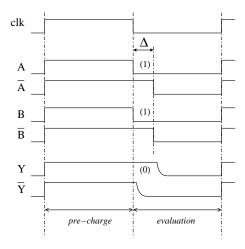

| 5.7 Timing diagram of the TDPL inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 101                                                                                                                  |

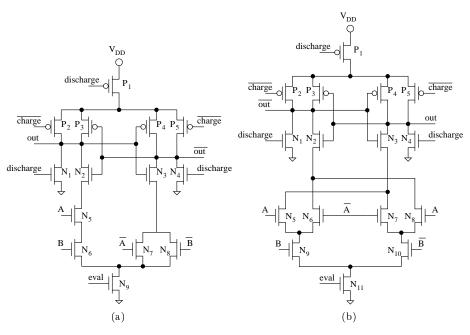

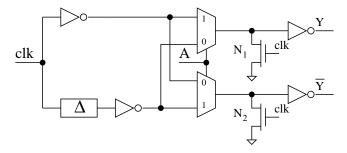

| 5.8 NAND/AND (a) and XOR/NXOR (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 102                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 109                                                                                                                  |

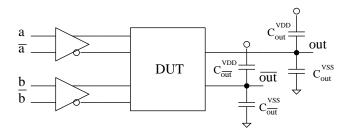

| 5.9 Simulation testbench.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 102                                                                                                                  |

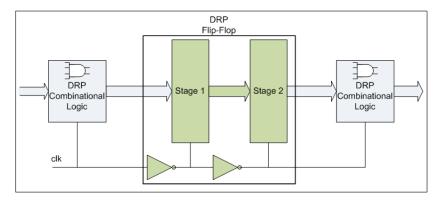

| 5.10 Generic DRP Flip-Flop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                      |

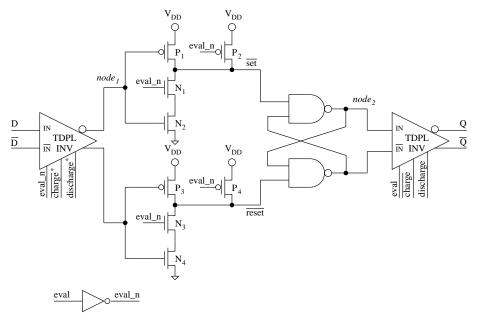

| 5.11 TDPL flip-flop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                      |

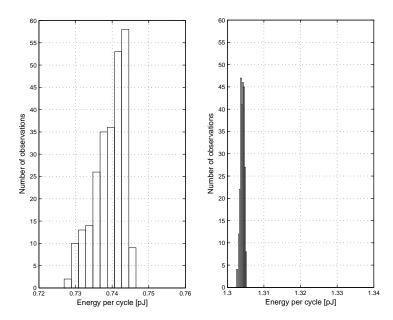

| 5.12 Flip-flop operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 106                                                                                                                  |

| 5.13 Circuit used as case study                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 106                                                                                                                  |

| 5.14 Case study - energy consumption per cycle: S.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                      |

| TDPL (right)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                      |

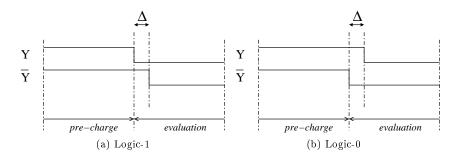

| 5.15 Time domain data encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 108                                                                                                                  |

| $5.16~\mathrm{NAND/AND}$ (a) and $\mathrm{XOR/NXOR}$ (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 108                                                                                                                  |

| 5.17 Timing diagram of the DDPL NAND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 109                                                                                                                  |

| 5.18 CMOS-to-DDPL converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                      |

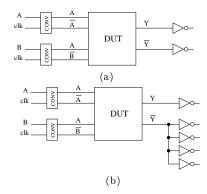

| 5.19 Simulation testbenches: balanced (a) and unbalar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ` /                                                                                                                  |

| 5.20  NAND/AND - superimposition of the power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                      |

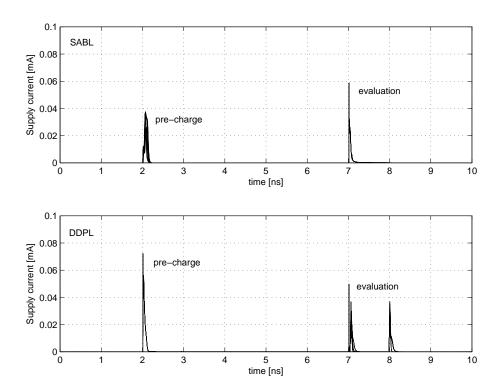

| SABL (above) vs. DDPL (bottom)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 111                                                                                                                  |

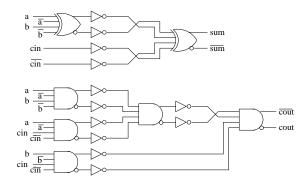

| 5.21 DDPL/SABL full adder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                      |

| 5.22 FULL ADDER - superimposition of the power s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                      |

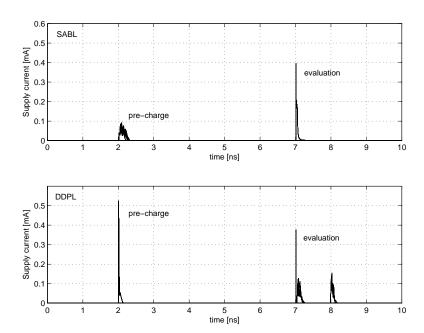

| traces: SABL (above) vs. DDPL (bottom)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 114                                                                                                                  |

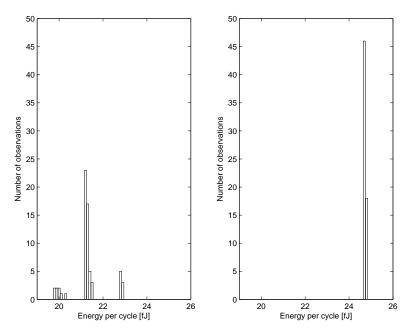

| 5.23 FULLADDER - energy consumption per cycle: S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                      |

| DDPL (right)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                      |

| DDI D (118110)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 115                                                                                                                  |

LIST OF FIGURES vi

| 5.25 DDPL-to-CMOS converter: implementation (a) and timing diagram (b)                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

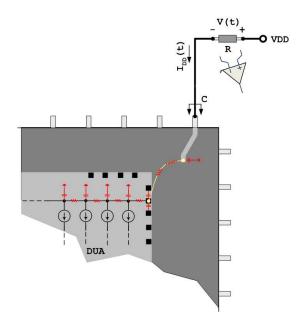

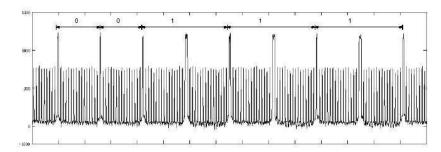

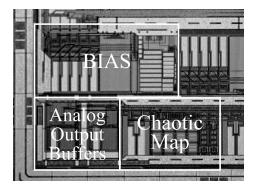

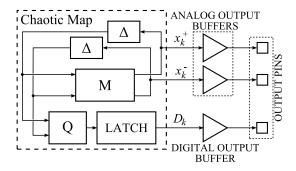

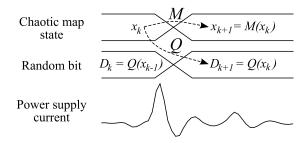

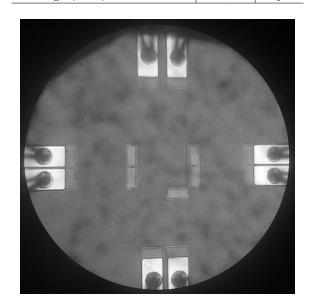

| 6.1 Micro-photograph of the $0.35\mu m$ CMOS prototype (detail) 123 6.2 Basic architecture of the chaos-based RNG prototype. The map state $x_k$ is implemented with the two differential analog voltages                                                             |

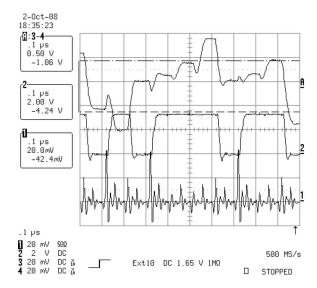

| $x_k^+$ and $x_k^-$ , while the random bit is the digital signal $D_k$ 12-6.3 Prototype measurements. From top to bottom: differential analog internal state of the chaotic map (channel A); generated random bits (channel 2); power supply current (channel 1). The |

| probe used for the the current sensing has a sensitivity of 5mV/mA.128                                                                                                                                                                                                |

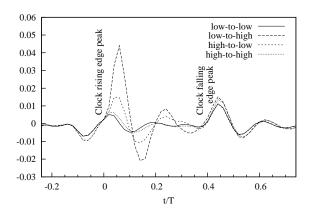

| 6.4 Typical current profile during a transients                                                                                                                                                                                                                       |

| 6.5 Example or the four kinds of dynamic current profile, according to the random output bit transition                                                                                                                                                               |

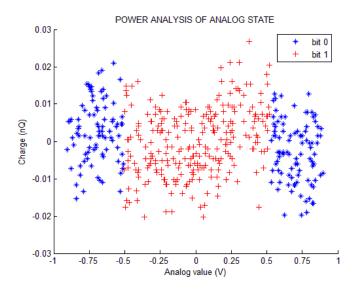

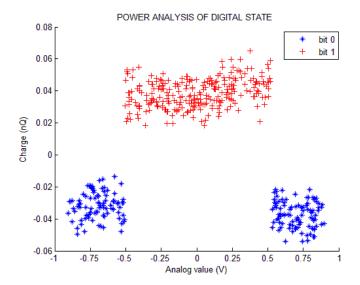

| 6.6 Scatter plot of the charge $\Delta q_k$ required when the successive ran-                                                                                                                                                                                         |

| dom bit $D_{k+1}$ is high and low compared with the internal (analog)                                                                                                                                                                                                 |

| state of the chaotic map $(x_k)$                                                                                                                                                                                                                                      |

| 6.7 Scatter plot of the charge $\Delta q_k$ required when the successive ran-                                                                                                                                                                                         |

| dom bit $D_{k+1}$ is high and low compared with the external (digi-                                                                                                                                                                                                   |

| tal) state of the chaotic map $D_{k+1} = Q(x_k)$                                                                                                                                                                                                                      |

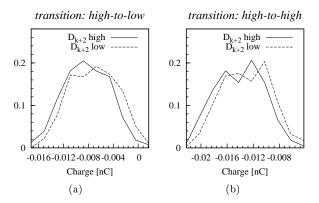

| 6.8 Conditional distribution density of the charge $\Delta q_k$ during a tran-                                                                                                                                                                                        |

| sient, assuming the successive random bit $D_{k+2}$ is high (con-                                                                                                                                                                                                     |

| tinuous line) or low (dotted line), in the case of a high-to-low                                                                                                                                                                                                      |

| random bit transition (case a) and of an unchanged high random                                                                                                                                                                                                        |

| bit (case b, referred to as high-to-high). The distributions are                                                                                                                                                                                                      |

| obtained with a 10 bins histogram of frequencies                                                                                                                                                                                                                      |

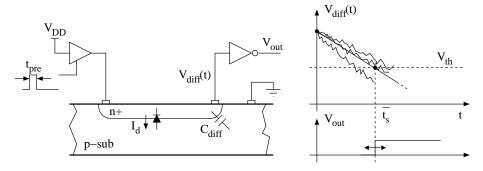

| 6.9 Noisy discharge of a reverse biased p-n junction                                                                                                                                                                                                                  |

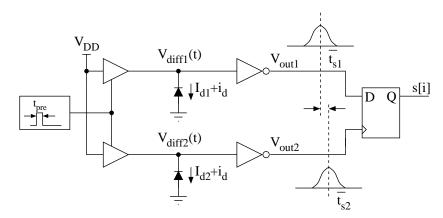

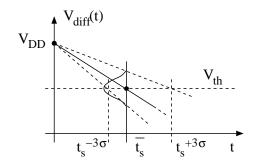

| 6.10 Generation of a random bit using two $n+$ diffusions 135                                                                                                                                                                                                         |

| 6.11 Feedback loop to cancel the output sequence bias                                                                                                                                                                                                                 |

| 6.12 Integration time variance                                                                                                                                                                                                                                        |

| 6.13 Testchip micro-photograph                                                                                                                                                                                                                                        |

| 6.14 RBG testchip and digital post-processing                                                                                                                                                                                                                         |

| 6.15 Oscilloscope screenshot (chip $\#20$ )                                                                                                                                                                                                                           |

## Chapter 1

### Introduction

#### 1.1 History of Cryptography

The most ancient use of coding is probably that one found on the "lacedaemonian scytale" (400 b.C.), a stick on which a leather tape was bundled up; on the tap one wrote for columns parallel to the axis of the stick, letter for letter, the secret text. Removed the tape from the stick, the text was transposed in regular but sufficient way in order to avoid the reading without a second stick equal to the first one.

In the ancient time well-known was hectographed code, in which each letter was ciphered with a number couple, or codes in which each letter was replaced with another letter.

In 800 a.d. Al-Kindi, an Arab mathematician, devised new methods of breaking ciphers of the Qur'an. It was the most fundamental cryptanalytic advance until Second World War. Al-Kindi wrote a book on cryptography entitled "Manuscript for the Deciphering Cryptographic Messages", in which he described the first cryptanalysis techniques.

In Europe, cryptography became (secretly) more important as a consequence of political competition and religious revolution. Although cryptography has a long and complex history, it wasn't until the 19th century that it developed anything more than ad hoc approaches to either encryption or cryptanalysis (the science of finding weaknesses in crypto systems).

The First World War is the first great war after the invention of the radio; this new mass media if from one side allowed to transmit messages practically in an instantaneous way, on the other side it was much exposed to the interception of the enemy: to capture a courier that brought an important message was more difficult than to intercept a radio transmission. For this reason cryptographic became very important and the first cryptography machines (with the relative algorithms) were built.

But it was during the Second World War that research in cryptography experienced a major acceleration and when the war ended cryptography was

studied in many fields, from mathematics to electronics. In 1976, the algorithm Lucifer developed by Horst Feistel at IBM, was officially adopted with the name DES ( $Data\ Encryption\ Standard$ ) as the first standard encryption algorithm, encouraging the business community to make use of cryptography to secure communication and business transactions. The same year, Whitfield Diffie, Martin Hellman and Ralph Merkle announced a method to solve the key distribution problem introducing the concept of asymmetric encryption and forming the basis for public key cryptography. Unfortunately, they did not succeed to find a one-way function necessary to implement their method. In 1977, Ronald Rivest, Adi Shamir and Leonard Adleman, mathematicians at the MIT laboratory for computer science, introduced the RSA, an asymmetric encryption algorithm which finally allowed public key cryptography to be used in practice.

Nowadays cryptography is used to protect personal data: using a mobile telephone, withdrawing money from a bank, storing medical data and so on. All these operations are based on the use of a pocket-sized card with an embedded integrated circuit, commonly named *smart card* or *chip card*.

The interest in secure devices has led to a great numbers of research works on new attacks, on one side, and new countermeasures on the other side. Different levels are considered starting from the algorithms to hardware realizations. In particular, since the introduction of side-channel attacks (physical quantities related with the key), many works have been published on how to exploit or avoid side-channel information leakage, i.e. information that can be retrieved from a cryptographic device by measuring a quantity not directly involved in the secret information treatment. Essentially from 20th century, cryptography makes extensive use of mathematics and engineering, including aspects of physics, information theory, computational complexity, statistics, combinatorial, abstract algebra, number theory, by involving more and more different aspects of sciences in general.

#### 1.2 Smart Card

A smart card consists of a plastic support in which a microchip is inserted; the interface between microchip and external world can be a series of contacts (in this case it is properly named contact-based smart card) or an antenna (contact-less smart card) or both (dual-interface smart card).

Probably the beginning of the story of Smart Card is to be found in the novel "La nuit des temps" (The drawn of time), in which the french science-fiction writer René Barjavel wrote in 1968 about a magic ring used as a key by Gondas, a very old and highly advanced civilization. The magic ring was empowered with memory and communications:

"... Every time a Gonda wanted something new, [...], he would pay with his key. He would bend his middle finger, would enter his key in a location chosen at this effect and his account at the central computer would immediately be reduced by the value of the merchandise or the request service ..."

Figure 1.1: An example of banking smart card.

The proliferation of simple plastic cards started in the USA in the early 1950s. The low price of the synthetic material PVC made it possible to produce robust, durable plastic cards that were much more suitable for everyday use than the paper and cardboard cards previously used, which could not adequately withstand mechanical stresses and climatic effects.

The entry of Visa and MasterCard into the field led to a very rapid proliferation of 'plastic money' in the form of credit cards. This occurred first in the USA, with Europe and the rest of the world following a few years later. Today, credit cards allow travelers to shop without cash everywhere in the world.

At first, the functions of these cards were quite simple. They served as data storage media that were secure against forgery and tampering. General information, such as the card issuer's name, was printed on the surface, while personal data elements, such as the cardholder's name and the card number, were embossed. Many cards also had a signature panel where the cardholder would sign his or her name for reference. The embossed characters on the card can be transferred to paper using simple, inexpensive devices, and they can also be easily read visually (by humans).

The first improvement consisted of a magnetic stripe on the back of the card. The fundamental disadvantage of embossed cards is that their use creates a flood of paper receipts, which are expensive to process. One remedy for this problem is to digitally encode the card data on a magnetic stripe located on the back of the card. Although the storage capacity of the magnetic stripe is only about 1000 bits, which is not very much, it is nevertheless more than sufficient for storing the information contained in the embossing. In this way paperbased transactions were replaced by electronic data processing. This required a different method to be used for user identification, which previously employed the user's signature. The method that has come into widespread general use involves a secret personal identification number (PIN) that is compared with a reference number. The reader is surely familiar with this method from using bank machines (automated teller machines). The main drawback of magneticstripe technology is that the stored data can be altered very easily. Manipulating embossed characters requires at least a certain amount of manual dexterity, and such manipulations be easily detected by a trained eye. By contrast, the data recorded on the magnetic stripe can be altered relatively easily using a standard read/write device, and it is difficult to afterwards prove that the data have been altered. Furthermore, magnetic-stripe cards are often used in automated equipment in which visual inspection is not possible, such as cash dispensers. Most systems that employ magnetic-stripe cards thus use online connections to the system's host computer for reasons of security, even though this generates significant costs for the necessary data transmissions. In order to reduce costs, it is necessary to find solutions that allow card transactions to be executed offline without endangering the security of the system.

The development of the smart card, combined with the expansion of electronic data-processing systems, has created completely new possibilities for devising such solutions. Thanks to enormous progress in microelectronics, in the 1970s it was possible to integrate data storage and processing logic on a single silicon chip measuring a few square millimeters. Smart card characteristic feature is an integrated circuit embedded in the card, which has components for transmitting, storing and processing data. The data can be transmitted using either contacts on the surface of the card or electromagnetic fields, without any contacts.

The first patents were in 1968 and 1970 but the first real progress in the development of smart cards came when Roland Moreno registered his smart card patents in France in 1974. The great breakthrough was achieved in 1984, when the French PTT (postal and telecommunications services agency) successfully carried out a field trial with telephone cards. In this field trial, smart cards immediately proved to meet all expectations with regard to high reliability and protection against manipulation. Significantly, this breakthrough for smart cards did not come in an area where traditional cards were already used, but in a new application.

One of the most important advantages of smart cards is that their stored data can be protected against unauthorized access and manipulation. Such confidential data can be processed only internally by the chip's processing unit. In principle, both hardware and software mechanisms can be used to restrict the use of the storage functions of writing, erasing and reading data and tie them to specific conditions. This makes it possible to construct a variety of security mechanisms, which can also be tailored to the specific requirements of a particular application. In combination with the ability to compute cryptographic algorithms, this allows smart cards to be used to implement convenient security modules that can be carried by users at all times, for example in a purse or wallet. Some additional advantages of smart cards are their high level of reliability and long life compared with magnetic-stripe cards, whose useful life is generally limited to one or two years.

Smart cards can be divided into two groups, which differ in both functionality and price: memory cards and microprocessor cards. Presently, both memory cards and microprocessor cards are available as contactless cards.

In a memory cards the data needed by the application are stored, as the name suggests, in a memory, which is usually EEPROM. Access to the memory

is controlled by the security logic, which in the simplest case consists only of write protection or erase protection for the memory or certain memory regions. However, there are also memory chips with more complex security logic that can also perform simple encryption. The functionality of memory cards is usually optimized for a particular application. Although this severely restricts the flexibility of the cards, it makes them quite inexpensive. Memory cards are typically used for prepaid telephone cards and health insurance cards.

In a microprocessor card the heart of the chip, as the name suggests, is a processor, which is usually surrounded by four additional functional blocks: mask ROM, EEPROM, RAM and an I/O port. The mask ROM contains the chip's operating system, which is 'burned in' when the chip is manufactured. The content of the ROM is thus identical for all the chips of a production run, and it cannot be changed during the chip's lifetime. The EEPROM is the chip's non-volatile memory. Data and program code can be written to and read from the EEPROM under the control of the operating system. The RAM is the processor's working memory. This memory is volatile, so all the data stored in it are lost when the chip's power is switched off. The serial I/O interface usually consists only of a single register, via which data are transferred bit by bit. Microprocessor cards are very flexible in use. In the simplest case, they contain a program optimized for a single application, so they can only be used for this particular application. However, modern smart card operating systems allow several different applications to be integrated into a single card. In this case, the ROM contains only the basic components of the operating system, with the application-specific part of the operating system being loaded into the EEPROM only after the card has been manufactured. Recent developments even allow application programs to be loaded into a card after it has already been personalized and issued to the cardholder. Special hardware and software measures are used to prevent the security conditions of the individual applications from being violated by this capability. Hardware attacks and, on the other hand, hardware countermeasures that will be proposed in this work are all related to applications based on microprocessor smart cards.

Finally, contactless cards, in which energy and data are transferred without any electrical contact between the card and the terminal, have achieved the status of commercial products in the last few years. As contactless cards can work at a distance from the terminal ranging from few centimeters to a meter, this means that such cards do not necessarily have to be held in the user's hand during use, but can remain in the user's purse or wallet. Contactless cards are thus particularly suitable for applications in which persons or objects should be quickly identified such as access control, local public transportation, ski passes, airline tickets. However, there are also applications where operation over a long distance could cause problems and should thus be prevented, as for example for electronic purse application.

Figure 1.2: Common security requirements of embedded system from an enduser perspective.

#### 1.3 An overview on side-channel attacks

Information technology is evolving at an amazing pace. Personal computers, fax machines, pagers, and mobile phones are in the hands of millions of people worldwide. Similarly, interest in smart card technology has soared in the 1990's, and by the year 2000 the number and variety of smart card-based applications exploded around the world.

In an increasing number of large and important smart card-based systems, from pay-TV through GSM mobile phones and prepaid gas meters to electronic wallets, smart cards are used by millions of cardholders worldwide in more than 90 countries, primarily in Europe and the Far East, processing point-of-sale transactions, managing records, and protecting computers and secure facilities.

For these reasons information engineers have developed an increasing interest in the tamper resistance properties of smart cards and other special purpose security processors. Tamper resistance is not absolute: an attacker with access to semiconductor test equipment can retrieve key material from a smart card controller by direct observation and manipulation of the chip's components. It is generally believed that, given sufficient investment, any chip-sized tamper resistant device can be penetrated in this way.

This is the reason for the increasing interest in new attack methods on one side and in new countermeasures and new cryptographic algorithms on the other side.

Cryptographic algorithms are building blocks of many security protocols and can be implemented both in software and hardware. Software solutions are cheaper and more flexible, while hardware implementations provide higher speed and intrinsic security. A trade-off in cost and speed can be achieved by hardware-software co-design.