MDPI

Article

# The Power Board of the KM3NeT Digital Optical Module: Design, Upgrade, and Production

Sebastiano Aiello<sup>1</sup>, Arnauld Albert<sup>2,3</sup>, Sergio Alves Garre<sup>4</sup>, Zineb Aly<sup>5</sup>, Antonio Ambrosone <sup>6,7</sup>, Fabrizio Ameli <sup>8</sup>, Michel Andre <sup>9</sup>, Eleni Androutsou <sup>10</sup>, Mancia Anguita 11, Laurent Aphecetche 12, Miguel Ardid 130, Salva Ardid 130, Hicham Atmani 14, Julien Aublin 15, Francesca Badaracco 16, Louis Bailly-Salins 17, Zuzana Bardacova 18,19, Bruny Baret 15, Adriana Bariego 4, Suzan Basegmez Du Pree 20, Yvonne Becherini 15, Meriem Bendahman 14,15, Francesco Benfenati 21,22, Marouane Benhassi <sup>6,23</sup>, David M. Benoit <sup>24</sup>, Edward Berbee <sup>20</sup>, Vincent Bertin <sup>5</sup>, Simone Biagi <sup>25</sup>, Markus Boettcher <sup>26</sup>, Danilo Bonanno <sup>25</sup>, Jihad Boumaaza <sup>14</sup>, Mohammed Bouta <sup>27</sup>, Mieke Bouwhuis <sup>20</sup>, Cristiano Bozza <sup>6,28</sup>, Riccardo Maria Bozza <sup>6,7</sup>, Horea Branzas <sup>29</sup>, Felix Bretaudeau <sup>12</sup>, Ronald Bruijn <sup>20,30</sup>, Jurgen Brunner <sup>5</sup>, Riccardo Bruno <sup>1</sup>, Ernst Jan Buis <sup>20,31</sup>, Raffaele Buompane <sup>6,23</sup>, Jose Busto <sup>5</sup> Barbara Caiffi 16, David Calvo 40, Stefano Campion 8,32, Antonio Capone 8,32, Francesco Carenini <sup>21,22</sup>, Víctor Carretero <sup>4</sup>, Théophile Cartraud <sup>15</sup>, Paolo Castaldi <sup>21,33</sup>, Vincent Cecchini <sup>4</sup>, Silvia Celli <sup>8,32</sup>, Luc Cerisy <sup>5</sup>, Mohamed Chabab <sup>34</sup>, Michael Chadolias 35, Cèdric Champion 15, Andrew Chen 36, Silvio Cherubini 25,37, Tommaso Chiarusi <sup>21</sup>, Marco Circella <sup>38</sup>, Rosanna Cocimano <sup>25</sup>, João Coelho <sup>15</sup>, Alexis Coleiro 15, Stephane Colonges 15, Rosa Coniglione 25, Paschal Coyle 5, Alexandre Creusot 15, Giacomo Cuttone 25, Richard Dallier 12, Yara Darras 35, Antonio De Benedittis <sup>6</sup>, Maarten de Jong <sup>20,39</sup>, Paul de Jong <sup>20,30</sup>, Bianca De Martino <sup>5</sup>, Els de Wolf <sup>20,30</sup>, Valentin Decoene <sup>12</sup>, Riccardo Del Burgo <sup>6</sup>, Ilaria Del Rosso <sup>21,22</sup>, Umberto Maria Di Cerbo <sup>6</sup>, Letizia Stella Di Mauro <sup>25</sup>, Irene Di Palma <sup>8,32</sup>, Antonio Diaz 110, Cristian Díaz Martín 11, Dídac Diego-Tortosa 250, Carla Distefano 25, Alba Domi <sup>35</sup>, Corinne Donzaud <sup>15</sup>, Damien Dornic <sup>5</sup>, Manuel Dörr <sup>40</sup>, Evangelia Drakopoulou <sup>10</sup>, Doriane Drouhin <sup>2,3</sup>, Rastislav Dvornický <sup>19</sup>, Thomas Eberl <sup>35</sup>, Eliska Eckerova <sup>18,19</sup>, Ahmed Eddymaoui <sup>14</sup>, Maximilian Eff <sup>15</sup>, Imad El Bojaddaini 27, Sonia El Hedri 15, Alexander Enzenhöfer 5, Giovanna Ferrara 25, Miroslav Filipovic 41, Francesco Filippini 21,22, Dino Franciotti 25, Luigi Antonio Fusco 6,28, Omar Gabella 42, Jean-Louis Gabriel 43, Silvia Gagliardini 8, Tamas Gal 35, Juan García Méndez 13, Alfonso Andres Garcia Soto 4, Clara Gatius Oliver <sup>20</sup>, Nicole Geißelbrecht <sup>35</sup>, Houria Ghaddari <sup>27</sup>, Lucio Gialanella <sup>6,23</sup>, Brad K. Gibson <sup>24</sup>, Emidio Giorgio <sup>25</sup>, Isabel Goos <sup>15</sup>, Pranjupriya Goswami <sup>15</sup>, Damien Goupilliere <sup>17</sup>, Sara Rebecca Gozzini <sup>4</sup>, Rodrigo Gracia <sup>35</sup>, Kay Graf <sup>35</sup>, Carlo Guidi 16,44, Benoît Guillon 17, Miguel Gutiérrez 45, Aart Heijboer 20, Amar Hekalo 40, Lukas Hennig 35, Juan-Jose Hernandez-Rey 4, Walid Idrissi Ibnsalih 6, Giulia Illuminati <sup>21,22</sup>, Peter Jansweijer <sup>20</sup>, Bouke Jisse Jung <sup>20</sup>, Piotr Kalaczyński <sup>46,47</sup>, Oleg Kalekin 35, Uli Katz 35, Amina Khatun 19, Giorgi Kistauri 48,49, Claudio Kopper 35, Antoine Kouchner 15,50, Vincent Kueviakoe 20, Vladimir Kulikovskiy 16, Ramaz Kvatadze <sup>49</sup>, Marc Labalme <sup>17</sup>, Robert Lahmann <sup>35</sup>, Giuseppina Larosa <sup>25</sup>, Chiara Lastoria <sup>5</sup>, Alfonso Lazo <sup>4</sup>, Sebastien Le Stum <sup>5</sup>, Grégory Lehaut <sup>17</sup>, Emanuele Leonora 1, Nadja Lessing 4, Giuseppe Levi 21,22, Miles Lindsey Clark 15, Pietro Litrico 25, Fabio Longhitano 10, Jerzy Mańczak 4, Jhilik Majumdar 20, Leonardo Malerba 16, Fadahat Mamedov 18, Alberto Manfreda 6, Martina Marconi 16,44, Annarita Margiotta <sup>21,22</sup>, Antonio Marinelli <sup>6,7</sup>, Christos Markou <sup>10</sup>, Lilian Martin <sup>12</sup>, Juan Antonio Martínez-Mora <sup>13</sup>, Fabio Marzaioli <sup>6,23</sup>, Massimo Mastrodicasa <sup>8,32</sup>, Stefano Mastroianni <sup>6</sup>, Sandra Miccichè <sup>25</sup>, Gennaro Miele <sup>6,7</sup>, Pasquale Migliozzi <sup>6</sup>, Emilio Migneco <sup>25</sup>, Saverio Minutoli <sup>16</sup>, Maria Lucia Mitsou <sup>6</sup>, Carlos Maximiliano Mollo <sup>6</sup>, Lizeth Morales Gallegos <sup>6,23</sup>, Michele Morga <sup>38</sup>,

Citation: Aiello, S.; Albert, A.; Garre, S.A.; Aly, Z.; Ambrosone, A.; Ameli, F.; Andre, M.; Androutsou, E.; Anguita, M.; Aphecetche, L.; et al. The Power Board of the KM3NeT Digital Optical Module: Design, Upgrade, and Production. *Electronics* **2024**, *13*, 2044. https://doi.org/10.3390/ electronics13112044

Academic Editors: Elias Stathatos and Flavio Canavero

Received: 14 March 2024 Revised: 6 May 2024 Accepted: 12 May 2024 Published: 24 May 2024

Copyright: © 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Electronics **2024**, 13, 2044 2 of 17

Abdelilah Moussa <sup>27</sup>, Ivan Mozun Mateo <sup>51,52</sup>, Rasa Muller <sup>20</sup>, Paolo Musico <sup>16</sup>, Maria Rosaria Musone 6,23, Mario Musumeci 25, Sergio Navas 45, Amid Naverhoda 38, Carlo Alessandro Nicolau 8, Bhuti Nkosi 36, Brían Ó Fearraigh 20,30, Veronica Oliviero <sup>6,7</sup>, Angelo Orlando <sup>25</sup>, Enzo Oukacha <sup>15</sup>, Daniele Paesani <sup>25</sup>, Juan Palacios González <sup>4</sup>, Gogita Papalashvili <sup>48</sup>, Vittorio Parisi <sup>16,44</sup>, Emilio Pastor <sup>4</sup>, Alice Paun 29, Gabriela Emilia Pavalas 29, Giuliano Pellegrini 210, Santiago Pena Martinez 15, Mathieu Perrin-Terrin 50, Jerome Perronnel 17, Valentin Pestel <sup>52</sup>, Rebekah Pestes <sup>15</sup>, Paolo Piattelli <sup>25</sup>, Chiara Poirè <sup>6,28</sup>, Vlad Popa <sup>29</sup>, Thierry Pradier <sup>2</sup>, Jorge Prado <sup>4</sup>, Sara Pulvirenti <sup>25</sup>, Gilles Quemener <sup>17</sup>, Carlos Quiroz 13, Ushak Rahaman 4, Nunzio Randazzo 1, Richard Randriatoamanana 12, Soebur Razzaque 53, Immacolata Carmen Rea 6, Diego Real 4,\* D, Giorgio Riccobene 25, Joshua Robinson 26, Andrey Romanov 16,44, Adrian Saina 4, Francisco Salesa Greus 4,23 D, Dorothea Franziska Elisabeth Samtleben <sup>20,39</sup>, Agustín Sánchez Losa <sup>4</sup>D, Simone Sanfilippo <sup>25</sup>, Matteo Sanguineti <sup>16,44</sup>, Claudio Santonastaso <sup>6,54</sup>, Domenico Santonocito 25, Piera Sapienza 25, Jan-Willem Schmelling 20, Jutta Schnabel <sup>35</sup>, Johannes Schumann <sup>35</sup>, Hester Schutte <sup>26</sup>, Jordan Seneca <sup>20</sup>, Nour-Eddine Sennan 27, Bastian Setter 35, Irene Sgura 38, Rezo Shanidze 48, Ankur Sharma 15, Yury Shitov 18, Fedor Šimkovic 190, Andreino Simonelli 6, Anna Sinopoulou <sup>1</sup>, Mikhail Smirnov <sup>35</sup>, Bernardino Spisso <sup>6</sup>, Maurizio Spurio <sup>21,22</sup>, Dimitris Stavropoulos <sup>10</sup>, Ivan Štekl <sup>18</sup>, Mauro Taiuti <sup>16,44</sup>, Yahya Tayalati <sup>14</sup>, Hannes Thiersen <sup>26</sup>, Iara Tosta e Melo <sup>1,37</sup>, Efi Tragia <sup>10</sup>, Benjamin Trocme <sup>15</sup>, Vasileios Tsourapis <sup>10</sup>, Ekaterini Tzamariudaki <sup>10</sup>, Antonin Vacheret <sup>17</sup>, Angel Valer Melchor 20, Veronica Valsecchi 25, Vincent van Beveren 20, Thijs van Eeden <sup>20</sup>, Daan van Eijk <sup>20</sup>, Véronique Van Elewyck <sup>15,50</sup>, Hans van Haren <sup>55</sup>, Godefroy Vannoye<sup>5</sup>, George Vasileiadis<sup>42</sup>, Francisco Vazquez De Sola<sup>20</sup>, Cedric Verilhac 15, Alessandro Veutro 8,32, Salvatore Viola 25, Daniele Vivolo 6,23, Joern Wilms <sup>56</sup>, Harold Yepes Ramirez <sup>13</sup>, Giorgos Zarpapis <sup>10</sup>, Sandra Zavatarelli <sup>16</sup>, Angela Zegarelli 8,32, Daniele Zito 25, Juan de Dios Zornoza 40, Juan Zuñiga 4 and Natalia Zywucka 26

- <sup>1</sup> INFN, Sezione di Catania, Via Santa Sofia 64, Catania, 95123 Italy; sebastiano.aiello@ct.infn.it (S.A.); emanuele.leonora@ct.infn.it (E.L.); fabio.longhitano@ct.infn.it (F.L.)

- Université de Strasbourg, CNRS, IPHC UMR 7178, F-67000 Strasbourg, France; arnauld.albert@iphc.cnrs.fr (A.A.)

- <sup>3</sup> Université de Haute Alsace, rue des Frères Lumière, 68093 Mulhouse Cedex, France

- <sup>4</sup> IFIC—Instituto de Física Corpuscular (CSIC—Universitat de València), c/Catedrático José Beltrán, 2, 46980 Paterna, Valencia, Spain; salvesgarre@km3net.de (S.A.G.); sara.gozzini@ific.uv.es (S.R.G.); juan.j.hernandez@ific.uv.es (J.-J.H.-R.); ushak.rahaman@ific.uv.es (U.R.)

- <sup>5</sup> Aix Marseille Univ, CNRS/IN2P3, CPPM, Marseille, France

- INFN, Sezione di Napoli, Complesso Universitario di Monte S. Angelo, Via Cintia ed. G, Napoli, 80126 Italy; riccardomaria.bozza@unina.it (R.M.B.); lucio.gialanella@na.infn.it (L.G.); fabio.marzaioli@unicampania.it (F.M.); maximil@na.infn.it (C.M.M.)

- Università di Napoli "Federico II", Dip. Scienze Fisiche "E. Pancini", Complesso Universitario di Monte S. Angelo, Via Cintia ed. G, Napoli, 80126 Italy

- <sup>8</sup> INFN, Sezione di Roma, Piazzale Aldo Moro 2, Roma, 00185 Italy; fabrizio.ameli@roma1.infn.it (F.A.); antonio.capone@roma1.infn.it (A.C.)

- Universitat Politècnica de Catalunya, Laboratori d'Aplicacions Bioacústiques, Centre Tecnològic de Vilanova i la Geltrú, Avda. Rambla Exposició, s/n, Vilanova i la Geltrú, 08800 Spain

- NCSR Demokritos, Institute of Nuclear and Particle Physics, Ag. Paraskevi Attikis, Athens, 15310 Greece; androutsou@inp.demokritos.gr (E.A.); cmarkou@inp.demokritos.gr (C.M.)

- University of Granada, Dept. of Computer Architecture and Technology/CITIC, 18071 Granada, Spain; manguita@ugr.es (M.A.); cdiazmartin@ugr.es (C.D.M.)

- Subatech, IMT Atlantique, IN2P3-CNRS, Université de Nantes, 4 rue Alfred Kastler—La Chantrerie, Nantes, BP 20722 44307 France

- Universitat Politècnica de València, Instituto de Investigación para la Gestión Integrada de las Zonas Costeras, C/ Paranimf, 1, Gandia, 46730 Spain; mardid@fis.upv.es (M.A.); jmmora@fis.upv.es (J.A.M.-M.)

Electronics **2024**, 13, 2044 3 of 17

- <sup>14</sup> University Mohammed V in Rabat, Faculty of Sciences, 4 av. Ibn Battouta, B.P. 1014, R.P. 10000 Rabat, Morocco

- Université Paris Cité, CNRS, Astroparticule et Cosmologie, F-75013 Paris, France; julien.aublin@apc.in2p3.fr (J.A.)

- <sup>16</sup> INFN, Sezione di Genova, Via Dodecaneso 33, Genova, 16146 Italy; vladimir.kulikoskiy@ge.infn.it (V.K.); martina.marconi@ge.infn.it (M.M.); saverio.minutoli@ge.infn.it (S.M.)

- LPC CAEN, Normandie Univ, ENSICAEN, UNICAEN, CNRS/IN2P3, 6 boulevard Maréchal Juin, Caen, 14050 France; guillon@in2p3.fr (B.G.)

- 18 Czech Technical University in Prague, Institute of Experimental and Applied Physics, Husova 240/5, Prague, 110 00 Czech Republic; fadahat.mamedov@cvut.cz (F.M.)

- Comenius University in Bratislava, Department of Nuclear Physics and Biophysics, Mlynska dolina F1, Bratislava, 842 48 Slovak Republic; dvornicky@fmph.uniba.sk (R.D.)

- Nikhef, National Institute for Subatomic Physics, PO Box 41882, Amsterdam, 1009 DB Netherlands; peterj@nikhef.nl (P.J.); dosamt@nikhef.nl (D.F.E.S.)

- INFN, Sezione di Bologna, v.le C. Berti-Pichat, 6/2, Bologna, 40127 Italy; benfenat@bo.infn.it (F.B.); ilaria.delrosso2@unibo.it (I.D.R.); annarita.margiotta@unibo.it (A.M.)

- <sup>22</sup> Università di Bologna, Dipartimento di Fisica e Astronomia, v.le C. Berti-Pichat, 6/2, Bologna, 40127 Italy

- Università degli Studi della Campania "Luigi Vanvitelli", Dipartimento di Matematica e Fisica, viale Lincoln 5, Caserta, 81100 Italy

- E. A. Milne Centre for Astrophysics, University of Hull, Hull, HU6 7RX, United Kingdom; d.benoit@hull.ac.uk (D.M.B.); brad.k.gibson@gmail.com (B.K.G.)

- INFN, Laboratori Nazionali del Sud, Via S. Sofia 62, Catania, 95123 Italy; simone.biagi@lns.infn.it (S.B.); coniglione@lns.infn.it (R.C.); litrico@lns.infn.it (P.L.)

- North-West University, Centre for Space Research, Private Bag X6001, Potchefstroom, 2520 South Africa; markus.bottcher@nwu.ac.za (M.B.)

- University Mohammed I, Faculty of Sciences, BV Mohammed VI, B.P. 717, R.P. 60000 Oujda, Morocco; houria.ghaddari@ump.ac.ma (H.G.)

- <sup>28</sup> Università di Salerno e INFN Gruppo Collegato di Salerno, Dipartimento di Fisica, Via Giovanni Paolo II 132, Fisciano, 84084 Italy

- <sup>29</sup> ISS, Atomistilor 409, Măgurele, RO-077125 Romania

- <sup>30</sup> University of Amsterdam, Institute of Physics/IHEF, PO Box 94216, Amsterdam, 1090 GE Netherlands

- TNO, Technical Sciences, PO Box 155, Delft, 2600 AD Netherlands

- <sup>32</sup> Università La Sapienza, Dipartimento di Fisica, Piazzale Aldo Moro 2, Roma, 00185 Italy

- <sup>33</sup> Università di Bologna, Dipartimento di Ingegneria dell'Energia Elettrica e dell'Informazione "Guglielmo Marconi", Via dell'Università 50, Cesena, 47521 Italia

- <sup>34</sup> Cadi Ayyad University, Physics Department, Faculty of Science Semlalia, Av. My Abdellah, P.O.B. 2390, Marrakech, 40000 Morocco

- Friedrich-Alexander-Universität Erlangen-Nürnberg (FAU), Erlangen Centre for Astroparticle Physics, Nikolaus-Fiebiger-Straße 2, 91058 Erlangen, Germany; michael.chadolias@fau.de (M.C.); tgal@km3net.de (T.G.); rgracia@km3net.de (R.G.); uli.katz@physik.uni-erlangen.de (U.K.); jutta.schnabel@fau.de (J.S.); johannes.schumann@fau.de (J.S.)

- <sup>36</sup> University of the Witwatersrand, School of Physics, Private Bag 3, Johannesburg, Wits 2050 South Africa; andrew.chen@wits.ac.za (A.C.)

- <sup>37</sup> Università di Catania, Dipartimento di Fisica e Astronomia "Ettore Majorana", Via Santa Sofia 64, Catania, 95123 Italy

- <sup>38</sup> INFN, Sezione di Bari, via Orabona, 4, Bari, 70125 Italy; marco.circella@ba.infn.it (M.C.)

- 39 Leiden University, Leiden Institute of Physics, PO Box 9504, Leiden, 2300 RA Netherlands

- <sup>40</sup> University Würzburg, Emil-Fischer-Straße 31, Würzburg, 97074 Germany; amar.hekalo@stud-mail.uni-wuerzburg.de (A.H.)

- Western Sydney University, School of Computing, Engineering and Mathematics, Locked Bag 1797, Penrith, NSW 2751 Australia

- 42 Laboratoire Univers et Particules de Montpellier, Place Eugène Bataillon—CC 72, Montpellier Cédex 05, 34095 France

- <sup>43</sup> IN2P3, LPC, Campus des Cézeaux 24, avenue des Landais BP 80026, Aubière Cedex, 63171 France

- <sup>44</sup> Università di Genova, Via Dodecaneso 33, Genova, 16146 Italy

- <sup>45</sup> University of Granada, Dpto. de Física Teórica y del Cosmos & C.A.F.P.E., 18071 Granada, Spain

- National Centre for Nuclear Research, 02-093 Warsaw, Poland

- <sup>47</sup> AstroCeNT, Nicolaus Copernicus Astronomical Center, Polish Academy of Sciences, Rektorska 4, Warsaw, 00-614 Poland

- <sup>48</sup> Tbilisi State University, Department of Physics, 3, Chavchavadze Ave., Tbilisi, 0179 Georgia

- <sup>49</sup> The University of Georgia, Institute of Physics, Kostava str. 77, Tbilisi, 0171 Georgia; ramaz@grena.ge

- <sup>50</sup> Institut Universitaire de France, 1 rue Descartes, Paris, 75005 France

- <sup>51</sup> IN2P3, 3, Rue Michel-Ange, Paris 16, 75794 France

Electronics **2024**, 13, 2044 4 of 17

- <sup>52</sup> LPC, Campus des Cézeaux 24, avenue des Landais BP 80026, Aubière Cedex, 63171 France

- 53 University of Johannesburg, Department Physics, PO Box 524, Auckland Park, 2006 South Africa

- Università degli Studi della Campania "Luigi Vanvitelli", CAPACITY, Laboratorio CIRCE—Dip. Di Matematica e Fisica—Viale Carlo III di Borbone 153, San Nicola La Strada, 81020 Italy

- <sup>55</sup> NIOZ (Royal Netherlands Institute for Sea Research), PO Box 59, Den Burg, Texel, 1790 AB, The Netherlands

- Friedrich-Alexander-Universität Erlangen-Nürnberg (FAU), Remeis Sternwarte, Sternwartstraße 7, 96049 Bamberg, Germany

- \* Correspondence: real@ific.uv.es

Abstract: The KM3NeT Collaboration is building an underwater neutrino observatory at the bottom of the Mediterranean Sea, consisting of two neutrino telescopes, both composed of a three-dimensional array of light detectors, known as digital optical modules. Each digital optical module contains a set of 31 three-inch photomultiplier tubes distributed over the surface of a 0.44 m diameter pressureresistant glass sphere. The module also includes calibration instruments and electronics for power, readout, and data acquisition. The power board was developed to supply power to all the elements of the digital optical module. The design of the power board began in 2013, and ten prototypes were produced and tested. After an exhaustive validation process in various laboratories within the KM3NeT Collaboration, a mass production batch began, resulting in the construction of over 1200 power boards so far. These boards were integrated in the digital optical modules that have already been produced and deployed, which total 828 as of October 2023. In 2017, an upgrade of the power board, to increase reliability and efficiency, was initiated. The validation of a pre-production series has been completed, and a production batch of 800 upgraded boards is currently underway. This paper describes the design, architecture, upgrade, validation, and production of the power board, including the reliability studies and tests conducted to ensure safe operation at the bottom of the Mediterranean Sea throughout the observatory's lifespan.

Keywords: power supply; acquisition electronics; neutrino telescopes

## 1. Introduction

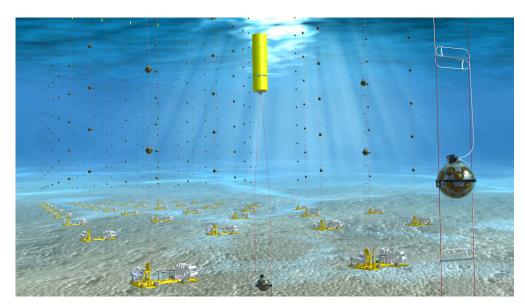

The KM3NeT Collaboration is building two underwater neutrino telescopes in the Mediterranean Sea for the detection of astrophysical neutrinos and the study of the fundamental neutrino properties, measuring the oscillation patterns of atmospheric neutrinos [1]. These detectors, known as Astroparticle Research with Cosmics in the Abyss (ARCA) and Oscillation Research with Cosmics in the Abyss (ORCA), are located off the southern coast of Sicily, Italy, and near the coast of Toulon, France, respectively, at depths of approximately 3500 m and 2450 m. The telescopes are built in the form of 3D lattices of light detectors called Digital Optical Modules (DOMs) [2], each containing 31 three-inch photomultiplier tubes (PMTs) [3], instrumentation for calibration and positioning, and all associated electronics boards. The DOMs are used to reconstruct the trajectory and energy of the primary neutrino by measuring the arrival times and positions of the Cherenkov photons induced by the relativistic charged particles produced in the interaction of neutrinos with matter inside and nearby the telescopes. The designed instrumented volume is around 1 km<sup>3</sup> for ARCA and  $7 \times 10^6$  m<sup>3</sup> for ORCA. The DOMs are distributed along lines called Detection Units (DUs), each containing 18 DOMs. The DUs are anchored on the seafloor and kept vertical by the buoyancy of the DOMs and buoys at the top. The horizontal spacing between DUs is approximately 90 m in ARCA and 20 m in ORCA, whereas the vertical spacing is around 36 m in ARCA and 9 m in ORCA. The different spatial configurations of ARCA and ORCA correspond to the different scientific scopes and neutrino energy ranges, with ARCA being optimized for the detection of cosmic neutrinos (TeV—PeV) and ORCA for atmospheric neutrinos (1 GeV-1 TeV). ARCA will consist of 230 DUs distributed in two separated blocks, while ORCA will be formed by only one block of 115 DUs. As of October 2023, the number of DUs deployed was 28 in ARCA and 18 in ORCA. See Figure 1 for a sketch view of the KM3NeT detector.

Electronics **2024**, 13, 2044 5 of 17

**Figure 1.** Artistic view of the KM3NeT detector. The illustration is not to scale: sunlight does not reach the depths at which the KM3NeT detector is deployed. The total instrumented volume of the KM3NeT detectors, once completed, will be around 1 km<sup>3</sup> for ARCA and  $7 \times 10^6$  m<sup>3</sup> for ORCA.

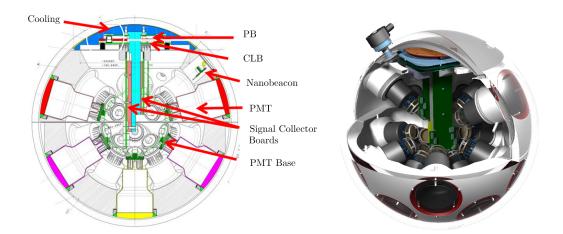

The main data-acquisition electronic board of the DOM is the Central Logic Board (CLB) [4], which mainly performs the readout of the 31 PMT channels. The power board (PB) is mounted on the bottom of the CLB and provides power to all the DOM elements. This includes generating the high voltage for the 31 PMTs and for all the instrumentation devices located inside the DOM, including the compass, accelerometer, gyroscope, pressure, humidity, and temperature sensors, and the power for the time and positioning calibration devices, including the the Nanobeacon flasher [5] and the acoustic piezo sensor.

The PB has to generate different voltages for the Field Programmable Gate Array (FPGA) of the CLB in the proper startup sequence. The Xilinx FPGA needs a monotonic startup sequence for all the voltages to avoid an increasing inrush current. The PB also includes the readout interface to monitor all the voltages and currents generated. To isolate the power circuit, reduce noise, and enhance reliability in the CLB, it was decided to build a separate power board in the KM3NeT acquisition electronics. This approach has also been adopted by other physics experiments such as ALICE [6] or ATLAS TileCAL [7]; however, it is different from the design of IceCube, where the power supply is embedded in the main acquisition board [8].

The PB is located in the shielded part of the aluminum cooling frame in the DOM to protect the sensitive electronics inside the DOM from interference caused by the high-frequency noise produced by the DC/DC converters of the PB. This location also provides better cooling for the PB. The frame at this point is shaped like a solid spherical cap that makes full contact with the inner surface of the DOM glass sphere. This helps maximize the heat flow to the surrounding seawater, where the ambient temperature is around  $13\,^{\circ}$ C, acting as a heat sink for the thermal losses of the converters of the PB. Figure 2 shows the different elements inside the DOM as well as the location of the PB.

The initial design of the power board was completed in 2013. A pre-series of prototypes was built and submitted to numerous and rigorous tests, such as HALT tests [9], efficiency tests, etc. After an extensive validation process across various laboratories within the KM3NeT Collaboration, more than 1200 power boards were manufactured. These were integrated into the DOMs which have already been deployed in the sea, numbering 828 as of October 2023. An upgrade of the power board began in 2017 with the aim of improving efficiency and reliability. Following the validation of the pre-production series, a production batch of 800 improved boards is currently being worked on.

Electronics **2024**, 13, 2044 6 of 17

**Figure 2.** (**Left**) Two-dimensional vertical cross-section of the DOM showing the position of the PB and the main elements of the DOM indicated with arrows. (**Right**) Three-dimensional representation of the DOM.

This paper is organized as follows: The design and architecture of the KM3NeT power board are detailed in Section 2, while the upgrade of the PB, primarily through a better selection of converters to improve efficiency and reduce consumption, is presented in Section 3. Section 4 describes the analysis of reliability. The production, control, and the functional tests applied are discussed in Sections 5 and 6, while in Section 7, the results on production and reliability are presented. Finally, conclusions are drawn in Section 8.

# 2. Design and Architecture of the Power Board

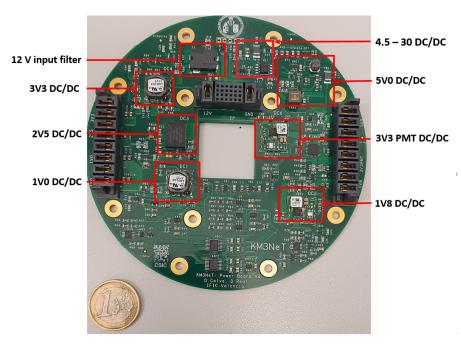

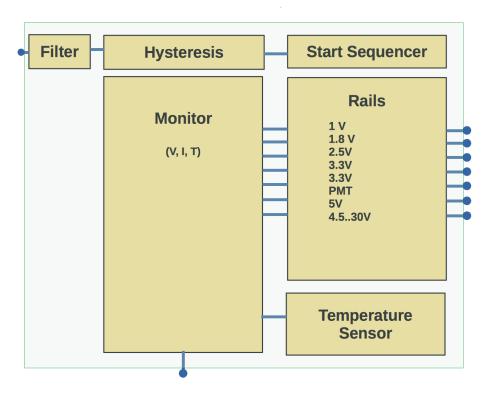

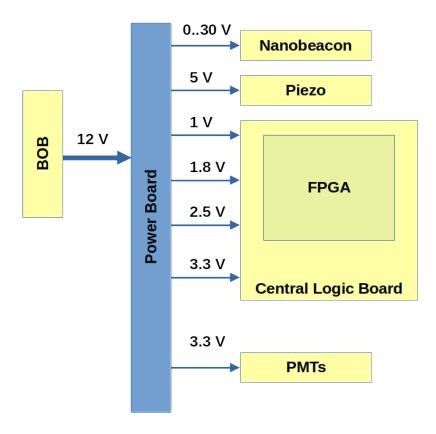

The PB (Figure 3) is a crucial component of the KM3NeT detector, as it provides power to the CLB and to the rest of the DOM elements. Because of the remote location of KM3NeT in the deep sea, the PB design goals for the power board were low power consumption and high reliability. This is crucial because the maintenance of the deployed structures involves complex and costly operations. The architecture of the PB, including its various functionalities, is shown in Figure 4. The PB is supplied with 12 V, which is generated with a DC/DC converter from 400 V at the BreakOut Box (BOB), a waterproof enclosure at the input of the DOM that can withstand the harsh conditions of the deep sea. The breakout box is connected, via the DU backbone, to the DU base to receive the high voltage. The PB provides power supply (See Figure 5) to the piezo (5 V), to the Nanobeacon (the 0 to 30 V variable power rail), to the PMTs (3.3 V), and to the CLB (1 V, 1.8 V, 2.5 V, and 3.3 V).

The main blocks of the PB are as follows:

- The filter block at the input voltage of the PB, which removes the high-frequency noise generated by the power converters at the DU base and breakout board;

- The hysteresis block, which prevents the PB from entering into an unstable state during startup and shutdown;

- The startup block, which allows the different voltages to start up monotonically as needed by the FPGA of the CLB;

- The Nanobeacon power supply controller, which controls the power supply of the Nanobeacon and can be configured through I<sup>2</sup>C;

- The monitoring system, which reads out the voltages and currents of every power rail, in addition to the temperature sensor.

Electronics **2024**, 13, 2044 7 of 17

**Figure 3.** View of the PB of the DOM (upgraded version). The different DC/DC converters to generate the voltages needed by the FPGA and the remaining components of the CLB are marked.

**Figure 4.** Architecture of the PB. The rails, which provide the different power supplies needed by the DOM, are managed by the start sequencer, which generates at startup the monotonic power sequence requested by the CLB FPGA. The monitor subsystem surveys the voltages and currents of the different rails, as well as the temperature sensor installed on the board. The 12 V is filtered at the input and the hysteresis system prevents instabilities while powering up and down the PB.

Electronics **2024**, 13, 2044 8 of 17

**Figure 5.** Diagram of the power supply distribution at the DOM. The BOB of the DOM provides 12 volts to the power board, where the power rails for the Nanobeacon, Piezo, CLB and PMTs are generated. Note that two 3.3 V rails are available, one for the CLB and another for the PMTs.

The main characteristics and functionalities of the PB blocks are detailed in the following subsections.

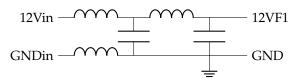

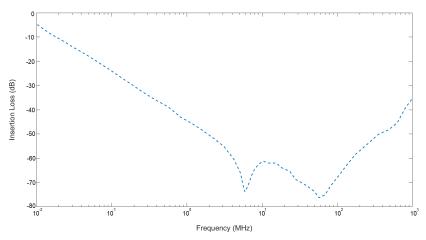

## 2.1. Input High-Frequency Filter

The PB incorporates an Electro-Magnetic Interference (EMI) filter to remove high-frequency noise from the 12 V DC input signal, providing a low-impedance path for the noise and allowing the desired signal to pass through with minimal attenuation. The filter consists of a Pi filter (see Figure 6) with two capacitors connected to the ground and an inductor connected between the two capacitors [10]. Two inductors connected between the power terminals and the inputs of the Pi filter are also included. The insertion losses of the filter have a minimum of 35 dB from 1 MHz to 1 GHz with a maximum drop of 30 mV. The filter can withstand a maximum voltage of 125 V (DC) and has a rated voltage of 50 V (DC) with a nominal operation of 12 V. The bode diagram of the filter is shown in Figure 7. Overall, the use of the filter improves the performance and reliability of the PB by reducing the impact of EMI noise on its operation.

Figure 6. Scheme of the Pi filter functioning as input high-frequency filter on the PB.

Electronics **2024**, 13, 2044 9 of 17

**Figure 7.** Bode diagram of the Pi filter at the PB to filter out high-frequency noise. From 1 MHz up to 1 GHz, the insertion losses are below -35 dB.

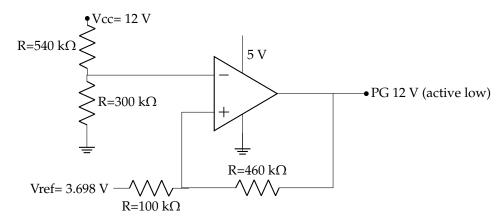

# 2.2. Hysteresis

The PB implements a hysteresis loop to avoid instabilities at the startup [11]. The DC/DC converters of the PB are enabled only when the input voltage exceeds 11 V and are disabled when the input value drops below 9.5 V. In this way, the fluctuations in the PB regulators are avoided during power on/off. The scheme of the hysteresis subsystem is presented in Figure 8. To provide hysteresis functionality, an operational amplifier is used in comparator mode with positive feedback. The input voltage is compared to a reference voltage (3.698 V), and the output is either high or low, depending on whether the input is above or below the reference. The input voltage is supplied to the operational amplifier after a voltage divider circuit, enabling a range of operation from 0 to 5 V. The non-inverting input of the operational amplifier is connected to the operational amplifier output through a resistor. The inverting input of the operational amplifier is connected to the input reference voltage. The resistor values in the voltage divider circuit at the input are chosen to set the reference voltage to the desired switching thresholds. When the input voltage is between 9.5 V and 11 V, the output will be either low (active) or high depending on the current state of the system. If the output is low, the reference voltage will be 9.5 V, and the system will switch off when the input voltage drops below 9.5 V. If the output is high (inactive), the reference voltage will be 11 V, and the system will switch on when the input voltage rises above 11 V. This creates the desired hysteresis effect, where the switching threshold depends on the current state of the system, avoiding fluctuations in the switching up and down of the system.

**Figure 8.** Scheme of the hysteresis subsystem. The configuration of the operational amplifier allows it to start at 11 V and to disconnect when the input voltage drops below 9.5 V. In this way, instabilities are prevented at power up and power down.

Electronics **2024**, 13, 2044 10 of 17

# 2.3. Power Startup

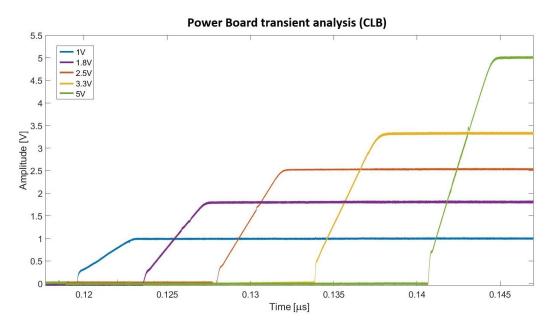

One of the functions of the PB is to provide a proper voltage startup sequence for the FPGA of the CLB (https://docs.xilinx.com/v/u/en-US/ds182\_Kintex\_7\_Data\_Sheet (accessed on 15 January 2024)). Providing a power startup sequence for FPGAs is crucial for ensuring reliability, functionality, performance, and seamless integration within other systems [12]. To achieve this, the PB includes a sequencer that generates the required sequence of voltages, which starts monotonically, as shown in Figure 9. The output of the hysteresis block initiates the sequence by starting the lower voltage rail (1 V). Then, the power-good signal of the lower voltage rail is connected in a cascading manner to prevent the higher voltage rails from starting until the previous rail has started successfully. In this way, a monotonically increasing sequence is produced. Two power-good signals are sent outside by the PB for monitoring and control purposes. The first one indicates that the voltage for PMTs has been successfully started (power-good PMT). The second one indicates the completion of the entire power-up sequence when the 5 V starts successfully.

**Figure 9.** Startup sequence of the PB. The figure shows that the PB indeed generates the various voltages in the sequence needed by the Xilinx FPGA on the CLB.

#### 2.4. DC/DC Rails

The PB generates six regulated voltages (1 V, 1.8 V, 2.5 V, 3.3 V, 3.3 V PMT, and 5 V) from the 12 V input using five non-isolated point-of-load (POL) DC/DC converters [13] and a linear regulator. The modular POL approach is easy and fast to implement and leads to a compact design with a small footprint and a simple Printed Circuit Board (PCB) layout. These designs are optimized by the manufacturer for size, heat flow, and EMI protection. They are also reliable in terms of initial assembly errors, response to fault conditions, and component lifetime failures. In addition, they include sophisticated protection mechanisms like low-pressure molding or chemical protection to avoid corrosion or moisture. The PB employs high-efficiency DC/DC converters to minimize power consumption in the DOM with the exception of the 3.3 V PMT linear regulator used to reduce noise on the PMT voltage rail. The efficiencies of these DC/DC converters are listed in Table 1 for both the original and upgraded versions.

Electronics **2024**, 13, 2044 11 of 17

| Voltage (V) | Current (A) | Efficiency Original PB (%) | Efficiency Upgraded PB (%) |

|-------------|-------------|----------------------------|----------------------------|

| 1           | 0.13        | 80                         | 80                         |

| 1.8         | 0.33        | 80                         | 80                         |

| 2.5         | 0.33        | 60                         | 78                         |

| 3.3         | 0.81        | 65                         | 90                         |

| 3.3 PMT     | 0.46        | 90                         | 90                         |

| 5           | 0.10        | 60                         | 90                         |

|             |             |                            |                            |

Table 1. PB efficiency for each rail output for both the original and upgraded versions.

## 2.5. Nanobeacon

The PB has a configurable output which is used by the Nanobeacon, a time-calibration device mounted in the DOM. This configurable output consists of a DC/DC converter that operates in a buck–boost configuration and can provide a voltage that is adjustable between 4.5 V and 30 V through an I<sup>2</sup>C-controlled 10 bit DAC. When the output voltage of the DAC changes, the control voltage of the DC/DC converter is modified, and the voltage of the Nanobeacon power rail is adjusted accordingly. This voltage determines the amount of current supplied to the LED and, therefore, the intensity of the generated optical pulse.

## 2.6. Monitoring System

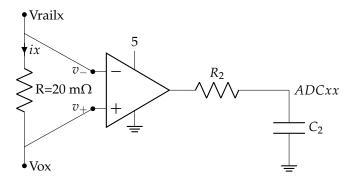

The currents and voltages of the PB are monitored in real time using two 12 bit ADCs of 12 inputs mounted on the board. In order to read out the current, resistance of low value,  $20 \text{ m}\Omega$ , is mounted in series in the rail where the current is measured. The two pads of the resistor are connected to a high-precision current-sense amplifier, also called a current-shunt monitor, with a fixed gain of 50. As an example, a 0.5 A DC current causes a voltage drop of 10 mV at the 20 m $\Omega$  shunt resistor, which is amplified to 0.5 V by the operational amplifier. This voltage is digitized by an ADC channel, which is read out via I<sup>2</sup>C. Figure 10 shows the design of the circuit used to read out the rail intensity. Some rails, such as the 1.8 V, 2.5 V, and the regulated 5 V, use a shunt resistor of 50 m $\Omega$  because the current circulating is lower than in the other rails. The conversion ratio (voltage to current) for each rail is taken into account by the monitoring software. The PB also includes a temperature LM45BIM3 sensor (https://www.ti.com/lit/gpn/lm45 (accessed on 15 January 2024)), which is read out by one of the ADC channels. The voltages are adapted to the ADC voltage scale and connected to a voltage follower for readout. Voltages, currents, and temperature are read using two MAX1239 ADCs (https://www.analog.com/media/en/technical-documentatio n/data-sheets/MAX1236-MAX1239M.pdf (accessed on 15 January 2024)). In Table 2, the different ratios are shown.

**Figure 10.** Template of the circuit to read out the current. The output line of a power rail passes through a 20 m $\Omega$  resistor, where the drop voltage is amplified in a high-precision amplifier. The output of the amplifier is read out in an ADC channel and sent via  $I^2C$  outside of the PB to the CLB.

Electronics **2024**, 13, 2044 12 of 17

**Table 2.** Conversion ratios and associated process variable. The ratios are used to convert the voltage value read by the ADC channel either to volts or amperes. In the case of the current readout, the values of the shunt resistance are provided too.

| Process Variable     | Ratio | Resistance             | Description                            |

|----------------------|-------|------------------------|----------------------------------------|

| 12 V current         | 1     | $20~\text{m}\Omega$    | 12 V current                           |

| 1V0 current          | 1     | $20\mathrm{m}\Omega$   | Current at the 1 V rail                |

| 1V8 current          | 0.4   | $50\mathrm{m}\Omega$   | Current at the 1.8 V rail              |

| 2V5 current          | 0.4   | $50\mathrm{m}\Omega$   | Current at the 2.5 V rail              |

| 3V3 current          | 1     | $20\mathrm{m}\Omega$   | Current at the 3.3 V rail              |

| 5V0 current          | 0.4   | $50  \mathrm{m}\Omega$ | Current at the 5 V rail                |

| 3V3PMT current       | 2     | $10~\mathrm{m}\Omega$  | Current at the 3.3 V rail for the PMTs |

| VLED current         | 2     | $10~\mathrm{m}\Omega$  | Current at the Nanobeacon rail         |

| VLED voltage         | 10.1  |                        | Voltage at the Nanobeacon rail         |

| 1V0 voltage          | 1     |                        | Voltage at the 1 V rail                |

| 1V8 voltage          | 1     |                        | Voltage at the 1.8 V rail              |

| 2V5 voltage          | 1     |                        | Voltage at the 2.5 V rail              |

| 3V3 voltage          | 2     |                        | Voltage at the 3.3 V rail              |

| 5V0 voltage          | 2     |                        | Voltage at the 5.0 V rail              |

| 3V3PMT voltage       | 2     |                        | Voltage at the 3.3 V rail for the PMTs |

| VLED control voltage | 1     |                        | Voltage at the Nanobeacon rail         |

| PB Temp              | 100   |                        | Temperature in the PB. Value in °C     |

#### 2.7. Layout

The layout of the PB has four layers: two for signals, placed on the top and bottom layers, one for power planes, and one for ground. The layer distribution and the stackup chosen for the PB are shown in Figure 11. The bottom of the board has no components, so a thermal interface pad can be placed between it and the aluminum frame onto which it is mounted.

**Figure 11.** Stackup of the PB PCB. It contains four layers, all of them being copper and with a width of 35  $\mu$ m. The dielectric material is FR4, with a core of 1000  $\mu$ m and two external frames of 200  $\mu$ m. For a better representation, the image is not to scale.

# 2.8. Firmware

The CLB firmware reads the PB's voltages, currents, and temperature. The CLB firmware is a combination of gateware and embedded software, with the gateware made up of logic coded in Hardware Description Language (HDL) and the embedded software written in C [14]. The gateware includes two LatticeMico32 (LM32) microprocessors (https://www.latticesemi.com/en/Products/DesignSoftwareAndIP/IntellectualProperty/IPCore/IPCores02/LatticeMico32.aspx (accessed on 15 January 2024)): the White Rabbit processor to manage the optical link traffic and tuneable oscillators, and the other to manage the communication interfaces for the instrumentation devices. The software is organized in three distinct layers—Common, Platform, and Application—where the Application layer holds code for detectors, peripherals, and slow control. This layer manages the ADCs and temperature sensor of the PB.

Electronics **2024**, 13, 2044 13 of 17

## 3. Power Board Upgrade

In 2017, an upgrade of the PB was initiated with the aim of improving its overall efficiency. The PB was modified to operate more efficiently by replacing some of the DC/DC converters. These modifications reduce the power consumption, thermal losses [15], and temperature inside the DOM, thereby increasing the overall reliability of the DOM electronics. A set of new DC/DC converters was chosen, paying particular attention to their efficiency at the PB's operating point and to their reliability. The original Murata DC/DC converters (https://www.murata.com/products/productdata/8807038189598/okl-t3-w 12.pdf?1583754815000 (accessed on 15 January 2024)) of the 2.5 V, 3.3 V, and 5 V rails were changed. For 3.3 V, a similar DC/DC model from Murata with the proper current output was selected. For 2.5 V and 5 V, new models from Analog Devices were chosen. After implementing these modifications, a decrease of more than one Watt in the power consumption of the DOM acquisition electronics was achieved (see Table 1).

## 4. Reliability: FIDES and HALT

The reliability of both versions of the PB has been evaluated using a FIDES analysis [16], and in the case of the upgraded version also by using a Highly Accelerated Life Test (HALT) procedure. These methods are used by KM3NeT to increase the reliability of the boards in the early stages of the development process. An investigation approach into the reliability of the power system is proposed as the most cost-effective option for enhancing system integrity against failures [17].

#### 4.1. FIDES

FIDES is the method selected by KM3NeT Collaboration to assess the reliability of electronic boards [18]. It provides a handbook for predicting the reliability of components and a guide for auditing the manufacturing process. Using this method, it is possible to compute an estimate of the Failure In Time (FIT, given in failures per 10<sup>9</sup> h) or the Mean Time Between Failure (MTBF) of the analyzed board. The FIDES method takes into account the expected operational conditions or stress, the life profile, and the technological factors that affect the reliability of the board. In addition to the estimated FIT, the method can identify weak points in the design of the board at a very early stage, saving time and costs in the development process for electronic boards. The reliability of the PB has been evaluated, providing a FIT value of 947, while the upgraded version has increased its reliability up to a FIT value of 783. This FIT number means that around 90% of the PB will not have any issues during the total KM3NeT operation time. The value calculated refers to the complete board, but there are subsystems that are not critical, such as the piezo sensor or the Nanobeacon power subsystem, the loss of which would not harm the operation of the DOM, so the expected failure rate of boards after the total KM3NeT operation time will be lower than 10%.

## 4.2. HALT

The HALT method [19] is used to assess the reliability of electronic boards by applying various forms of stress to a small number of boards, usually four to six, at an early design stage. HALT tests are implemented by putting the PBs under extreme temperatures and under extreme rates of temperature change (1  $^{\circ}$ C/min). The goal of these tests is to ensure the functionality of the product and to optimize the test setup for maximum functional test coverage. The test setup should also allow for remote operation outside the environmental chamber. In KM3NeT, this approach has been introduced and has been used on the upgraded version of the PB. The temperature step stress tests involve decreasing and increasing the temperature of the boards in steps, while the extreme temperature stress tests involve rapid changes in the temperature to the minimum and to the maximum. A total of six PBs have undergone HALT tests in combination with six CLBs. The minimum temperature reached by the PBs was  $-40 \, ^{\circ}$ C, the limit of the climatic chamber used. The maximum temperature was 95  $^{\circ}$ C, the temperature at which the PB still worked. The tests

Electronics **2024**, 13, 2044

were stopped when the FPGA had to be switched off as a precaution because the internal temperature was over its operational limit. The results of the HALT tests allow us to set the limits for the Highly Accelerated Stress Screening (HASS) tests, which are used during mass production to filter infant mortality.

#### 5. Production Control

More than six thousand PBs have to be produced for the construction of the DOMs and DUs to be deployed at the bottom of the Mediterranean Sea. To ensure their reliability, a series of production requirements have been established as follows:

- The PCB production and assembly process must comply with standard IPC 6011 Class 3 [20].

- Solder paste masks should be generated using the given *gerber files*, choosing the pad-shrinking factor based on the solder paste and the mask thickness.

- Solder paste must be deposited on the PCB using automatic machines and the aforementioned masks for good uniformity.

- Solder paste deposition must be inspected before the PCB is populated.

- All surface-mounted device components must be placed using automatic pick and place machines.

- A reflow oven must be used for soldering the components.

- The boards must be identifiable. If the PCBs also have an individual identifying code from the producing company, an electronic file with the correspondence between the board label and the PCB label must be provided.

- The production must provide traceability of all procured components in accordance with IPC1782 [21] level 2 (M2), with level 3 (M3) traceability as a second option.

After production, a series of tests are required as part of the procurement process. The data from these tests are stored in electronic format. Finally, appropriate packaging for shipment to the integration sites should be implemented.

# 5.1. PCB Test Control

Before the PBs are assembled, the following tests are carried out on the PCBs:

- 100% electrical continuity tests;

- Control of correspondence to IPC Class 3 on a sample of boards performing metallographic micro sections.

## 5.2. Component Assembly Test Control

The following activities are carried out during the assembly of components on the PCB:

- Identification of the board with an appropriate label;

- Automatic optical inspection on the positioning and soldering of components on all boards;

- X-ray inspection and verification of very thin quad flat non-leaded package components.

## 6. Functional Tests

Functional tests are performed immediately after the production of the boards to check their correct behavior and identify faulty boards. During these tests, the PB is connected to a CLB. The CLB is programmed to provide a maximum voltage of 30 V on the Nanobeacon device.

The following actions are required for the tests:

- Set the input voltage to 12 V and power-on the system;

- Verify that the rail voltages remain within the specified accuracy ranges (see Table 3), as measured at the positions of the CLB indicated in Figure 12;

Electronics **2024**, 13, 2044 15 of 17

• Write down the measurements after 1 min and 5 min from power-on, and finally, once the test are finished and the boards are powered off, the results of the tests are stored in an electronic file.

**Table 3.** Nominal values of voltage for each rail and the percentage of variation allowed in the functional test.

| Rail   | Voltage (V) | Accuracy (%) |

|--------|-------------|--------------|

| 1V0    | 1.0         | ±1.5         |

| 1V8    | 1.8         | ±3.0         |

| 2V5    | 2.5         | ±3.0         |

| 3V3    | 3.3         | ±1.5         |

| 3V3PMT | 3.3         | ±3.0         |

| 5V0    | 5.0         | ±3.0         |

| VLED   | 4.0-30.0    | ±1.0         |

**Figure 12.** Picture of a CLB with the test points for production functional tests. The different power rail test points are marked on the picture. A CLB running operational firmware is used as load and for measuring the voltages.

# 7. Production and Reliability Results

According to the production control process outlined in the previous sections, a total of 2100 PBs have been produced in nine different batches. The production yield has been very high (>99%), with only a few malfunctioning PBs detected during the production tests.

Eight hundred of the produced PBs have been mounted and tested in their corresponding DOMs. During this process, only a few minor issues related to the component assembly process on the PCB were found, and this experience was used to improve the packaging and handling instructions.

## 8. Conclusions

The architecture of the KM3NeT power board, together with the different functional blocks, has been presented. The power boards will be used for more than a decade in

Electronics **2024**, 13, 2044 16 of 17

conditions where access and maintenance are very difficult, making their efficiency and reliability crucial. To ensure the quality and reliability of these boards, specific requirements have been established. The present work outlines the measures taken by KM3NeT Collaboration to enhance the reliability of the power boards during production. Additionally, a test bench has been implemented to filter any non-functional boards after production. A total of 6000 of these boards will be produced for the completion of the KM3NeT infrastructure. As of April 2024, 2100 power boards were successfully produced with a high yield. A total of 828 power boards are already working in the 46 detection units deployed at this time. The research to improve reliability and power consumption as well as to address the obsolescence of components continues.

**Author Contributions:** Conceptualization, D.R. and D.C.; methodology, D.R., D.C., S.C. (Stephane Colonges), P.M. (Paolo Musico), and P.J.; software, D.C., D.R., C.B., V.v.B., O.G., and T.C. (Tommaso Chiarusi); validation, D.R., D.C., P.M. (Paolo Musico), G.P. (Giuliano Pellegrini), P.J., and S.C. (Stephane Colonges); formal analysis, S.C. (Stephane Colonges), D.C., G.P. (Giuliano Pellegrini), and P.J.; investigation, D.C. and D.R.; resources, D.R. and D.C.; data curation, D.R. and D.C.; writing—original draft preparation, D.R. and D.C.; writing—review and editing, all the authors; visualization, D.C., D.R., C.B., V.v.B., and O.G.; supervision, D.R. and D.C.; project administration, D.R.; funding acquisition, J.d.D.Z., J.Z., and D.R. All authors have read and agreed to the published version of the manuscript.

Funding: The authors acknowledge the financial support of the funding agencies: Agence Nationale de la Recherche (contract ANR-15-CE31-0020), Centre National de la Recherche Scientifique (CNRS), Commission Européenne (FEDER fund and Marie Curie Program), LabEx UnivEarthS (ANR-10-LABX-0023 and ANR-18-IDEX-0001), Paris Île-de-France Region, France; Shota Rustaveli National Science Foundation of Georgia (SRNSFG, FR-22-13708), Georgia; The General Secretariat of Research and Innovation (GSRI), Greece; Istituto Nazionale di Fisica Nucleare (INFN), Ministero dell'Università e della Ricerca (MIUR), PRIN 2022 program (Grant PANTHEON 2022E2J4RK); Ministry of Higher Education, Scientific Research and Innovation, Morocco, and the Arab Fund for Economic and Social Development, Kuwait; Nederlandse organisatie voor Wetenschappelijk Onderzoek (NWO), the Netherlands; The National Science Centre, Poland (2021/41/N/ST2/01177); The grant "AstroCeNT: Particle Astrophysics Science and Technology Centre", carried out within the International Research Agendas programme of the Foundation for Polish Science financed by the European Union under the European Regional Development Fund; National Authority for Scientific Research (ANCS), Romania; Grants PID2021-124591NB-C41, -C42, -C43 funded by MCIN/AEI/ 10.13039/501100011033 and, as appropriate, by "ERDF A way of making Europe", by the "European Union" or by the "European Union NextGenerationEU/PRTR", Programa de Planes Complementarios I+D+I (refs. ASFAE/2022/023, ASFAE/2022/014), Programa Prometeo (PROMETEO/2020/019) and GenT (refs. CIDEGENT/2018/034, /2019/043, /2020/049. /2021/23) of the Generalitat Valenciana, Junta de Andalucía (ref. SOMM17/6104/UGR, P18-FR-5057), EU: MSC program (ref. 101025085), Programa María Zambrano (Spanish Ministry of Universities, funded by the European Union, NextGenerationEU), Spain; The European Union's Horizon 2020 Research and Innovation Programme (ChETEC-INFRA—Project no. 101008324).

Data Availability Statement: The data presented in this study are available in this article.

**Conflicts of Interest:** The authors declare no conflicts of interest.

#### References

- 1. Adrián-Martínez1, S.; Ageron, M.; Aharonian, F.; Aiello, S.; Albert, A.; Ameli, F.; Anassontzis, E.; Andre, M.; Androulakis, G.; Anghinolfi, M.; et al. Letter of Intent for KM3NeT 2.0. *J. Phys. G* **2016**, *43*, 084001. [CrossRef]

- 2. Aiello1, S.; Albert, A.; Alshamsi, M.; Garre, S.A.; Aly, Z.; Ambrosone, A.; Ameli, F.; Andre, M.; Androulakis, G.; Anghinolfi, M.; et al. The KM3NeT multi-PMT optical module. *J. Instrum.* **2022**, *17*, P07038. [CrossRef]

- 3. Aiello1, S.; Akrame, S.E.; Ameli, F.; Anassontzis, E.G.; Andre, M.; Androulakis, G.; Anghinolfi, M.; Anton6, G.; Ardid, M.; Aublin, J.; et al. Characterisation of the Hamamatsu photomultipliers for the KM3NeT Neutrino Telescope. *JINST* **2018**, *13*, P05035. [CrossRef]

- 4. Aiello, S.; Ameli, F.; Margiotta, A.; Andre, M.; Androulakis, G.; Anghinolfi, M.; Marinelli, A.; Anton, G.; Ardid, M.; Markou, C.; et al. KM3NeT front-end and readout electronics system: Hardware, firmware, and software. *J. Astron. Telesc. Instrum. Syst.* **2019**, 5, 046001. [CrossRef]

Electronics **2024**, 13, 2044 17 of 17

5. Aiello, S.; Albert, A.; Alshamsi, M.; Garre, S.A.; Aly, Z.; Ambrosone, A.; Ameli, F.; Andre, M.; Androulakis, G.; Anghinolfi, M.; et al. Nanobeacon: A time calibration device for the KM3NeT neutrino telescope. *Nucl. Instrum. Methods Phys. Res. Sect. A* **2022**, 1040, 167132. [CrossRef]

- 6. Saini, J.; Singaraju, R.N.; Santra, G.C.; Bhaskar, P. Low Voltage Distribution Board (LVDB) for ALICE Photon Multiplicity Detector. *DAE Symp. Nucl. Phys.* **2010**, *55*, 762–763.

- 7. Hibbard, M.; Moayedi, S.; Hadavand, H.; Davoudi, A.; on behalf of the ATLAS Tile Calorimeter System. ATLAS TileCal low voltage power supply upgrade hardware and testing. *Nucl. Instrum. Methods A* **2019**, 936, 112–114. [CrossRef]

- 8. Aartsen, M.G.; Ackermann, M.; Adams, J.; Aguilar, J.A.; Ahlers, M.; Ahrens, M.; Altmann, D.; Andeen, K.; Anderson, T.; Ansseau, I.; et al. The IceCube Neutrino Observatory: Instrumentation and Online Systems. *JINST* 2017, 12, P03012. [CrossRef]

- 9. Doertenbach, N. Highly Accelerated Life Testing—Testing with a Different Purpose. S.V. Sound Vib. 2001, 35, 18–23.

- 10. Tanaka, M.; Shimura, K.; Sato, M.; Mizuno, T.; Matsuoka, T. Hybrid inductor for improving gain attenuation characteristics of a Pi filter circuit. *Energy Rep.* **2020**, *6* (Suppl. S9), 446–451. [CrossRef]

- 11. Schild, A.; Lunze, J.; Krupar, J.; Schwarz, W. Design of Generalized Hysteresis Controllers for DC–DC Switching Power Converters. *IEEE Trans. Power Electron.* **2009**, 24, 138–146. [CrossRef]

- 12. Shi, Y.; Li, Y.; Zhou, Y.; Xu, R.; Feng, D.; Yan, Z.; Fang, C. Optimal scheduling for power system peak load regulation considering short-time startup and shutdown operations of thermal power unit. *Int. J. Electr. Power Energy Syst.* **2021**, *31*, 107012. [CrossRef]

- 13. Yin, J.; Beville, E. Chapter 183: Simple and compact 4-output point-of-load DC/DC μModule system. In *Analog Circuit Design*; Elsevier: Amsterdam, The Netherlands, 2015; pp. 385–386. [CrossRef]

- 14. Aiello, S.; Albert, A.; Garre, S.A.; Aly, Z.; Ambrosone, A.; Ameli, F.; Andre, M.; Androutsou, E.; Anghinolfi, M.; Anguita, M.; et al. Embedded Software of the KM3NeT Central Logic Board. *arXiv* 2023, arXiv:2308.01032v2.

- 15. Texas Instruments. Application Report SNVA848A-October 2018-Revised November 2019; Texas Instruments: Dallas, TX, USA, 2019.

- 16. Eurocopter, AIRBUS, Nexter, MBDA, and Thales. Reliability Methodology for Electronic Systems. Edition A. 2010. Available online: http://www.embedded.agh.edu.pl/www/fpga/dydaktyka/MPiMS/Data/UTE\_FIDES\_Guide\_2009\_-\_Edition\_A%2 0-%20September%202010\_english\_version.pdf (accessed on 15 January 2024).

- 17. Martino, E.; Fairbrother, A.; Ghosh, R.; Schuderer, J. Data-driven and physics-based reliability tests to failure of a power electronics converter. *Microelectron. Reliab.* **2023**, *150*, 115063. [CrossRef]

- 18. Real, D.; Calvo, D.; Musico, P.; Jansweijer, P.; van Beveren, V.; Colonges, S.; Pellegrini, G.; Díaz, A.F. KM3NeT Acquisition Electronics: New Developments and Advances in Reliability. In Proceedings of the 37th International Cosmic Ray Conference (ICRC2021), Berlin, Germany, 12–23 July 2021; p. 1108. [CrossRef]

- 19. Porter, A. Chapter 9—Highly Accelerated Life Testing (HALT). In *Accelerated Testing and Validation*; Newnes: Oxford, UK, 2004; pp. 123–138.

- 20. IPC-6011 Generic Performance Specification for Printed Boards. 1996. Available online: https://www.ipc.org/TOC/IPC-6011.pdf (accessed on 15 January 2024).

- 21. IPC-1782 Standard for Manufacturing and Supply Chain Traceability of Electronic Products. 2019. Available online: https://www.ipc.org/TOC/IPC-1782.pdf (accessed on 15 January 2024).

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.