## LA SAPIENZA UNIVERSITY OF ROME

DOCTORAL THESIS

## Study and development of innovative strategies for energy-efficient cross-layer design of digital VLSI systems based on Approximate Computing

*Author:* Giulia STAZI

Supervisor: Dr. Francesco MENICHELLI

A thesis submitted in fulfillment of the requirements for the degree of Doctor of Philosophy

in the

Department of Information Engineering, Electronics and Telecommunications (DIET)

## **Declaration of Authorship**

I, Giulia STAZI, declare that this thesis titled, "Study and development of innovative strategies for energy-efficient cross-layer design of digital VLSI systems based on Approximate Computing" and the work presented in it are my own. I confirm that:

- This work was done wholly or mainly while in candidature for a research degree at this University.

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated.

- Where I have consulted the published work of others, this is always clearly attributed.

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work.

- I have acknowledged all main sources of help.

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself.

Signed:

Date:

«γνῶθι σεαυτόν»

Delphi's Oracle

#### LA SAPIENZA UNIVERSITY OF ROME

## Abstract

#### Faculty of Information Engineering, Informatics and Statistics (I3S) Department of Information Engineering, Electronics and Telecommunications (DIET)

#### Doctor of Philosophy

## Study and development of innovative strategies for energy-efficient cross-layer design of digital VLSI systems based on Approximate Computing

by Giulia STAZI

The increasing demand on requirements for high performance and energy efficiency in modern digital systems has led to the research of new design approaches that are able to go beyond the established energy-performance tradeoff. Looking at scientific literature, the Approximate Computing paradigm has been particularly prolific. Many applications in the domain of signal processing, multimedia, computer vision, machine learning are known to be particularly resilient to errors occurring on their input data and during computation, producing outputs that, although degraded, are still largely acceptable from the point of view of quality. The Approximate Computing design paradigm leverages the characteristics of this group of applications to develop circuits, architectures, algorithms that, by relaxing design constraints, perform their computations in an approximate or inexact manner reducing energy consumption.

This PhD research aims to explore the design of hardware/software architectures based on Approximate Computing techniques, filling the gap in literature regarding effective applicability and deriving a systematic methodology to characterize its benefits and tradeoffs.

The main contributions of this work are:

- the introduction of approximate memory management inside the Linux OS, allowing dynamic allocation and de-allocation of approximate memory at user level, as for normal exact memory;

- the development of an emulation environment for platforms with approximate memory units, where faults are injected during the simulation based on models that reproduce the effects on memory cells of circuital and architectural techniques for approximate memories;

- the implementation and analysis of the impact of approximate memory hardware on real applications: the H.264 video encoder, internally modified to allocate selected data buffers in approximate memory, and signal processing applications (digital filter) using approximate memory for input/output buffers and tap registers;

- the development of a fully reconfigurable and combinatorial floating point unit, which can work with reduced precision formats.

## Contents

| De | eclara                            | tion of                          | Authorship                                                                                      | iii                                                                                            |

|----|-----------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Ał | ostrac                            | t                                |                                                                                                 | vii                                                                                            |

| 1  | Intro<br>1.1<br>1.2<br>1.3<br>1.4 | Source<br>Appro                  | n<br>for Low Power Circuit Design                                                               | 1<br>1<br>3<br>5<br>7                                                                          |

| 2  | <b>App</b> 2.1 2.2                | Appro                            | te Computing: State of the Art<br>eximate Computing: main concepts                              | <b>11</b><br>11<br>12                                                                          |

|    |                                   | 2.2.2<br>2.2.3<br>2.2.4<br>2.2.5 | puting                                                                                          | 12<br>14<br>14<br>15<br>16<br>16<br>18                                                         |

|    |                                   | 2.2.6                            | Algorithmic Noise Tolerance and Reduced Precision Redun-<br>dancy techniques                    | 20<br>21                                                                                       |

|    |                                   | 2.2.7                            | proximation                                                                                     | 21<br>22<br>23<br>23<br>23<br>23                                                               |

|    | 2.3                               | Appro<br>2.3.1                   | Approximate Memory Circuits and Architectures         Approximate SRAM         Approximate DRAM | 25<br>25<br>25                                                                                 |

|    | 2.4<br>2.5                        |                                  | precision Computing                                                                             | 32<br>33                                                                                       |

| 3  | <b>App</b><br>3.1<br>3.2          | Introd                           | te Memory Support in Linux OS<br>uction                                                         | <ul> <li>39</li> <li>39</li> <li>40</li> <li>40</li> <li>41</li> <li>42</li> <li>46</li> </ul> |

|   |                          |                                                                                                                       | Page-level allocator (Buddy System algorithm)                                                                                                                                                                                                                                                                                                                         | 46<br>48                                                                                                                                                                                                                   |

|---|--------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                          |                                                                                                                       | Non Contiguous Memory Allocator vmalloc                                                                                                                                                                                                                                                                                                                               | 49                                                                                                                                                                                                                         |

|   | 3.3                      |                                                                                                                       | opment of approximate memory management in Linux Kernel .                                                                                                                                                                                                                                                                                                             | 50                                                                                                                                                                                                                         |

|   |                          | 3.3.1                                                                                                                 | Kernel compile-time configuration menu                                                                                                                                                                                                                                                                                                                                | 50                                                                                                                                                                                                                         |

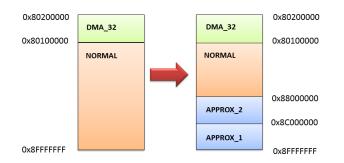

|   |                          | 3.3.2                                                                                                                 | Creation of ZONE_APPROXIMATE on 32-bit architectures                                                                                                                                                                                                                                                                                                                  | 51                                                                                                                                                                                                                         |

|   |                          |                                                                                                                       | ZONE_APPROXIMATE on x86 architectures                                                                                                                                                                                                                                                                                                                                 | 53                                                                                                                                                                                                                         |

|   |                          |                                                                                                                       | ZONE_APPROXIMATE on ARM architectures                                                                                                                                                                                                                                                                                                                                 | 56                                                                                                                                                                                                                         |

|   |                          |                                                                                                                       | ZONE_APPROXIMATE on RISC-V 32-bit architectures                                                                                                                                                                                                                                                                                                                       | 60                                                                                                                                                                                                                         |

|   |                          | 3.3.3                                                                                                                 | Approximate Memory and Early Boot Allocators                                                                                                                                                                                                                                                                                                                          | 61                                                                                                                                                                                                                         |

|   | 3.4                      |                                                                                                                       | tion in ZONE_APPROXIMATE                                                                                                                                                                                                                                                                                                                                              | 64                                                                                                                                                                                                                         |

|   |                          | 3.4.1                                                                                                                 | Approximate GFP Flags                                                                                                                                                                                                                                                                                                                                                 | 64                                                                                                                                                                                                                         |

|   |                          |                                                                                                                       | Alloc Fair policy                                                                                                                                                                                                                                                                                                                                                     | 66                                                                                                                                                                                                                         |

|   |                          | 3.4.2                                                                                                                 | User level approximate memory allocation                                                                                                                                                                                                                                                                                                                              | 67                                                                                                                                                                                                                         |

|   |                          | 3.4.3                                                                                                                 | Implementation of the device /dev/approxmem                                                                                                                                                                                                                                                                                                                           | 68                                                                                                                                                                                                                         |

|   |                          | 3.4.4                                                                                                                 | Approximate Memory Library: approx_malloc and approx_free                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                            |

|   |                          |                                                                                                                       | approx_malloc                                                                                                                                                                                                                                                                                                                                                         | 73                                                                                                                                                                                                                         |

|   |                          | o 4 F                                                                                                                 | approx_free                                                                                                                                                                                                                                                                                                                                                           | 74                                                                                                                                                                                                                         |

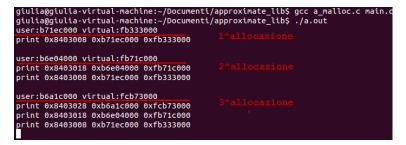

|   | 0 5                      | 3.4.5                                                                                                                 | Initial verification                                                                                                                                                                                                                                                                                                                                                  | 75                                                                                                                                                                                                                         |

|   | 3.5                      |                                                                                                                       | y Aware Approximate Memory Zones in Linux OS                                                                                                                                                                                                                                                                                                                          | 78                                                                                                                                                                                                                         |

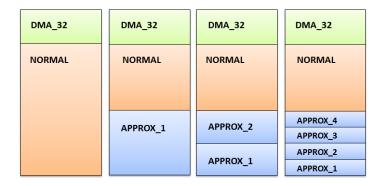

|   |                          | 3.5.1                                                                                                                 | Introduction and 64-bit implementation potentials                                                                                                                                                                                                                                                                                                                     | 78                                                                                                                                                                                                                         |

|   |                          | 3.5.2                                                                                                                 | Approximate memory zones on 64-bit architectures                                                                                                                                                                                                                                                                                                                      | 79                                                                                                                                                                                                                         |

|   |                          | 3.5.3                                                                                                                 | Data Allocation                                                                                                                                                                                                                                                                                                                                                       | 81                                                                                                                                                                                                                         |

|   |                          |                                                                                                                       | <i>approx library</i> for multiple approximate memory zone                                                                                                                                                                                                                                                                                                            | 82                                                                                                                                                                                                                         |

|   |                          | 3.5.4                                                                                                                 | Initial verification of the implementation                                                                                                                                                                                                                                                                                                                            | 83                                                                                                                                                                                                                         |

|   |                          |                                                                                                                       | ·                                                                                                                                                                                                                                                                                                                                                                     | 02                                                                                                                                                                                                                         |

|   |                          | 3.5.5                                                                                                                 | Verification and allocation tests                                                                                                                                                                                                                                                                                                                                     | 83                                                                                                                                                                                                                         |

| 4 |                          | 3.5.5<br>ropinQ                                                                                                       | Verification and allocation tests                                                                                                                                                                                                                                                                                                                                     | 89                                                                                                                                                                                                                         |

| 4 | 4.1                      | 3.5.5<br>ropinQ<br>Introd                                                                                             | Verification and allocation tests                                                                                                                                                                                                                                                                                                                                     | <b>89</b><br>89                                                                                                                                                                                                            |

| 4 | 4.1<br>4.2               | 3.5.5<br>ropinQ<br>Introd<br>Relate                                                                                   | Verification and allocation tests                                                                                                                                                                                                                                                                                                                                     | <b>89</b><br>89<br>90                                                                                                                                                                                                      |

| 4 | 4.1                      | 3.5.5<br><b>ropinQ</b><br>Introd<br>Relate<br>QEmu                                                                    | Verification and allocation tests                                                                                                                                                                                                                                                                                                                                     | <b>89</b><br>89<br>90<br>91                                                                                                                                                                                                |

| 4 | 4.1<br>4.2               | 3.5.5<br>ropinQ<br>Introd<br>Relate<br>QEmu<br>4.3.1                                                                  | Verification and allocation tests                                                                                                                                                                                                                                                                                                                                     | <b>89</b><br>89<br>90<br>91<br>91                                                                                                                                                                                          |

| 4 | 4.1<br>4.2               | 3.5.5<br>ropinQ<br>Introd<br>Relate<br>QEmu<br>4.3.1<br>4.3.2                                                         | Verification and allocation tests         Quo, Full System Emulator for Approximate Memory Platforms         uction         d Works: Simulation environments for digital platforms         t Emulator         Main Concepts         Dynamic Translation: Tiny Code Generator                                                                                          | <b>89</b><br>89<br>90<br>91<br>91<br>92                                                                                                                                                                                    |

| 4 | 4.1<br>4.2<br>4.3        | 3.5.5<br><b>ropinQ</b><br>Introd<br>Relate<br>QEmu<br>4.3.1<br>4.3.2<br>4.3.3                                         | Verification and allocation tests         Quo, Full System Emulator for Approximate Memory Platforms         uction         d Works: Simulation environments for digital platforms         t Emulator         Main Concepts         Dynamic Translation: Tiny Code Generator         QEmu SoftMMU                                                                     | <b>89</b><br>89<br>90<br>91<br>91<br>92<br>92                                                                                                                                                                              |

| 4 | 4.1<br>4.2               | 3.5.5<br>ropinQ<br>Introd<br>Relate<br>QEmu<br>4.3.1<br>4.3.2<br>4.3.3<br>Appro                                       | Verification and allocation tests                                                                                                                                                                                                                                                                                                                                     | <ul> <li>89</li> <li>90</li> <li>91</li> <li>91</li> <li>92</li> <li>93</li> </ul>                                                                                                                                         |

| 4 | 4.1<br>4.2<br>4.3        | 3.5.5<br><b>ropinQ</b><br>Introd<br>Relate<br>QEmu<br>4.3.1<br>4.3.2<br>4.3.3                                         | Verification and allocation tests         Quo, Full System Emulator for Approximate Memory Platforms         uction         d Works: Simulation environments for digital platforms         t Emulator         Main Concepts         Dynamic Translation: Tiny Code Generator         QEmu SoftMMU         eximate Memory in ApropinQuo         QEmu Memory Management | <ul> <li>89</li> <li>90</li> <li>91</li> <li>91</li> <li>92</li> <li>92</li> <li>93</li> <li>93</li> </ul>                                                                                                                 |

| 4 | 4.1<br>4.2<br>4.3        | 3.5.5<br>ropinQ<br>Introd<br>Relate<br>QEmu<br>4.3.1<br>4.3.2<br>4.3.3<br>Appro                                       | Verification and allocation tests                                                                                                                                                                                                                                                                                                                                     | <ul> <li>89</li> <li>90</li> <li>91</li> <li>91</li> <li>92</li> <li>93</li> </ul>                                                                                                                                         |

| 4 | 4.1<br>4.2<br>4.3        | 3.5.5<br>ropinQ<br>Introd<br>Relate<br>QEmu<br>4.3.1<br>4.3.2<br>4.3.3<br>Appro                                       | Verification and allocation tests                                                                                                                                                                                                                                                                                                                                     | <ul> <li>89</li> <li>90</li> <li>91</li> <li>91</li> <li>92</li> <li>93</li> <li>93</li> <li>94</li> </ul>                                                                                                                 |

| 4 | 4.1<br>4.2<br>4.3        | 3.5.5<br>ropinQ<br>Introd<br>Relate<br>QEmu<br>4.3.1<br>4.3.2<br>4.3.3<br>Appro                                       | Verification and allocation tests                                                                                                                                                                                                                                                                                                                                     | <ul> <li>89</li> <li>90</li> <li>91</li> <li>91</li> <li>92</li> <li>92</li> <li>93</li> <li>93</li> </ul>                                                                                                                 |

| 4 | 4.1<br>4.2<br>4.3        | 3.5.5<br>ropinQ<br>Introd<br>Relate<br>QEmu<br>4.3.1<br>4.3.2<br>4.3.3<br>Appro                                       | Verification and allocation tests                                                                                                                                                                                                                                                                                                                                     | <ul> <li>89</li> <li>89</li> <li>90</li> <li>91</li> <li>91</li> <li>92</li> <li>93</li> <li>93</li> <li>94</li> <li>95</li> </ul>                                                                                         |

| 4 | 4.1<br>4.2<br>4.3        | 3.5.5<br>ropinQ<br>Introd<br>Relate<br>QEmu<br>4.3.1<br>4.3.2<br>4.3.3<br>Appro                                       | Verification and allocation tests                                                                                                                                                                                                                                                                                                                                     | <ul> <li>89</li> <li>90</li> <li>91</li> <li>91</li> <li>92</li> <li>93</li> <li>93</li> <li>94</li> </ul>                                                                                                                 |

| 4 | 4.1<br>4.2<br>4.3        | 3.5.5<br>ropinQ<br>Introd<br>Relate<br>QEmu<br>4.3.1<br>4.3.2<br>4.3.3<br>Appro                                       | Verification and allocation tests                                                                                                                                                                                                                                                                                                                                     | <ul> <li>89</li> <li>89</li> <li>90</li> <li>91</li> <li>92</li> <li>92</li> <li>93</li> <li>93</li> <li>94</li> <li>95</li> <li>97</li> </ul>                                                                             |

| 4 | 4.1<br>4.2<br>4.3        | 3.5.5<br>ropinQ<br>Introd<br>Relate<br>QEmu<br>4.3.1<br>4.3.2<br>4.3.3<br>Appro<br>4.4.1                              | Verification and allocation tests                                                                                                                                                                                                                                                                                                                                     | <ul> <li>89</li> <li>89</li> <li>90</li> <li>91</li> <li>92</li> <li>92</li> <li>93</li> <li>93</li> <li>94</li> <li>95</li> <li>97</li> <li>97</li> </ul>                                                                 |

| 4 | 4.1<br>4.2<br>4.3<br>4.4 | 3.5.5<br><b>ropinQ</b><br>Introd<br>Relate<br>QEmu<br>4.3.1<br>4.3.2<br>4.3.3<br>Appro<br>4.4.1<br>4.4.2              | Verification and allocation tests                                                                                                                                                                                                                                                                                                                                     | <ul> <li>89</li> <li>89</li> <li>90</li> <li>91</li> <li>91</li> <li>92</li> <li>93</li> <li>93</li> <li>94</li> <li>95</li> <li>97</li> <li>98</li> </ul>                                                                 |

| 4 | 4.1<br>4.2<br>4.3        | 3.5.5<br>ropinQ<br>Introd<br>Relate<br>QEmu<br>4.3.1<br>4.3.2<br>4.3.3<br>Appro<br>4.4.1                              | Verification and allocation tests                                                                                                                                                                                                                                                                                                                                     | <ul> <li>89</li> <li>89</li> <li>90</li> <li>91</li> <li>92</li> <li>93</li> <li>93</li> <li>94</li> <li>95</li> <li>97</li> <li>97</li> <li>98</li> <li>101</li> </ul>                                                    |

| 4 | 4.1<br>4.2<br>4.3<br>4.4 | 3.5.5<br><b>ropinQ</b><br>Introd<br>Relate<br>QEmu<br>4.3.1<br>4.3.2<br>4.3.3<br>Appro<br>4.4.1<br>4.4.2              | Verification and allocation tests                                                                                                                                                                                                                                                                                                                                     | <ul> <li>89</li> <li>89</li> <li>90</li> <li>91</li> <li>92</li> <li>92</li> <li>93</li> <li>93</li> <li>94</li> <li>95</li> <li>97</li> <li>98</li> <li>101</li> <li>101</li> </ul>                                       |

| 4 | 4.1<br>4.2<br>4.3<br>4.4 | 3.5.5<br>ropinQ<br>Introd<br>Relate<br>QEmu<br>4.3.1<br>4.3.2<br>4.3.3<br>Appro<br>4.4.1<br>4.4.2<br>Error i<br>4.5.1 | Verification and allocation tests                                                                                                                                                                                                                                                                                                                                     | <ul> <li>89</li> <li>89</li> <li>90</li> <li>91</li> <li>92</li> <li>93</li> <li>93</li> <li>94</li> <li>95</li> <li>97</li> <li>98</li> <li>101</li> <li>101</li> <li>104</li> </ul>                                      |

| 4 | 4.1<br>4.2<br>4.3<br>4.4 | 3.5.5<br>ropinQ<br>Introd<br>Relate<br>QEmu<br>4.3.1<br>4.3.2<br>4.3.3<br>Appro<br>4.4.1<br>4.4.2<br>Error i<br>4.5.1 | Verification and allocation tests                                                                                                                                                                                                                                                                                                                                     | <ul> <li>89</li> <li>89</li> <li>90</li> <li>91</li> <li>92</li> <li>92</li> <li>93</li> <li>94</li> <li>95</li> <li>97</li> <li>97</li> <li>98</li> <li>101</li> <li>104</li> <li>104</li> </ul>                          |

| 4 | 4.1<br>4.2<br>4.3<br>4.4 | 3.5.5<br>ropinQ<br>Introd<br>Relate<br>QEmu<br>4.3.1<br>4.3.2<br>4.3.3<br>Appro<br>4.4.1<br>4.4.2<br>Error i<br>4.5.1 | Verification and allocation tests                                                                                                                                                                                                                                                                                                                                     | <ul> <li>89</li> <li>89</li> <li>90</li> <li>91</li> <li>92</li> <li>92</li> <li>93</li> <li>93</li> <li>94</li> <li>95</li> <li>97</li> <li>97</li> <li>98</li> <li>101</li> <li>104</li> <li>104</li> <li>105</li> </ul> |

|   | 4.6  | Quality aware selective ECC for approximate DRAM and model               | 107 |

|---|------|--------------------------------------------------------------------------|-----|

|   |      | 4.6.1 Bit dropping for LSBs, bit reuse and selective ECC                 |     |

|   |      | 4.6.2 Quality aware selective ECC                                        | 108 |

|   |      | ECC codes for approximate memories                                       | 108 |

|   |      | 4.6.3 Impact of bit dropping and bit reuse                               | 109 |

|   |      | 4.6.4 Implementation                                                     |     |

|   | 4.7  | Verification of fault models                                             | 111 |

|   |      | 4.7.1 Error on access models verification                                | 111 |

|   |      | 4.7.2 DRAM orientation model verification                                |     |

|   |      | 4.7.3 Bit dropping model verification                                    | 112 |

| 5 | Evn  | loiting approximate memory in applications and results                   | 115 |

| 9 | 5.1  |                                                                          |     |

|   | 5.2  | Impact of Approximate Memory on a H.264 Software Video Encoder           |     |

|   | 0.2  | 5.2.1 H.264 video encoding and the x264 encoder                          |     |

|   |      | H.264 Encoder                                                            |     |

|   |      | H.264 Decoder                                                            |     |

|   |      | H.264 data fault resilience                                              |     |

|   |      | The <i>x</i> 264 software video encoder                                  |     |

|   |      | Analysis of <i>x</i> 264 heap memory usage                               |     |

|   |      | 5.2.2 Approximate memory data allocation for the <i>x</i> 264 encoder    |     |

|   |      | 5.2.3 Experimental setup                                                 |     |

|   |      | 5.2.4 Impact on output using approximate DRAM and power sav-             |     |

|   |      | ing considerations                                                       | 124 |

|   |      | Power saving considerations                                              |     |

|   |      | 5.2.5 Impact on output using approximate SRAM                            |     |

|   |      | 5.2.6 Considerations on the results and possible future analysis         |     |

|   | 5.3  | Study of the impact of approximate memory on a digital FIR filter design |     |

|   |      | Impact on output using approximate DRAM                                  |     |

|   |      | Impact on output using approximate SRAM                                  |     |

|   |      | Impact on output using approximate SRAM with bit dropping                |     |

|   | 5.4  |                                                                          | 102 |

|   | 0.1  | ital FIR filtering                                                       | 133 |

|   |      |                                                                          |     |

| 6 |      | thesis Time Reconfigurable Floating Point Unit for Transprecision Com    |     |

|   | puti |                                                                          | 137 |

|   | 6.1  | Introduction and previous works                                          |     |

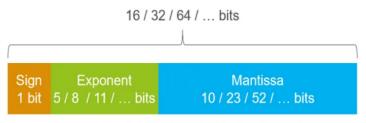

|   | 6.2  | Floating Point representation, IEEE-754 standard                         |     |

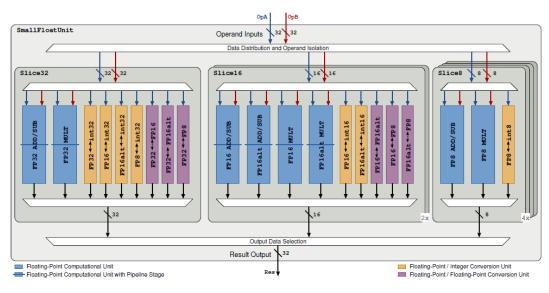

|   | 6.3  | Design of the reconfigurable Floating Point Unit                         |     |

|   | 6.4  | 6.3.1 Top unit Floating_Point_Unit_core                                  |     |

|   | 6.4  | Experimental Results                                                     |     |

|   |      | 6.4.1 Testing                                                            |     |

|   |      | 6.4.2Synthesis Setup                                                     |     |

|   |      |                                                                          |     |

|   |      | Number of gates and resources       Propagation delay and speed          |     |

|   |      |                                                                          |     |

|   | 65   | Conclusion and Future works                                              |     |

|   | 0.0  |                                                                          | 14/ |

| 7  | Conclusion                                                            | 149 |

|----|-----------------------------------------------------------------------|-----|

|    | 7.1 Approximate Memory management within the Linux Kernel             | 149 |

|    | 7.2 Models and emulator for microprocessor platforms with approximate |     |

|    | memory                                                                |     |

|    | 7.3 Impact of approximate memory allocation on ETAs                   |     |

|    | 7.4 Transprecision FPU implementation                                 | 153 |

| A  | Linux kernel files for approximate memory support                     | 155 |

|    | A.1 Patched Kernel files                                              | 155 |

|    | A.2 New Kernel source files                                           | 156 |

|    | A.3 Approximate Memory Configuration (Make menuconfig)                | 156 |

| B  | AppropinQuo: list of approximate memory models                        | 157 |

|    | B.0.1 QEmu 2.5.1 patched files for approximate memory support         | 157 |

|    | B.0.2 New QEmu 2.5.1 source files                                     | 157 |

| C  | Transprecision FPU: list of vhd files                                 | 159 |

| D  | Publications and Presentations                                        | 161 |

| Bi | bliography                                                            | 163 |

xii

# **List of Figures**

| 1.1  | Dennard scaling and power consumption models. Source: Hennessy,               |    |

|------|-------------------------------------------------------------------------------|----|

| 1.0  | 2018                                                                          | 1  |

| 1.2  | Moore's law. Source:                                                          | 2  |

| 1.3  | Amdahl's law. Source:                                                         | 3  |

| 1.4  | Dark silicon:end of multicore era. Source: Hardavellas et al., 2011           | 4  |

| 1.5  | Power trends. Source: [Burns, 2016]                                           | 5  |

| 1.6  | Power trends. Source: [Energy Aware Scheduling]                               | 6  |

| 1.7  | Low power strategies at different abstraction levels. Source: [Gupta          | -  |

|      | and Padave, 2016]                                                             | 7  |

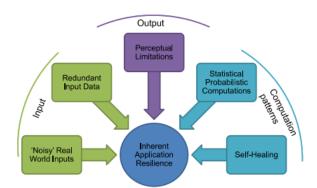

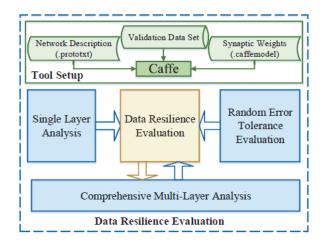

| 2.1  | Overview of ASAC framework. Source: Roy et al., 2014                          | 12 |

| 2.2  | Overview of ARC framework. Source: Chippa et al., 2013                        | 13 |

| 2.3  | Overview of EnerJ language extension. Source: Sampson et al., 2011            | 14 |

| 2.4  | ISA extension for AxC support. Source: Esmaeilzadeh et al., 2012              | 15 |

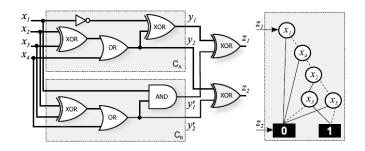

| 2.5  | Examples of ETAs                                                              | 15 |

| 2.6  | Possible sources of application error resilience .Source: Chippa et al., 2013 | 16 |

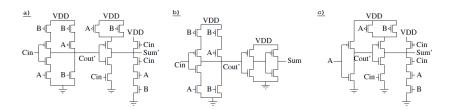

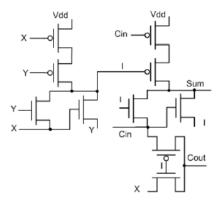

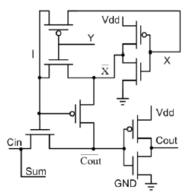

| 2.7  | a) simplified MA, b) approximation 1, c) approximation 2. Source:Gupta        |    |

|      | et al., 2011                                                                  | 17 |

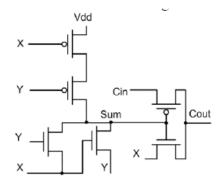

| 2.8  | Design of exact full adder, 10 transistors. Source: Yang et al., 2013         | 17 |

| 2.9  | Design of AXA1, 8 transistors. Source: Yang et al., 2013                      | 18 |

| 2.10 | Design of AXA2, 6 transistors. Source: Yang et al., 2013                      | 18 |

|      | Design of AXA3, 8 transistors .Source: Yang et al., 2013                      | 18 |

|      | Comparison between AXA1, AXA2, AXA3 and exact full adder .Source:             |    |

|      | Yang et al., 2013                                                             | 19 |

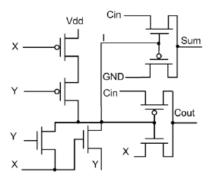

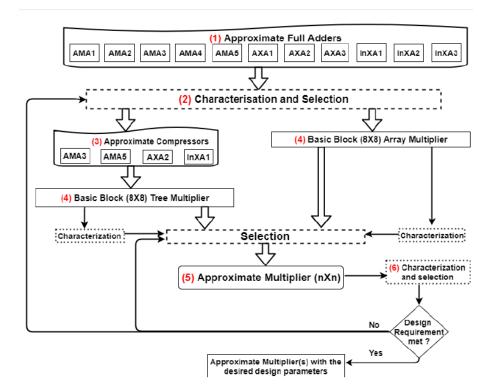

| 2.13 | Overview of approximate multipliers comparison. Source: Masadeh,              |    |

|      | Hasan, and Tahar, 2018                                                        | 19 |

| 2.14 | Overview of different approximate FA properties. Source: Masadeh,             |    |

|      | Hasan, and Tahar, 2018                                                        | 20 |

| 2.15 | Reduced Precision Redundancy ANT Block Diagram. Source: Pagliari              |    |

|      | et al., 2015                                                                  | 21 |

| 2.16 | Determining the Hamming distance of two combinational circuits us-            |    |

|      | ing a Binary Decision Diagrams (BDD). Source : Vasicek and Sekan-             |    |

|      | ina, 2016                                                                     | 22 |

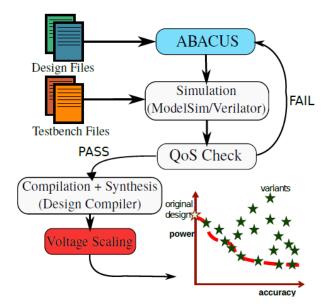

| 2.17 | Integration of ABACUS in a traditional design flow. Source : Nepal            |    |

|      | et al., 2014                                                                  | 23 |

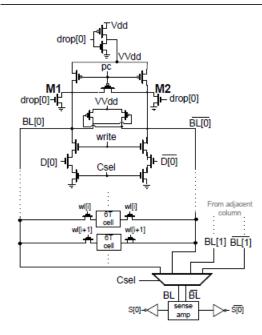

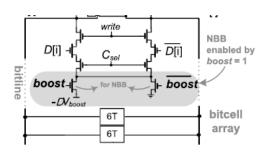

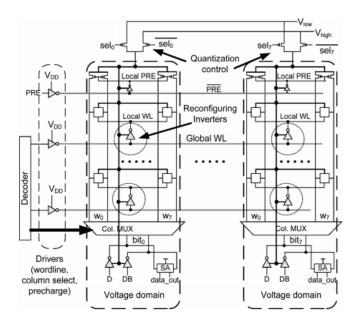

|      | SRAM bit dropping precharge circuit. Source: Frustaci et al., 2016            | 27 |

|      | Sram SNBB precharge circuit. Source: Frustaci et al., 2016                    | 27 |

|      | Architecture of dual $V_{dd}$ memory array. Source : Cho et al., 2011         | 28 |

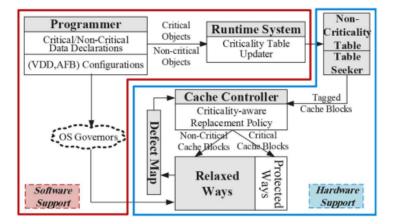

| 2.21 | Overview of HW/SW components for approximated caches. Source :                |    |

|      | Shoushtari, BanaiyanMofrad, and Dutt, 2015                                    | 28 |

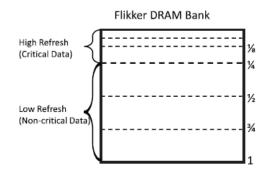

| 2.22 | RAIDR implementation. Source : Liu et al., 2012a                              | 29 |

| 2.23 | Proposed DRAM partitioning according to refresh rate. Source : Liu     |    |

|------|------------------------------------------------------------------------|----|

|      | et al., 2012b                                                          | 29 |

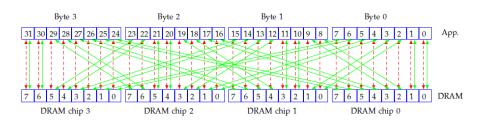

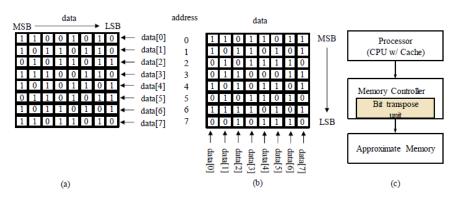

| 2.24 | Proposed mapping of bits of 4 DRAM chips. Source : Lucas et al., 2014  | 30 |

|      | Proposed quality bins. Source : Raha et al., 2017                      | 30 |

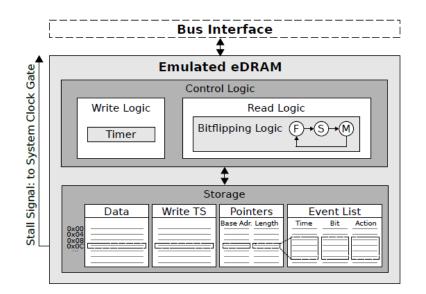

| 2.26 | eDRAM emulator: block diagram. Source: Widmer, Bonetti, and Burg,      |    |

|      | 2019                                                                   | 31 |

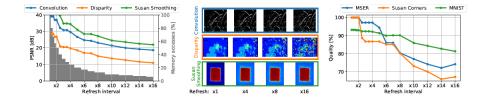

| 2.27 | Benchmarks output quality for refuced refresh rate. Source: Widmer,    |    |

|      | Bonetti, and Burg, 2019                                                | 32 |

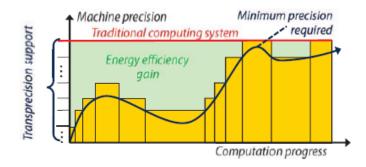

| 2.28 | Transprecision Computing paradigm. Source : Malossi et al., 2018       | 32 |

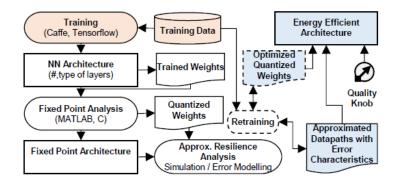

|      | Methodology for designing energy-effcient and adaptive neural net-     |    |

| ,    | work accelerator-based architectures for Machine Learning. Source:     |    |

|      | Shafique et al., 2017a                                                 | 33 |

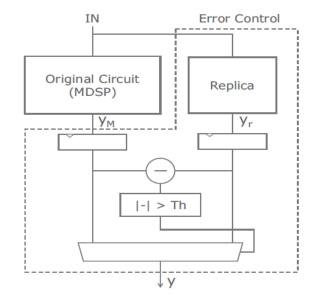

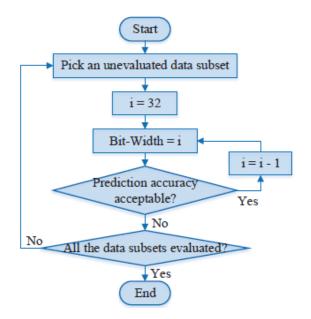

| 2 30 | Overview of DRE. Source : Chen et al., 2017                            | 35 |

|      | Flow of Single Layer Analysis. Source: Chen et al., 2017               | 35 |

|      | Approximate memory architecture; (a) conventional data storage scheme  |    |

| 2.32 |                                                                        | ,  |

|      | (b) approximate data storage scheme, (c) system architecture to sup-   | 26 |

| 0.00 | port approximate memory access. Source: Nguyen et al., 2018            | 36 |

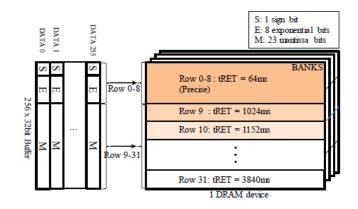

| 2.33 | Row-level refresh scheme for approximate DRAM. Source: Nguyen          | ~= |

|      | et al., 2018                                                           | 37 |

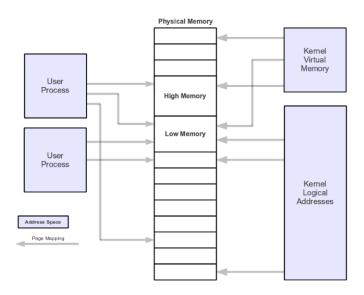

| 3.1  | Kernel address space and User process address space                    | 42 |

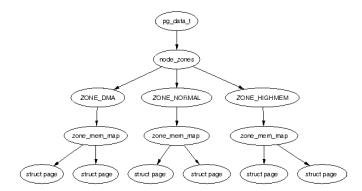

| 3.2  | Nodes, Zones and Pages. Source:[Gorman, 2004]                          | 42 |

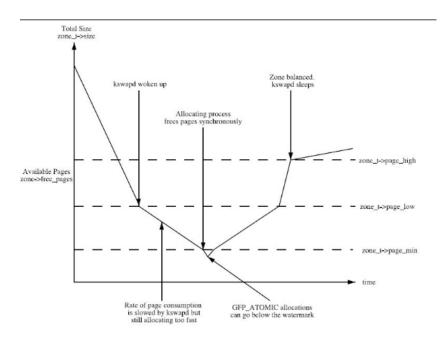

| 3.3  | Zone watermarks                                                        | 44 |

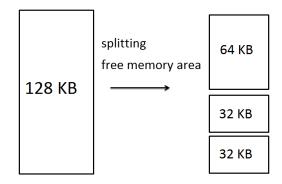

| 3.4  | Buddy system allocator                                                 | 46 |

| 3.5  | The linear address interval starting from PAGE_OFFSET. Source: [Bovet, | 10 |

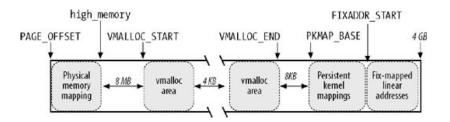

| 0.0  | 2005]                                                                  | 50 |

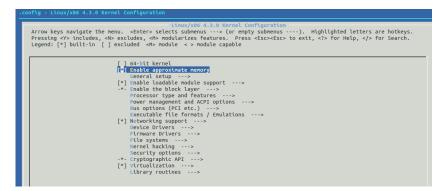

| 3.6  | Example of menuconfig menu for x86 architecture                        | 51 |

| 3.7  | Output of <i>dmesg</i> command                                         | 57 |

| 3.8  | Output of <i>cat /proc/zoneinfo</i> command                            | 57 |

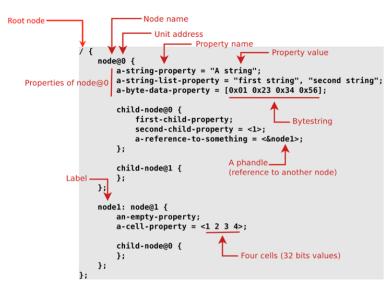

| 3.9  | Device tree structure                                                  | 58 |

| 3.10 | Example of approximate memory node in DTB file                         | 59 |

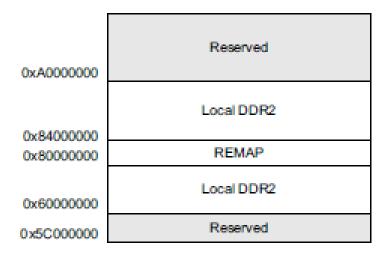

|      | Vexpress Cortex A9 board memory map (extract)                          | 60 |

|      | On left: kernel boot logs. On right: zone_approximate statistics       | 60 |

|      | RISC-V Boot messages                                                   | 61 |

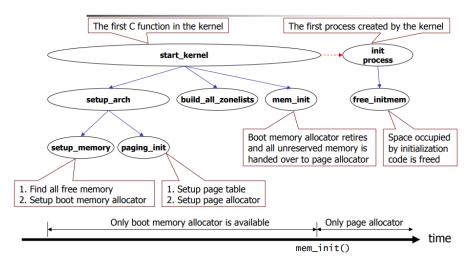

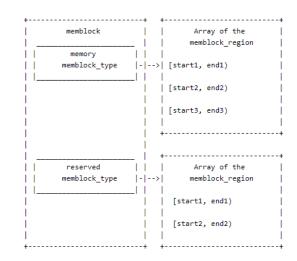

| 2.14 | Overview of memory allocators. Source:[Liu, 2010]                      | 62 |

|      |                                                                        | 63 |

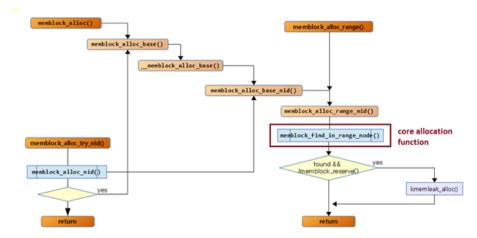

|      | Memblock memory allocation                                             | 63 |

|      | Memblock allocator function tree                                       |    |

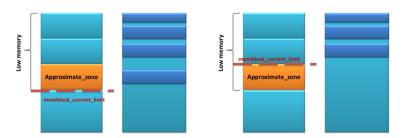

|      | Memblock current limit on architectures with ZONE_APPROXIMATE          | 64 |

|      | Output of <i>cat /proc/zoneinfo</i> command                            | 64 |

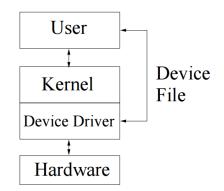

|      | Device driver interaction                                              | 68 |

|      | Creation of device approxmem                                           | 73 |

|      | Bulding the linked list                                                | 76 |

|      | <i>vmallocinfo</i> messages on x86 architecture                        | 76 |

|      | Messages of cat / proc / pid / maps                                    | 77 |

| 3.24 | ZONE_APPROXIMATE statistics after boot                                 | 77 |

| 3.25 | ZONE_APPROXIMATE statistics after <i>approx_malloc</i> call            | 77 |

| 3.26 | Configuration of physical memory layout                                | 81 |

| 3.27 | Configuration of physical memory layout on RISC-V SiFiveU              | 83 |

| 3.28 | Boot messages printing the physical memory layout                      | 84 |

|      | Kernel boot messages for RISCV 64 platform with 4 approximate mem-     |    |

|      | ory zones                                                              | 84 |

|      | ZONE_APPROXIMATE statistics after <i>approx_malloc</i> call                                |     | 86  |

|------|--------------------------------------------------------------------------------------------|-----|-----|

|      | ZONE_APPROXIMATE2 statistics after <i>approx_malloc</i> call                               |     | 87  |

|      | ZONE_APPROXIMATE3 statistics after approx_malloc call                                      |     | 87  |

| 3.33 | ZONE_APPROXIMATE4 statistics after approx_malloc call                                      | •   | 87  |

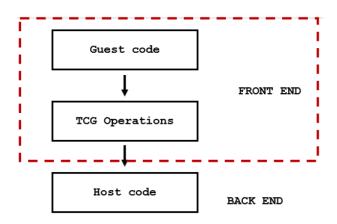

| 4.1  | Tiny Code Generator                                                                        |     | 92  |

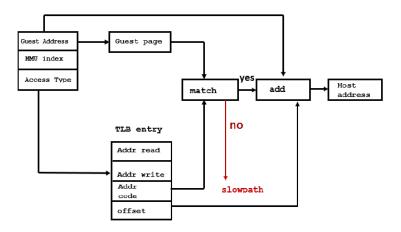

| 4.2  | QEmu SoftMMU                                                                               | •   | 93  |

| 4.3  | e820 Bios Memory Mapping passed to Linux Kernel                                            | •   | 96  |

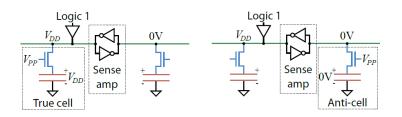

| 4.4  | DRAM true cell and anti cell. Source:Liu et al., 2013                                      | . 1 | .02 |

| 4.5  | Error on Read debug messages produced during execution                                     | . 1 | 05  |

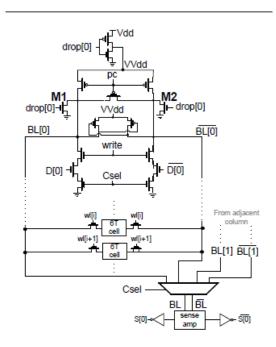

| 4.6  | SRAM precharge circuit for bit-dropping technique. Source:Frustaci                         | 1   | 07  |

| 4 7  | et al., 2015a                                                                              |     |     |

| 4.7  | Example of Looseness Mask on Big Endian architecture                                       |     |     |

| 4.8  | 32 bit ECC data format in approximate memory                                               | . 1 | 10  |

| 5.1  | H.264 high level coding/decoding scheme                                                    | . 1 | 17  |

| 5.2  | H.264 inter-frame and intra-frame prediction                                               | . 1 | 17  |

| 5.3  | x264 encoding information                                                                  | . 1 | 19  |

| 5.4  | Memory allocation profiling: Massif output                                                 | . 1 | 20  |

| 5.5  | x264, output frame with different Looseness Levels and fault rate $10^{-4}$                |     |     |

|      | $[errors/(bit \times s)]  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | . 1 | 25  |

| 5.6  | x264, output frame with different Looseness Levels and fault rate $10^{-3}$                |     |     |

|      | $[errors/(bit \times s)]  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ |     |     |

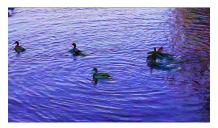

| 5.7  | Video Output PSNR graph [dB]                                                               |     |     |

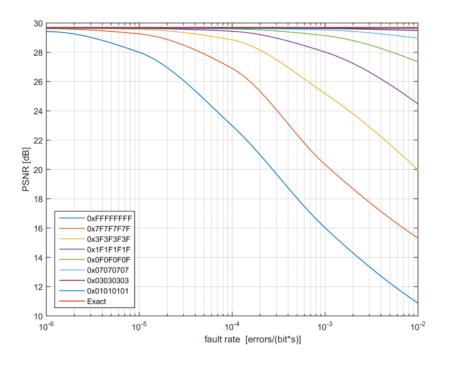

| 5.8  | DRAM cell retention time distribution. Source:Liu et al., 2012a                            | . 1 | 27  |

| 5.9  | x264, output frame coded with exact (top left) and approximate SRAM                        |     |     |

|      | (0xFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF                                                    |     |     |

|      | left) and $10^{-2}$ (bottom right) [ <i>errors</i> /access]                                |     |     |

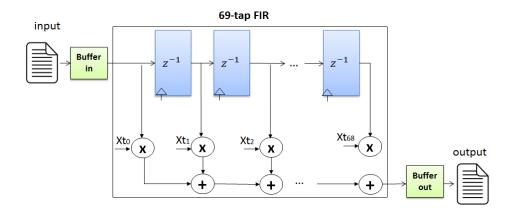

|      | Digital FIR architecture                                                                   |     |     |

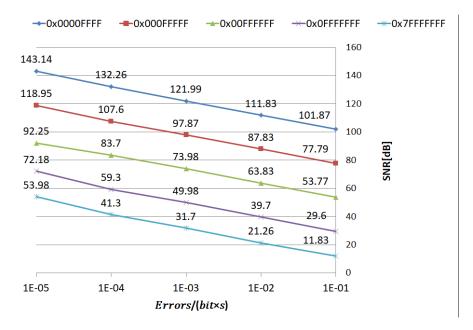

| 5.11 | FIR, output SNR [ <i>dB</i> ] for approximate DRAM (anti cells)                            | . 1 | 32  |

| 6.1  | Block diagram of the FPU hardware datapath. Source: [Tagliavini et                         |     |     |

|      | al., 2018]                                                                                 | . 1 | 38  |

| 6.2  | IEEE 754 Precision formats                                                                 | . 1 | 39  |

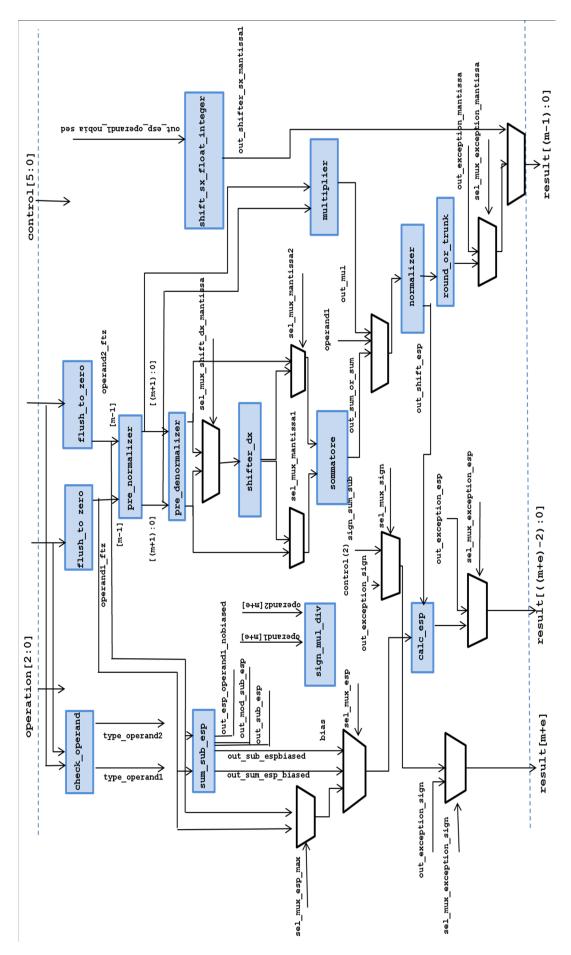

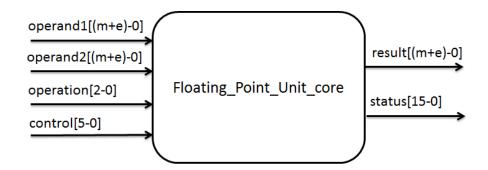

| 6.3  | Floating Point Unit Core architecture                                                      | . 1 | 41  |

| 6.4  | External interface of FPU core                                                             |     |     |

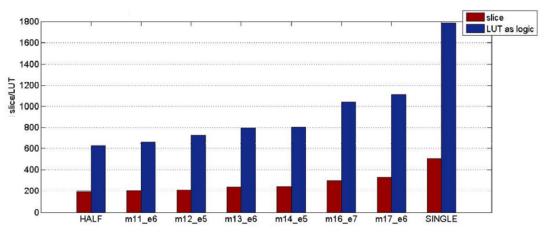

| 6.5  | Resources with DSP disabled @40MHz                                                         | . 1 | 45  |

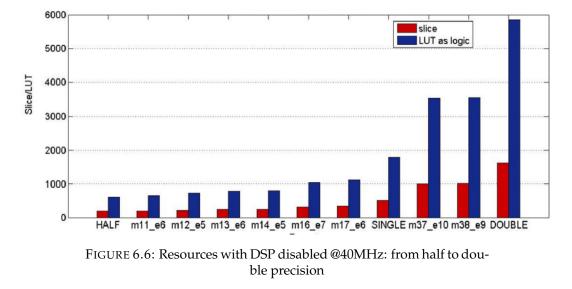

| 6.6  | Resources with DSP disabled @40MHz: from half to double precision                          | . 1 | 46  |

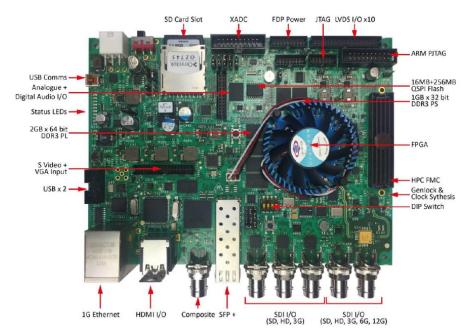

| 7.1  | Omnitek board where approximate DRAM cells could be introduced                             | . 1 | 51  |

## List of Tables

| 3.1  | DMA zone, physical ranges                                                        |

|------|----------------------------------------------------------------------------------|

| 3.2  | 32-bit x86 architecture memory layout                                            |

| 3.3  | 32-bit x86 memory layout with ZONE_APPROXIMATE                                   |

| 4.1  | List of Hamming codes                                                            |

| 4.2  | FIR, output SNR [ <i>dB</i> ]                                                    |

| 4.3  | BER for 32 bit data in approximate memory                                        |

| 4.4  | <i>bench_access</i> results, fixed Looseness Level                               |

| 4.5  | <i>bench_spontaneous_error</i> results (Wait time $t = 1000ms$ )                 |

| 4.6  | <i>bench_dropping</i> results                                                    |

| = 4  | 110                                                                              |

| 5.1  | Heap memory usage                                                                |

| 5.2  | Test videos from derf's collection                                               |

| 5.3  | Video Output PSNR [dB]         126                                               |

| 5.4  | x264, video output PSNR [ <i>dB</i> ] for approximate DRAM (true cells) 126      |

| 5.5  | x264, video output PSNR [ <i>dB</i> ] for approximate SRAM (error on access) 128 |

| 5.6  | FIR, output SNR [ <i>dB</i> ] for SRAM                                           |

| 5.7  | FIR, SNR $[dB]$ for SRAM bit dropping                                            |

| 5.8  | FIR, access count on approximate data structures                                 |

| 5.9  | FIR, output SNR [ <i>dB</i> ] for SRAM, EOR                                      |

| 5.10 | FIR, output SNR $[dB]$ for SRAM, EOW                                             |

| 6.1  | Operation codes                                                                  |

| 6.2  | List of analyzed formats                                                         |

| 6.3  | Resources @ 40MHz clock with DSP disabled                                        |

| 6.4  | Propagation delay for reduced precision FP formats                               |

| 6.5  | Power consumption @40MHz                                                         |

|      | I I I I I I I I I I I I I I I I I I I                                            |

## List of Abbreviations

AxC **Approximate Computing** AxM Approximate Memory Algorithmic Noise Tolerance ANT BDD **B**inary **D**ecision **D**iagram Bit Error Rate BER **CNN C**onvolutional Neural Network CPS Cyber Physical System CS Chip Select DCT **Discret Cosin Transform** DMA **Direct Memory Access** DNN **Deep Neural Network** DPM Dynamic Power Managment DRAM Dynamic Random Acess Memory DRT Data Retention Time eDRAM embedded Dynamic Random Acess Memory ECC Error Correction Code EOR Error On Read EOW Error On Write ER Error Rate ES **Error Significance** EAS Energy Aware Scheduler ETA **Error Tolerant Application** FA Full Adder FIR Finite Impulse Response GFP Get Free Page HPC High Performance Computing **H**ardWare HW IoE Internet of Everything IoT Internet of Things Instruction Set Architecture ISA LSB Least Significant Bit Mirror Adder MA ML Machine Learning Memory Management Unit MMU MSB Most Significant Bit Mean Squared Error **MSE** NBB Negative Bitline Boosting **O**perating **S**ystem OS PDP Power Delay Product **PSNR** Peak Signal to Noise Ratio PULP Processor Ultra Low Power Quality of Service OoS RM Read Margin

| RTL  | Register Transfer Level             |

|------|-------------------------------------|

| RPR  | Reduced Precision Format            |

| SoC  | System on Chip                      |

| SSIM | Structural SIMilarity               |

| SNBB | Selective Negative Bitline Boosting |

| SNR  | Signal to Noise Ratio               |

| SRAM | Static Random Acess Memory          |

| SW   | SoftWare                            |

| TCG  | Tiny Code Generator                 |

| TS   | Training Set                        |

| VLSI | Very Large Scale Integration        |

| VGG  | Visual Geometry Group               |

| WM   | Write Margin                        |

|      |                                     |

To my dearest affections, for always being by my side. To myself for the constancy and commitment to achieve this goal, for trying and being successful.

## Chapter 1

## Introduction

## 1.1 Need for Low Power Circuit Design

In the past, during the so-called desktop PC era, the main goal of VLSI design was to develop systems capable of satisfying and optimizing real time processing requirements, computational speed and graphics quality in applications such as video compression, games and graphics. With the advancement of VLSI technology, digital systems have increased in complexity and three factors have come to convergence making energy efficiency the most important constraint:

• *Technology*. From a technological point of view, excessive energy consumption has become the limiting factor in integrating multiple transistors on a single chip or a multi-chip module, determining the end of the *Dennard scaling* law (Fig. 1.4).

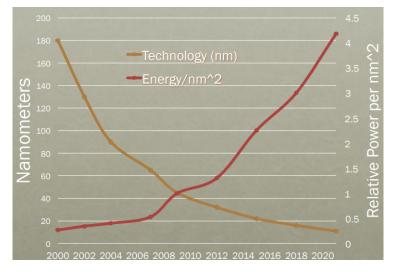

FIGURE 1.1: Dennard scaling and power consumption models. Source: Hennessy, 2018

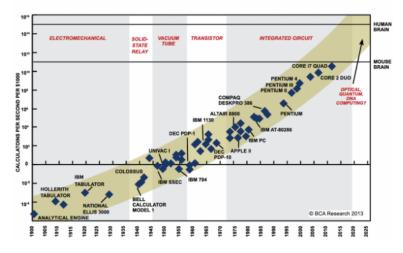

The latter, also known as *MOSFET scaling* (1977), claims that as the transistors shrink in size, the power density stays constant; meaning indeed that the power consumption is proportional to the chip area. This law allowed chipmakers to increase clock speed of processors over years without increasing power. However, the MOSFET scaling, which held from 1977 to 1997, became fading between 1997 to 2006 until it collapsed rapidly in 2007 when the transistors became so small that the increased leakage started overheating the chip and preventing processors from clocking up further. In these years there has been also a slowdown in *Moore's law* (Fig. 1.2), according to which the number of devices in a chip doubles every 18 months [Platt, 2018]. In facts, with the end of Dennard's law process technology scaling can continue to allow the duplication of the number of transistor for every generation, but without getting a significant improvement in switching speed and energy efficiency of transistors. As the number of transistors increased, also energy consumption raising followed. Technology scaling, while involving a reduction of supply voltage (0.7 scaling factor) and a reduction in the die area (0.5 scaling factor), started increasing parasitic capacities of about 43%, meaning that the power density increases by 40% with each generation [*Low Power Design in VLSI*].

FIGURE 1.2: Moore's law. Source:

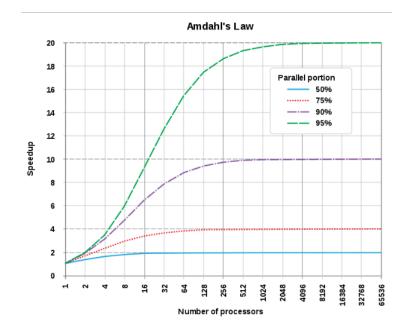

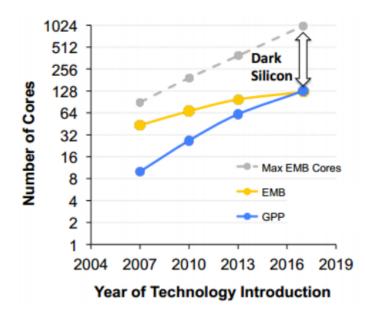

- *Architecture*. The limitations and inefficiencies in exploiting instruction level parallelism (dominant approach from 1982 to 2005) has led to the end of single-processor era. Moreover the *Amdahl's Law* (Fig. 1.3), which aims to predict the theoretical maximum speedup for programs using multiple processors, and its implications ended the 'easy' multicore era. Citing this law: *"the effort expended on achieving high parallel processing rates is wasted unless it is accompanied by achievements in sequential processing rates of very nearly the same magnitude"* [Amdahl, 1967]. In [Esmaeilzadeh et al., 2013] it is also shown that, as the number of cores increases, constraints on power consumption can prevent all the cores from being powered at maximum speed, determining a fraction of cores which are always powered off (*dark silicon*). At 22 nm the 21% of a fixed-size chip must be "*dark*", and, with ITRS projections, at 8 nm, this number can grow up to more than 50%.

- *Application focus shift*. The transition from desktop PC to individual, mobile devices and ultrascale cloud computing determines the definition of new constraints. The advent of the Big Data era, IoT technologies, IoE and CPS have led to increasing demand for data processing, storage and transmission: modern digital systems are required to interact continuously with the external physical world, satisfying not only requirements on high performance capabilities but also specific constraints on energy and power consumption.

FIGURE 1.3: Amdahl's law. Source:

Power consumption therefore has become an essential constraint in portable devices, in order to take advantage of real time execution times having minimum possible requirements on weight, battery life and physical dimensions due to battery size. As an example, we can consider that almost 70% of users look for longer talk times and battery lasting times as a key feature for mobile phones [Natarajan et al., 2018]. Moreover, power consumption impacts significantly the design of VLSI circuits since users of mobile devices continue to demand:

- mobility: Nowadays consumers continue to request smaller and sleeker mobile devices. To support these features, high level silicon integration processes are required, which, in turn, determines high levels of leakage. Hence the need to find a strategy to reduce powr cinsumption and in particular leakage currents.

- portability: battery life is impacted by energy consumed per task; moreover a second order effect is that effective battery energy capacity is decreased by higher drawing current that causes IR drops in power supply voltage. To overcome this issue, more power/ground pins are required to reduce the resistance R and also thicker/wider on-chip metal wires or dedicated metal layers are necessary.

- *reliability*. Power dissipated as heat reduces speed and reliability since high power systems tend to run hot and the temperature can exacerbate several silicon failure mechanisms. More expensive packaging and cooling systems are indeed required.

## **1.2** Source of Power Dissipation

The sources of power dissipation in a CMOS device are expressed by the elements of the following equation:

FIGURE 1.4: Dark silicon:end of multicore era. Source: Hardavellas et al., 2011

$TotalPowerP = P_{dynamic} + P_{short-circuit} + P_{leakage} + P_{static}$

In particular:

• Dynamic power or switching power:

$$P = \alpha C V^2 f$$

where *P* corresponds to the power, *C* is the effective switch capacitance which is a function of gate fan-out, wire length and transistor size, *V* is the supply voltage, *f* is the frequency of operation and  $\alpha$  the switching activity factor. It corresponds to the power dissipated by charging/discharging the parasitic capacitors of each circuit node.

• P<sub>short-circuit</sub>:

$$P = I_{short}V$$

which is produced by the direct path between supply rails during switching. In particular both pull-down (n-MOS) and pull-up (p-MOS) networks may be momentarily ON simultaneously leading to an impulse of short-circuit current.

• P<sub>leakage</sub>:

$$P = I_{leakage} V$$

which is mainly determined by the fabrication technology. There are many sources that contribute to the leakage power, such as gate leakage, junction leakage, sub-threshold conduction. It occurs even when the system is idle or in standby mode. The leakage power, which is the dominant component in static energy consumption, was mainly neglected until 2005 when, in correspondence with the 65nm technology step, further scaling of threshold voltage

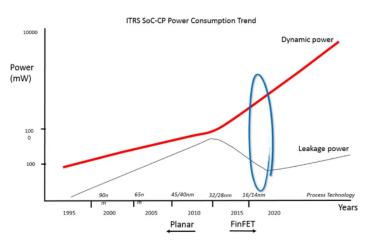

has extremely increased the sub-threshold leakage currents (Fig. 1.5). It is expected that this kind of power will increase 32 times per device by 2020 [Roy and Prasad, 2009].

• P<sub>static</sub>:

$$P = I_{static}V$$

which is determined by the constant current from  $V_{dd}$  the ground (standby power).

FIGURE 1.5: Power trends. Source: [Burns, 2016]

## **1.3 Approximate Computing**

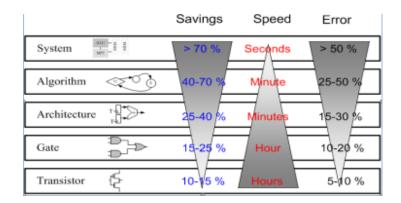

The problems caused by the sharp increase in power densities of SoC, due to the interruption of Dennard's downsizing law, prompted the search for new solutions. There are different strategies that can be applied for reducing power consumption at different levels of the VLSI design flow [Gupta and Padave, 2016, R., 2016] (Fig.1.7). These are listed below:

Operating System and Software Level: approaches such as partitioning and compression algorithms. At Operating System level, power consumption can be reduced by designing an "'energy-aware"' scheduler (EAS). In this scenario, the scheduler takes decision relying on energy models of the resources. As an example in Linux kernel 5.4.0 the EAS, based on energy models of the CPU, is able to select an energy efficient CPU for each task [Energy Aware Scheduling] (Fig. 1.6).

OS can also achieve energy efficiency by implementing *Dynamic Power Management* (DPM) of system resources allowing to reconfigure dynamically the system providing the requested services [*Low Power Principles*]. Another approach at system level can be code compression, which proposes basically to store programs in a compressed form and decompress them on-the-fly at execution time [Varadharajan and Nallasamy, 2017, Benini, Menichelli, and Olivieri, 2004]. An example of a simple code compression approach consists in the definition of a *dense* instruction set, characterized by a limited number of short instructions. This technique has been adopted by several commercial core processors such as ARM (Thumb ISA), MIPS and Xtensa.

| CPU util.<br>1024  |                | Energ                   | y Model                    |

|--------------------|----------------|-------------------------|----------------------------|

| 768                |                | Little                  | ++<br>  Big                |

|                    |                | Cap   Pwr               | Cap  Pwr                   |

| 512                | - ##<br>## ##  | 170   50<br>  341   150 | 512   400  <br>  768   800 |

| 341 -PP<br>PP      | ## ##<br>## ## | 512   300               | 1024   1700                |

| 170 -##<br>## ##   | ## ##<br>## ## |                         |                            |

| CPUØ CPU1          | CPU2 CPU3      |                         |                            |

| Current OPP: ===== | Other OPP: -   | util_av                 | g (100 each): ##           |

FIGURE 1.6: Power trends. Source: [Energy Aware Scheduling]

- *Architecture level*: techniques such as parallelism, pipelining, distributed processing and power management. In particular, parallelism and pipelining can optimize power consumption at the expense of area while maintaining the same throughput. By combining these two approaches it is possible to achieve a further reduction in power by aggressively reducing supply voltage.

- *Circuit/Logic level*: examples are voltage scaling, double edge triggering and transistor sizing. The latter in particular has a strong impact on circuit delay and power dissipation in combinational circuits. At logic level an example is represented by *adiabatic circuits* which use reversible logic to conserve energy. The implementation of these circuits is governed by two rules:

- 1. a transistor must never be turned on when there is a potential voltage between drain and source;

- 2. a transistor must never be turned off when current is flowing through it.

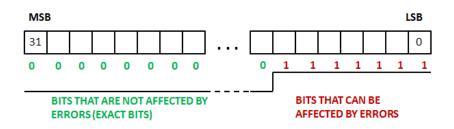

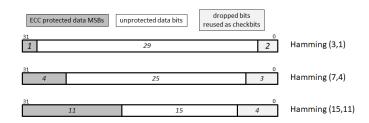

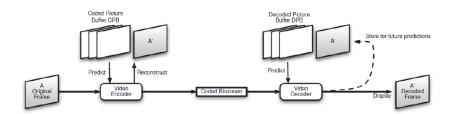

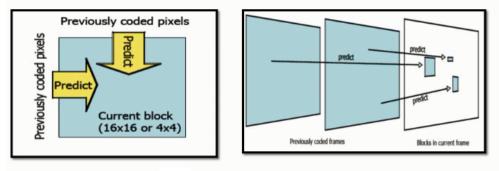

- *Technology Level*: techniques such as threshold reduction and multi-threshold (MT-CMOS) devices. The latter refers to the possibility of realizing transistors with different thresholds in a CMOS process, which allows to save energy up to 30% [Gupta and Padave, 2016]. Another technique is the usage of multiple supply voltages (Voltage Islands) that, by assigning different  $V_{dd}$  values to cells according to their timing criticality, allows to reduce both leakage and dynamic power. In particular, the basic idea is to group different supply voltages in a reduced number of voltage islands (each one with a single  $V_{dd}$ ) avoiding complex power supply system and a large amount of level shifters.