# Analysis and design of low-power data converters

Department of Information Engineering, Electronics and Telecommunications

Doctor of Philosophy in Information and Communication Technologies Cycle  $\mathsf{XXX}$

Candidate

Danilo Ruscio ID number 1089812

Thesis Advisor

Prof. Francesco Centurelli

A thesis submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in ICT  $\,$

Thesis defended on 22 February 2018.

This thesis was evaluated by the two following external referees:

Prof. Alfio Dario Grasso, University of Catania, Catania, Italy Prof. Vincenzo Stornelli, University of L'Aquila, L'Aquila, Italy

The time and effort of the external referees in evaluating this thesis, as well as their valuable and constructive suggestions are very much appreciated and greatly acknowledged.

### Analysis and design of low-power data converters

Ph.D. thesis. Sapienza - University of Rome

© 2018 Danilo Ruscio. All rights reserved

This thesis has been typeset by LATEX and the Sapthesis class.

Version: February 19, 2018

Author's email: danilo.ruscio@uniroma1.it

#### Abstract

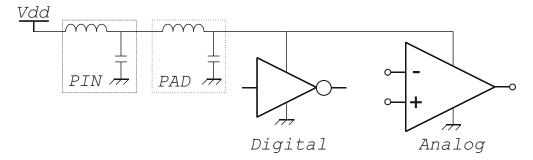

In a large number of applications the signal processing is done exploiting both analog and digital signal processing techniques. In the past digital and analog circuits were made on separate chip in order to limit the interference and other side effects, but the actual trend is to realize the whole elaboration chain on a single System on Chip (SoC). This choice is driven by different reasons such as the reduction of power consumption, less silicon area occupation on the chip and also reliability and repeatability. Commonly a large area in a SoC is occupied by digital circuits, then, usually a CMOS short-channel technological processes optimized to realize digital circuits is chosen to maximize the performance of the Digital Signal Processor (DSP). Opposite, the short-channel technology nodes do not represent the best choice for analog circuits. But in a large number of applications, the signals which are treated have analog nature (microphone, speaker, antenna, accelerometers, biopotential, etc.), then the input and output interfaces of the processing chip are analog/mixed-signal conversion circuits. Therefore in a single integrated circuit (IC) both digital and analog circuits can be found. This gives advantages in term of total size, cost and power consumption of the SoC. The specific characteristics of CMOS short-channel processes such as:

- Low breakdown voltage (BV) gives a power supply limit (about 1.2 V).

- High threshold voltage  $V_{TH}$  (compared with the available voltage supply) fixed in order to limit the leakage power consumption in digital applications (of the order of 0.35 / 0.4V), puts a limit on the voltage dynamic, and creates many problems with the stacked topologies.

- Threshold voltage dependent on the channel length  $V_{TH} = f(L)$  (short channel effects).

- Low value of the output resistance of the MOS  $(r_0)$  and gm limited by speed saturation, both causes contribute to achieving a low intrinsic gain  $g_m r_0 = 20$  to 26dB.

- Mismatch which brings offset effects on analog circuits.

make the design of high performance analog circuits very difficult. Realizing low-power circuits is fundamental in different contexts, and for different reasons: lowering the power dissipation gives the capability to reduce the batteries size in mobile devices (laptops, smartphones, cameras, measuring instruments, etc.), increase the life of remote sensing devices, satellites, space probes, also allows the reduction of the size and weight of the heat sink. The reduction of power dissipation allows the realization of implantable biomedical devices that do not damage biological tissue. For this reason, the analysis and design of low power and high precision analog

circuits is important in order to obtain high performance in technological processes that are not optimized for such applications. Different ways can be taken to reduce the effect of the problems related to the technology:

- Circuital level: a circuit-level intervention is possible to solve a specific problem

of the circuit (i.e. Techniques for bandwidth expansion, increase the gain,

power reduction, etc.).

- Digital calibration: it is the highest level to intervene, and generally going to correct the non-ideal structure through a digital processing, these aims are based on models of specific errors of the structure.

- Definition of new paradigms.

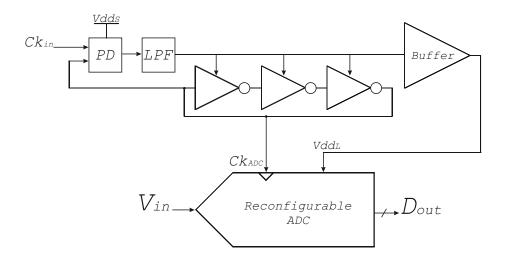

This work has focused the attention on a very useful mixed-signal circuit: the pipeline ADC. The pipeline ADCs are widely used for their energy efficiency in high-precision applications where a resolution of about 10-16 bits and sampling rates above hundreds of Mega-samples per second (telecommunication, radar, etc.) are needed. An introduction on the theory of pipeline ADC, its state of the art and the principal non-idealities that affect the energy efficiency and the accuracy of this kind of data converters are reported in Chapter 1. Special consideration is put on low-voltage low-power ADCs. In particular, for ADCs implemented in deep submicron technology nodes side effects called short channel effects exist opposed to older technology nodes where undesired effects are not present. An overview of the short channel effects and their consequences on design, and also power consuption reduction techniques, with particular emphasis on the specific techniques adopted in pipelined ADC are reported in Chapter 2. Moreover, another way may be undertaken to increase the accuracy and the efficiency of an ADC, this way is the digital calibration. In Chapter 3 an overview on digital calibration techniques, and furthermore a new calibration technique based on Volterra kernels are reported. In some specific applications, such as software defined radios or micropower sensor, some circuits should be reconfigurable to be suitable for different radio standard or process signals with different characteristics. One of this building blocks is the ADC that should be able to reconfigure the resolution and conversion frequency. A reconfigurable voltage-scalable ADC pipeline capable to adapt its voltage supply starting from the required conversion frequency was developed, and the results are reported in Chapter 4. In Chapter 5, a pipeline ADC based on a novel paradigm for the feedback loop and its theory is described.

# Contents

| 1 | Intr | oduct  | ion        |                                                      | 1  |

|---|------|--------|------------|------------------------------------------------------|----|

|   | 1.1  | Analo  | g to Digit | al Converters                                        | 1  |

|   |      | 1.1.1  | Flash A    | DC                                                   | 5  |

|   |      | 1.1.2  | Pipeline   | ADC                                                  | 6  |

|   |      | 1.1.3  | SAR AI     | OC                                                   | 7  |

|   |      | 1.1.4  | Sigma-I    | Delta ADC                                            | 8  |

|   | 1.2  | Perfor | mance Cl   | haracterization in ADC Converters                    | 9  |

|   |      | 1.2.1  | Static C   | Characteristics                                      | 10 |

|   |      |        | 1.2.1.1    | DNL                                                  | 11 |

|   |      |        | 1.2.1.2    | INL                                                  | 11 |

|   |      |        | 1.2.1.3    | Offset Error                                         | 11 |

|   |      |        | 1.2.1.4    | Gain Error                                           | 12 |

|   |      | 1.2.2  | Frequen    | cy Domain Measures                                   | 12 |

|   |      |        | 1.2.2.1    | Signal-to-Noise Ratio (SNR)                          | 13 |

|   |      |        | 1.2.2.2    | Spurious Free Dynamic Range (SFDR)                   | 13 |

|   |      |        | 1.2.2.3    | Harmonic Distorsion $HD_K$                           | 13 |

|   |      |        | 1.2.2.4    | Total Harmonic Distorsion                            | 14 |

|   |      |        | 1.2.2.5    | Signal-to-noise and Distorsion Ratio (SNDR)          | 14 |

|   |      |        | 1.2.2.6    | Effective Number Of Bits (ENOB)                      | 14 |

|   |      |        | 1.2.2.7    | Dynamic Range                                        | 14 |

|   |      |        | 1.2.2.8    | Effective Resolution Bandwidth                       | 15 |

|   |      |        | 1.2.2.9    | Inter-Modulation Distortion                          | 15 |

|   |      | 1.2.3  | Dynami     | c Performance                                        | 16 |

|   |      |        | 1.2.3.1    | Sampling Time Uncertainly                            | 16 |

|   |      |        | 1.2.3.2    | Thermal Noise                                        | 18 |

|   | 1.3  | Pipeli | ne ADC .   |                                                      | 18 |

|   |      | 1.3.1  | Compon     | nent Accuracy                                        | 19 |

|   |      | 1.3.2  | The Mu     | ltiplying DAC                                        | 19 |

|   |      |        | 1.3.2.1    | Effect of Finite Opamp Gain and Parasitic Capacitors | 21 |

|   |      |        | 1.3.2.2    | Effect of Mismatch                                   | 21 |

|   |      |        | 1.3.2.3    | Speed                                                | 22 |

vi Contents

|   |     | 1.3.3          | subADC                                                             |

|---|-----|----------------|--------------------------------------------------------------------|

|   |     | 1.3.4          | subDAC                                                             |

|   |     | 1.3.5          | Sample-and-Hold and Residue Amplifier                              |

|   |     | 1.3.6          | Digital Output Recostruction                                       |

|   |     | 1.3.7          | Digital Error Correction                                           |

|   | 1.4 | MDAC           | C Implementation                                                   |

|   |     | 1.4.1          | 1 bit MDAC                                                         |

|   |     | 1.4.2          | 1.5 bit MDAC                                                       |

|   |     | 1.4.3          | Multi bit MDAC                                                     |

|   | 1.5 | Issues         | in Pipeline ADC                                                    |

|   |     | 1.5.1          | Noise in MDACs                                                     |

|   |     |                | 1.5.1.1 kT/C                                                       |

|   |     |                | 1.5.1.2 Thermal Noise in Opamp                                     |

|   |     | 1.5.2          | Thermal Noise in SC-MDAC                                           |

|   |     |                | 1.5.2.1 Distortion Model for Pipeline ADCs                         |

|   | 1.6 | Figure         | s of Merit of ADCs                                                 |

|   | 1.7 | State          | of the Art of Pipeline ADCs                                        |

| _ | -   |                |                                                                    |

| 2 |     |                | sumption reduction in submicron CMOS process 41                    |

|   | 2.1 | •              | Submicron CMOS Process                                             |

|   |     | 2.1.1          | Static Characteristic of NMOS Devices                              |

|   |     | 2.1.2          | Small Signal Properties of NMOS Devices                            |

|   |     | 2.1.3          | Noise Properties                                                   |

|   |     | 2.1.4          | Short Channel Effect                                               |

|   |     | 0.1.5          | 2.1.4.1 Output Resistance                                          |

|   |     | 2.1.5          | Body Effect                                                        |

|   |     | 2.1.6          | Modification of the Threshold Voltage due to Short Channel  Effect |

|   |     | 0.1.7          |                                                                    |

|   |     | 2.1.7<br>2.1.8 | •                                                                  |

|   |     | 2.1.8          | Mobility Degradation and Velocity Saturation                       |

|   |     | _              | Leakage Currents       47         Noise       48                   |

|   | 2.2 |                | t on Analog Design                                                 |

|   | 2.2 | 2.2.1          | Intrinsic Device Gain                                              |

|   |     | 2.2.1 $2.2.2$  | Signal Headroom                                                    |

|   |     | 2.2.2          | Excess Thermal Noise                                               |

|   |     | ۷.∠.ئ          | 2.2.3.1 Leakage currents                                           |

|   |     | 2.2.4          | Mismatch and Process Spreads                                       |

|   | 2.3 |                | g Design in Mixed-Signal Systems                                   |

|   | ۷.۵ |                |                                                                    |

|   |     | 2.3.1          | Switch                                                             |

|   |     | 2.3.2          | Supply Noise                                                       |

Contents

|   | 2.4 | Power   | Consum    | ption Reduction Techniques                                 | 54  |

|---|-----|---------|-----------|------------------------------------------------------------|-----|

|   |     | 2.4.1   | Frequen   | cy Scaling                                                 | 56  |

|   |     | 2.4.2   | Voltage   | Scaling                                                    | 56  |

|   |     | 2.4.3   | Open Lo   | oop Amplifier Approach                                     | 56  |

|   |     | 2.4.4   | Specific  | Power Reduction Techniques for Pipelined ADC               | 57  |

|   |     |         | 2.4.4.1   | Front-End Sample-and-Hold Removal                          | 58  |

|   |     |         | 2.4.4.2   | Capacitors and Opamp Sharing                               | 58  |

|   |     |         | 2.4.4.3   | ${\bf Comparator~Based~Switched~Capacitor~Circuits} . \ .$ | 59  |

| 3 | Cal | ibratio | n         |                                                            | 61  |

|   | 3.1 | Calibr  | ation Ove | erview                                                     | 62  |

|   |     | 3.1.1   | Procedu   | re for ADC Error Calibration                               | 63  |

|   |     | 3.1.2   | Foregrou  | and Calibration                                            | 63  |

|   |     | 3.1.3   | Backgro   | und Calibration                                            | 64  |

|   |     |         | 3.1.3.1   | Virtual Background Calibration Technique                   | 64  |

|   |     |         | 3.1.3.2   | Skip and Fill                                              | 65  |

|   |     |         | 3.1.3.3   | Queue                                                      | 66  |

|   |     |         | 3.1.3.4   | True Background Calibration Technique                      | 66  |

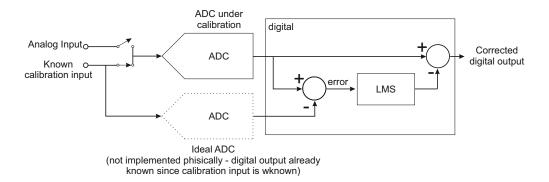

|   |     | 3.1.4   | Adaptiv   | e Calibration Technique                                    | 66  |

|   |     |         | 3.1.4.1   | Channel Error Identification                               | 66  |

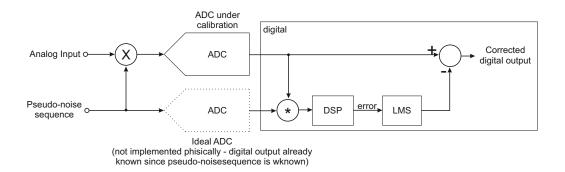

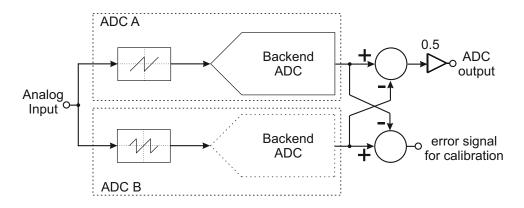

|   |     |         | 3.1.4.2   | Correlation-Based Techniques                               | 67  |

|   |     |         | 3.1.4.3   | Rapid Calibration of ADC Errors                            | 67  |

|   | 3.2 | Calibr  | ation bas | ed on Volterra Kernel                                      | 69  |

|   |     | 3.2.1   | Volterra  | Series                                                     | 69  |

|   |     | 3.2.2   | Volterra  | Calibration Survey                                         | 70  |

|   |     | 3.2.3   | Pruned    | Volterra Calibration                                       | 71  |

|   |     |         | 3.2.3.1   | Pruned Volterra Sample-and-Hold                            | 71  |

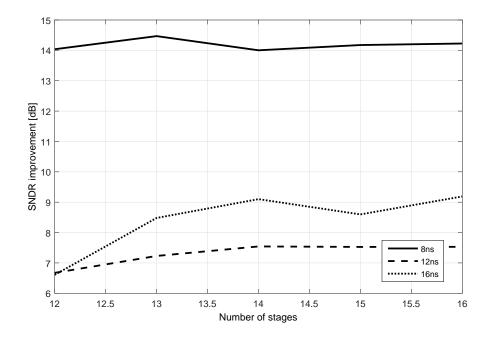

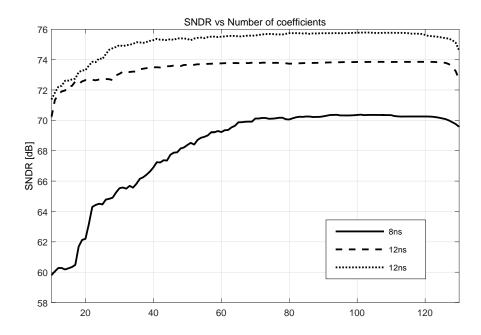

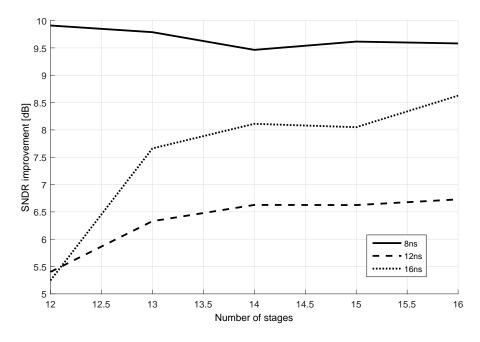

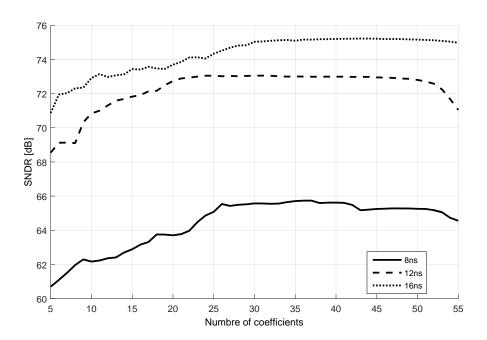

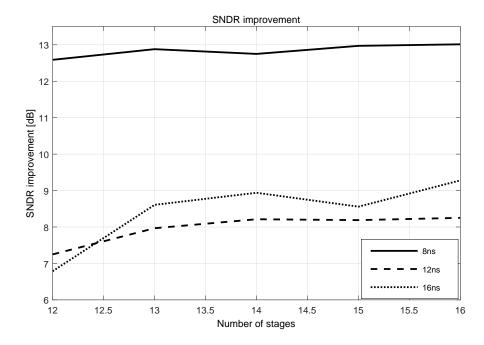

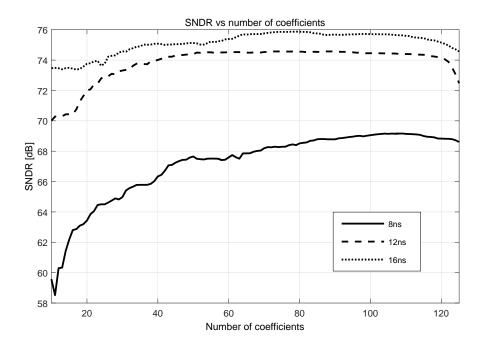

|   |     |         | 3.2.3.2   | Simulation Results                                         | 73  |

|   |     |         | 3.2.3.3   | Pruned Volterra ADC                                        | 76  |

| 4 | Rec | onfigu  | rability  |                                                            | 83  |

|   |     | 4.0.1   | Reconfig  | gurable ADC Survey                                         | 86  |

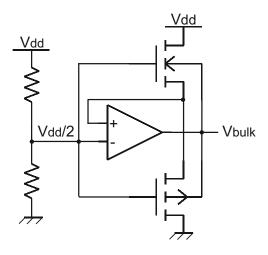

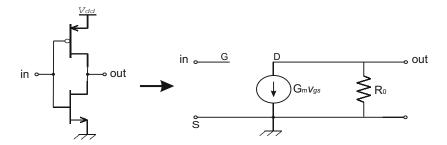

|   |     | 4.0.2   | Voltage   | Scalable OPA                                               | 87  |

|   |     |         | 4.0.2.1   | Test Voltage Scalable OPA                                  | 92  |

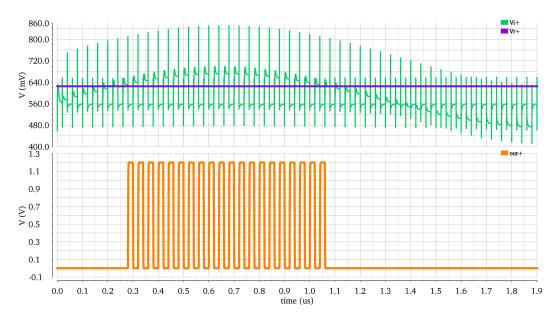

|   |     | 4.0.3   | Voltage   | Scalable Sample-and-Hold                                   | 99  |

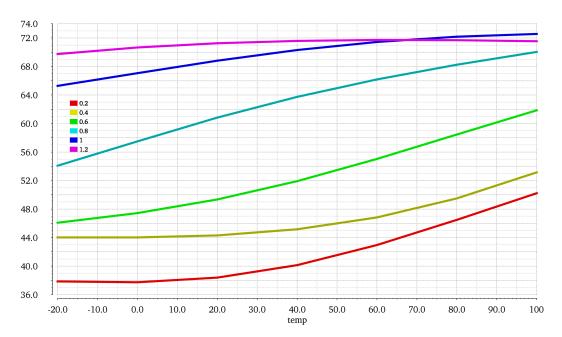

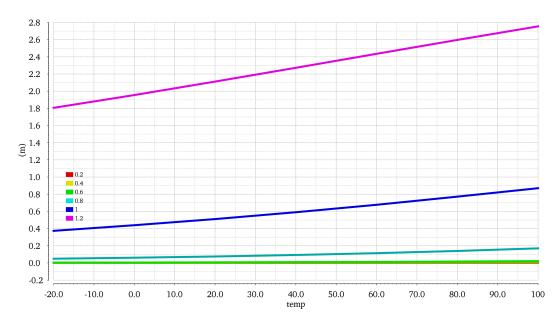

|   |     |         | 4.0.3.1   | Test Voltage Scalable Sample-and-Hold                      | 101 |

|   |     | 4.0.4   | Voltage   | Scalable Multiplying-DAC                                   | 102 |

|   |     |         | 4.0.4.1   | Test Voltage Scalable Multiplying-DAC                      | 104 |

|   |     | 4.0.5   | Voltage   | Scalable Pipeline ADC                                      | 107 |

|   |     |         | 4.0.5.1   | Test Voltage Scalable Pipeline ADC                         | 109 |

viii Contents

| 5 | MD  | AC wi  | th low sensitivity to OPA's finite gain error                 | 111 |

|---|-----|--------|---------------------------------------------------------------|-----|

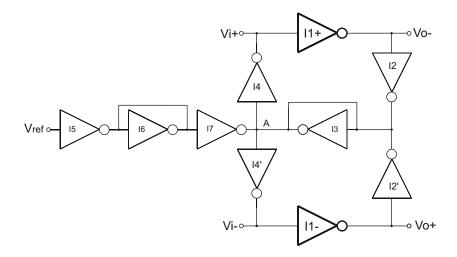

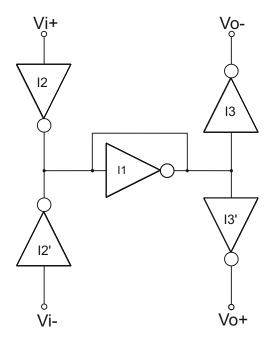

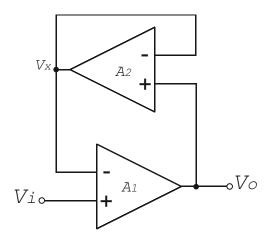

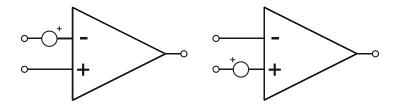

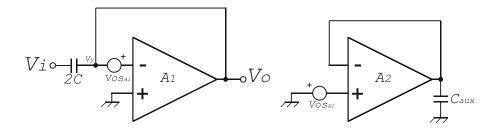

|   | 5.1 | Active | Feedback Structure Introduction                               | 112 |

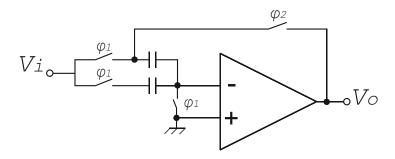

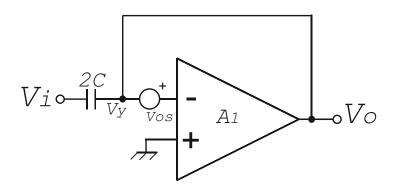

|   |     | 5.1.1  | Classical Feedback x2 Gain Sample-and-Hold Analysis           | 113 |

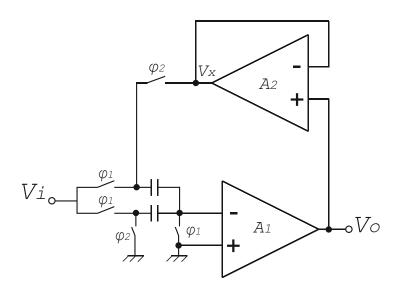

|   |     | 5.1.2  | Active Feedback x2 Gain Sample-and-Hold Analysis              | 114 |

|   |     | 5.1.3  | Classical Feedback MDAC Analysis                              | 115 |

|   |     | 5.1.4  | Active Feedback MDAC Analysis                                 | 116 |

|   |     | 5.1.5  | Figure of Merit for Active Feedback Structure                 | 118 |

|   |     | 5.1.6  | Mismatch on Gain of Opamps                                    | 118 |

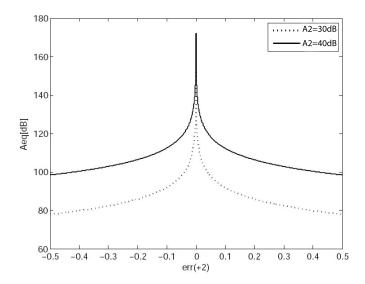

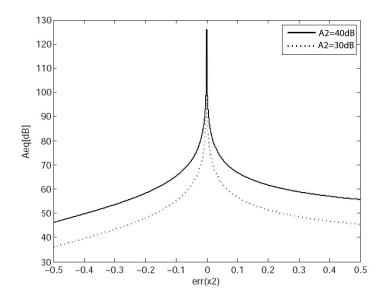

|   |     |        | 5.1.6.1 "+2 Error"                                            | 118 |

|   |     |        | 5.1.6.2 "x2 Error"                                            | 119 |

|   |     |        | 5.1.6.3 Error Model                                           | 120 |

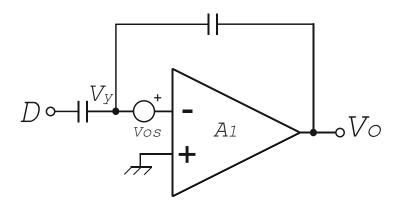

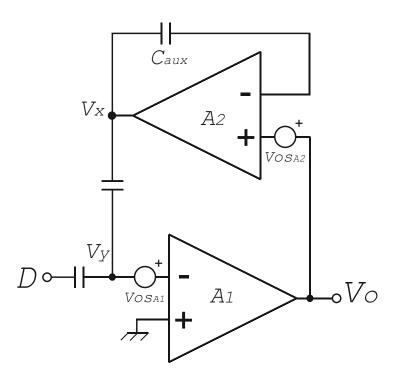

|   |     | 5.1.7  | Analysis of the Offset in the MDAC                            | 121 |

|   |     |        | 5.1.7.1 Offset in Classical MDAC Topology                     | 121 |

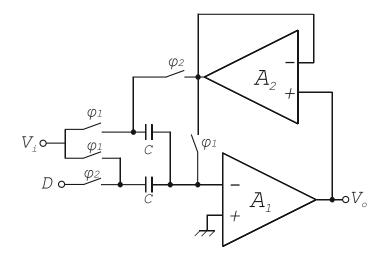

|   |     |        | 5.1.7.2 Correlated Double Sampling on Classical MDAC          |     |

|   |     |        | Topology                                                      | 122 |

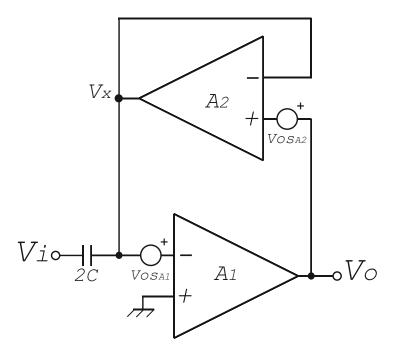

|   |     | 5.1.8  | Offset in Active-Feedback MDAC Topology                       | 124 |

|   |     |        | 5.1.8.1 CDS Applied on the Main Amplifier of the Active       |     |

|   |     |        | Loop                                                          | 125 |

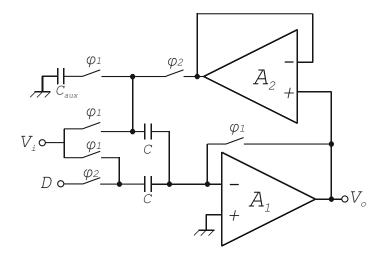

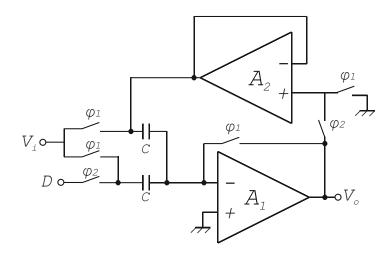

|   |     |        | 5.1.8.2 CDS Applied on Active Loop                            | 126 |

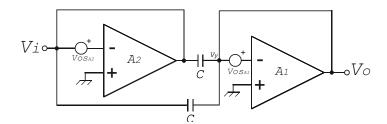

|   |     | 5.1.9  | Offset Cancellation by Auxiliary Capacitor in Active-Feedback |     |

|   |     |        | Topology                                                      | 128 |

|   |     | 5.1.10 | Offset Pre-Sampling in Active-Feedback Topology               | 130 |

|   | 5.2 | Freque | ency Analysis of the Active-Feedback Loop                     | 132 |

|   |     | 5.2.1  | Single Pole Approximation                                     | 132 |

|   |     | 5.2.2  | Two-Poles Approximation                                       | 134 |

|   | 5.3 | Active | Feedback Loop in Deep Submicron Technologies                  | 136 |

|   |     | 5.3.1  | Criteria for the topological choice of the opamps             | 136 |

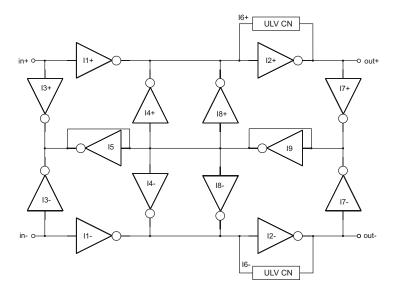

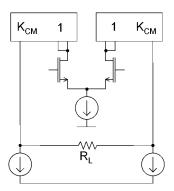

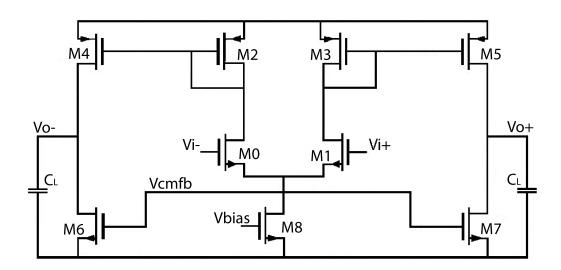

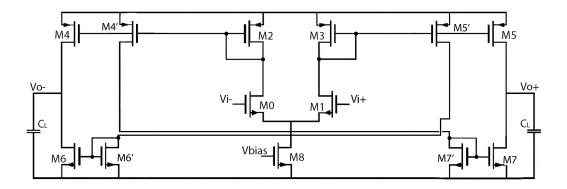

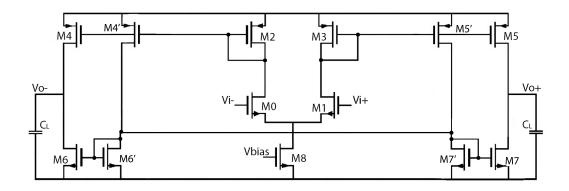

|   |     |        | 5.3.1.1 Current Mirror Based OPA                              | 137 |

|   |     | 5.3.2  | Possible Ways to Obtain the Gain Relationship                 | 138 |

|   |     |        | 5.3.2.1 x2 Based on Current Mirror Ratio                      | 139 |

|   |     |        | 5.3.2.2 x2 Based on Load Resistance Ratio                     | 139 |

|   |     |        | 5.3.2.3 x2 Based on Transconductance Ratio                    | 140 |

|   |     |        | 5.3.2.4 x2 Based on Topology                                  | 140 |

|   |     | 5.3.3  | Obtain the $+2$ in the Gain Ratio                             | 141 |

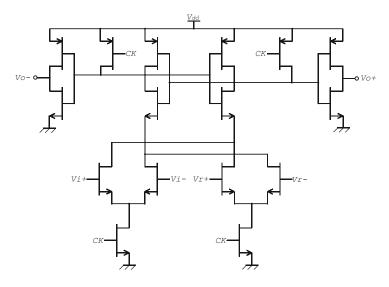

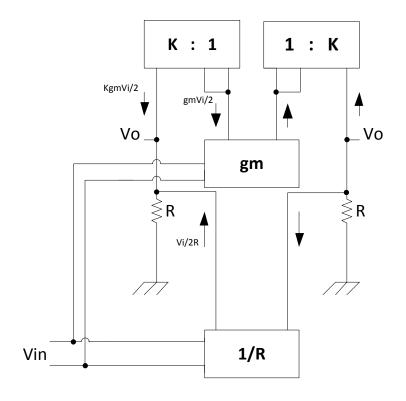

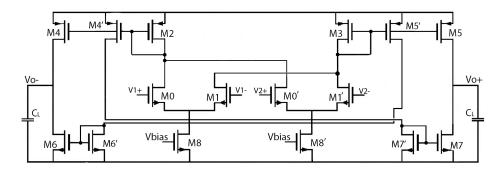

|   | 5.4 | Design | of an Active-Feedback Based ADC Pipeline                      | 143 |

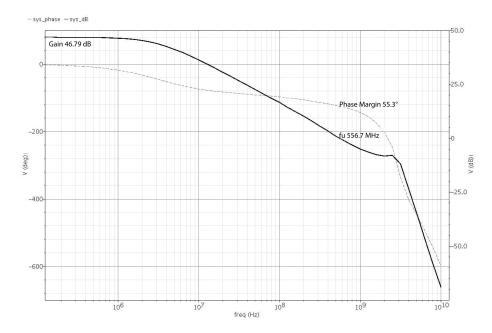

|   |     | 5.4.1  | Opamps Characterization                                       | 144 |

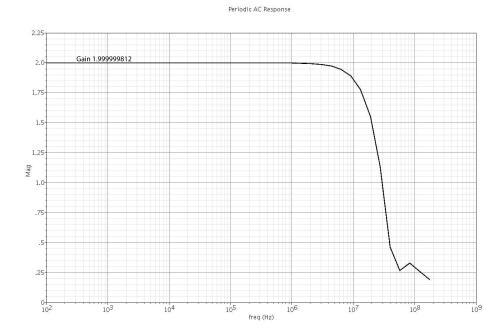

|   |     | 5.4.2  | Active Feedback Characterization                              | 145 |

|   |     | 5.4.3  | Active Feedback Pipeline ADC Characterization                 | 147 |

# List of Tables

| 1.1 | Resolution and sampling rate of different ADC structures                 | 2   |

|-----|--------------------------------------------------------------------------|-----|

| 1.2 | Literature survey on ADC in the years 2014 and 2017                      | 3   |

| 1.3 | Literature survey on ADC pipeline                                        | 39  |

| 3.1 | Linearity improvement and complexity for various models                  | 82  |

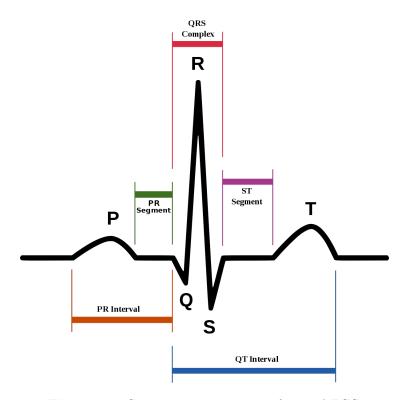

| 4.1 | Bandwidths and amplitudes of various bio-potentials                      | 84  |

| 4.2 | Reconfigurable ADC Survey                                                | 87  |

| 4.3 | OPA open loop characterization                                           | 94  |

| 4.4 | OPA open loop characterization corner                                    | 96  |

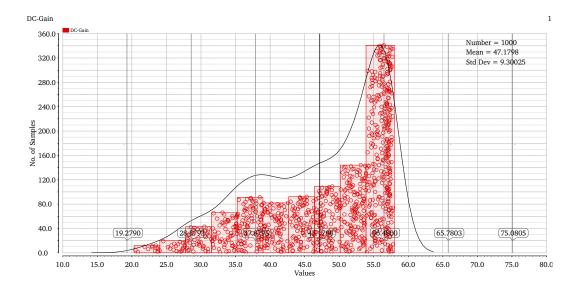

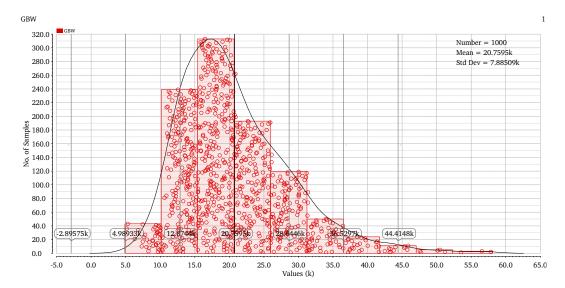

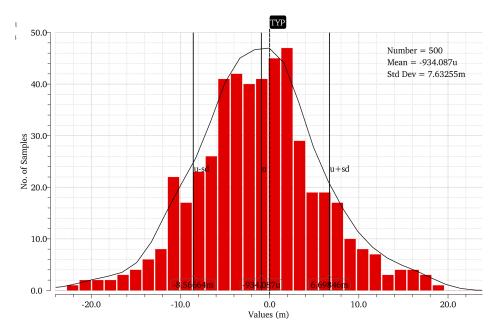

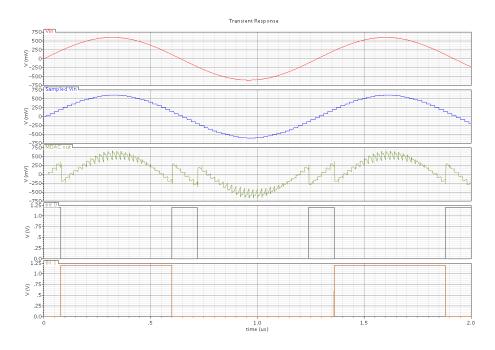

| 4.5 | Monte Carlo analysis summary                                             | 100 |

| 4.6 | THD for different values of Vdd and sampling period                      | 103 |

| 4.7 | MDAC and Sample-and-Hold characterization for different voltage supplies | 108 |

| 4.8 | Pipeline and Sample-and-Hold characterization for different voltage      | 100 |

| 1.0 | supply                                                                   | 109 |

| 5.1 | Requirements for the opamps                                              | 144 |

| 5.2 | Main amplifier characterization                                          | 144 |

| 5.3 | Feedback amplifier characterization                                      | 145 |

| 5.4 | Main opamp characterization with temperature variation                   | 145 |

| 5.5 | Feedback opamp characterization with temperature variation               | 145 |

| 5.6 | Main opamp characterization with process variation                       | 146 |

| 5 7 | Foodback opens characterization with process variation                   | 146 |

# Chapter 1

# Introduction

# 1.1 Analog to Digital Converters

Technology scaling has enabled the capability to integrate the whole signal processing chain in the same chip. This allows the digital treatment of the signal that provides accurate processing and low power consumption, but the physical quantities from which the signals are derived have analogue nature, thus analog to digital converters (ADC) are required to interface the analog to the digital world. In a mixed-signal system the ADC could be the main cause of waste of energy. For this reason a reduction of the power consumption of an ADC is welcome, because it allows the possibility to implement mixed-signal systems in low-power environment. Over the years several ADC architectures have been developed to optimize specific features, such as resolution, conversion speed and power consumption. Each type of converter structure achieves optimal power consumption for a specific conversion frequency or resolution interval.

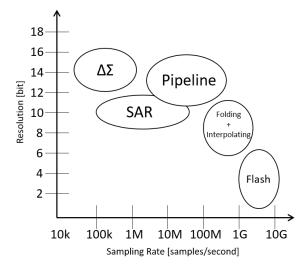

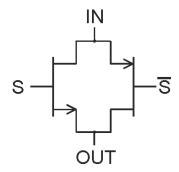

Figure 1.1. resolution sampling rate ADC structures

Figure 1.1 shows the sampling frequency and resolution ranges where we can find each kind of ADC structure. We can clearly discern that Flash ADCs reach the fastest conversion frequencies, but with a limited resolution. Conversely, the best resolution performance can be obtained only by  $\Sigma\Delta$  ADCs but the conversion frequencies attained are very limited. There are different middle ground, such as Successive Approximation Register (SAR), Time-Interleaved and pipeline ADCs. Each Structure has been proposed to optimise a specific point, such as power consumption, resolution, conversion frequencies and area. In table 1.1 are reported the main characteristics for the different ADC structures.

| Architecture          | Latency | Speed       | Accuracy    | Area   |

|-----------------------|---------|-------------|-------------|--------|

| Flash                 | Low     | High        | Low         | High   |

| SAR                   | Low     | Low-medium  | Medium-High | Low    |

| Folding+interpolating | Low     | Medium-High | Medium      | High   |

| Sigma Delta           | High    | Low         | High        | Medium |

| Pipeline              | High    | Medium-High | Medium-High | Medium |

Table 1.1. Resolution and sampling rate of different ADC structures

In Table 1.2 is reported a literature survey on different ADC structure published during the period that this work is being carried out. As shown in table the best speed performance are achieved not only by Flash ADCs, but also by time-interleaved system that uses several SAR or pipeline ADCs as subconverter. Furthermore also high speed  $\Sigma\Delta$  ADCs have been in the spotlight during the considered period.

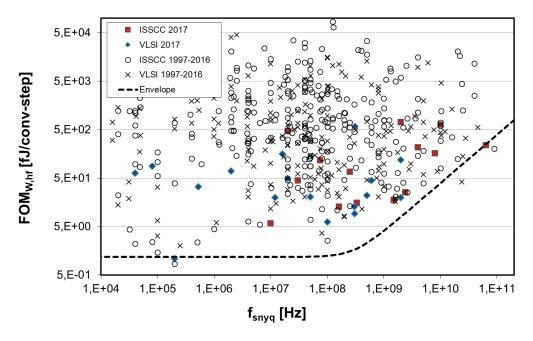

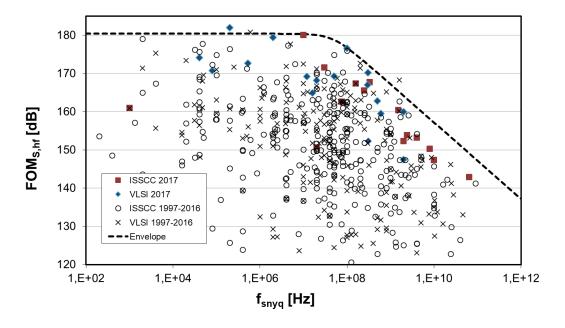

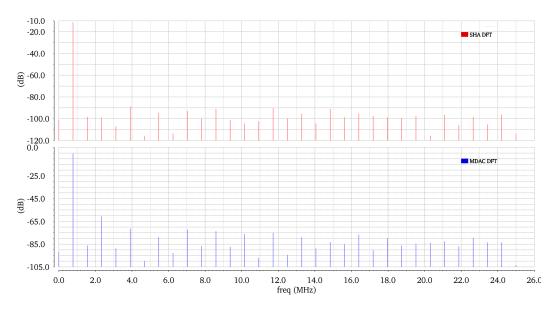

The results published by ISSCC (International Solid-State Circuits Conference) and IEEE transactions on VLSI in the last two decades are reported in figure 1.2 and 1.3. The figure spots the energy efficiency (defined in section 1.6) and the conversion frequency reached by the reported works. The figures bring out the energy efficiency against the absolute speed. Since both the Walden and the Shreier FOM (the Walden and the Shreier Figure of merit are defined in 1.6) work well only across a limited range of SNDR, separate plot for  $FOM_S$  and  $FOM_W$  has been produced. For low-resolution designs, the  $FOM_W$  plot is more suitable, whereas the  $FOM_S$  plot does a better job at rewarding high resolution designs that also push bandwidth. The envelope lines included in the FOM vs. Speed plots are constructed as follows:

- 1. Identify the 5 data points with the best FOM (regardless of speed) and average them. This defines the "DC" value of the envelope.

- 2. Identify the 5 best data points with the best "combination2 of FOM and speed. For  $FOM_W$ , this means  $FOM_W/f_{snug}$ . For  $FOM_S$ , this means  $FOM_S + 1$

| Year | TYPE                 | Technology | Author           | P[mW]     | fs[MHz] | $FOM_W \left[ \frac{fJ}{conv} \right]$ |

|------|----------------------|------------|------------------|-----------|---------|----------------------------------------|

| 2014 | Pipe, SAR            | 0,18       | A. Bannon        | 30,5      | 5       | -                                      |

| 2014 | SAR                  | 0,09       | Y. Chen          | 0,0002    | 0.255   | -                                      |

| 2014 | Pipe                 | 0,18       | H. Venkatram     | 6         | 30      | 47,7                                   |

| 2014 | Subranging           | 0,065      | K. Yoshioka      | 6         | 820     | 89,8                                   |

| 2014 | $\Sigma\Delta$ VCO   | 0,065      | B. Young         | 38        | 1280    | -                                      |

| 2014 | $\Sigma\Delta$       | 0,02       | S. Ho            | 23        | 2810    | -                                      |

| 2014 | $\Sigma\Delta$       | 0,18       | A. Bandyopadhyay | 21        | 57.5    | -                                      |

| 2014 | $\Sigma\Delta$       | 0,09       | C. Weng          | 4,3       | 300     | -                                      |

| 2014 | Pipe                 | 0,18       | H. Venkatram     | 6         | 30.0    | 47,7                                   |

| 2014 | Pipe, SAR, TI        | 0,028      | B. Verbruggen    | 2,3       | 200     | 4,4                                    |

| 2014 | Pipe, SAR            | 0,065      | C. Lin           | 5,3       | 210     | 20,7                                   |

| 2014 | Pipe, SAR            | 0,04       | Y. Zhou          | 4,96      | 160     | 17,5                                   |

| 2015 | SAR                  | 0,18       | S. Jeong         | 0,00012   | 10      | -                                      |

| 2015 | SAR                  | 0,014      | C. C. Lee        | 4,3       | 70      | 26,7                                   |

| 2015 | SAR                  | 0,065      | Z. Chen          | $0,\!121$ | 50      | -                                      |

| 2015 | SAR, VCO             | 0,045      | J. P. Mathew     | 3,4       | 200     | 8,1                                    |

| 2015 | SAR, TI              | 0,028      | Y. Duan          | 381       | 46000   | 452,9                                  |

| 2016 | SAR                  | 0,028      | K. Obata         | 0,0371    | 0,1     | -                                      |

| 2016 | SAR, VCO             | 0,04       | A. Sanyal        | $0,\!35$  | 36      | -                                      |

| 2016 | SAR, TI              | 0,016      | Yohan Frans      | 280       | 2800    | 150,9                                  |

| 2016 | SAR, TI              | 0,065      | Jae Won Nam      | 37,7      | 1600    | 7,2                                    |

| 2016 | Pipe, SAR, TI        | 0,028      | Yuan-Ching Lien  | 0,0146    | 800     | 17,3                                   |

| 2016 | Flash                | 0,028      | Bharath Raghavan | 0,095     | 10000   | 330,7                                  |

| 2016 | SAR, TI              | 0,028      | Benwei Xu        | 0,023     | 24000   | 20,9                                   |

| 2016 | SAR. TI              | 0,016      | Ying-Zu Lin      | 8,2       | 1600    | 11,2                                   |

| 2016 | Pipe, TI             | 0,028      | Ahmed M.A. Ali   | 2300      | 5000    | 398,5                                  |

| 2017 | $\Sigma\Delta$       | 0,028      | I.H. Janget      | 4,2       | 320     | -                                      |

| 2017 | $\Sigma\Delta$ , VCO | 0,04       | S. Li            | $0,\!524$ | 330     | -                                      |

| 2017 | $\Sigma\Delta$       | 0,04       | M. B. Dayanik    | 233       | 5000    | 237,2                                  |

| 2017 | Pipe, SAR, TI        | 0,016      | E. Martens       | 3,6       | 303     | 5,0                                    |

| 2017 | Pipe                 | 0,028      | K.J. Moon        | 6         | 500     | 21,5                                   |

| 2017 | Pipe                 | 0,028      | J. Lagos         | 14,2      | 600     | 36,0                                   |

| 2017 | Pipe, SAR            | 0,04       | Y. Lim           | 2,3       | 100     | -                                      |

| 2017 | SAR, Pipe            | 0,18       | D. Hummerston    | 11,4      | 2       | -                                      |

| 2017 | Flash                | 0,065      | S. Zhu           | 21        | 2000    | 240,5                                  |

**Table 1.2.** Literature survey on ADC in the years 2014 and 2017

$10log(f_{snyq})$ . The average of these defines the locations of the 10dB/decade rise/drop lines in the FOM plots.

Figure 1.2. Figure Of Merit vs Speed in ADC

Figure 1.3. Shreier FOM vs frequency

Between the different structures one of the most interesting is the pipeline ADC because it can reach conversion frequencies and resolutions that make this structure

suitable for telecom, radar and biomedical applications. This Chapter continues with an overview of the principal architectures of ADC converter and for each type is kept the focus on the pros and cons respect to the pipeline converter.

#### 1.1.1 Flash ADC

Many different ADC architectures have been developed over the years, each with different tradeoffs respects to power consumption, speed, and resolution. Most of this structures are derived from the Flash ADC, or make use of Flash ADC in their implementation.

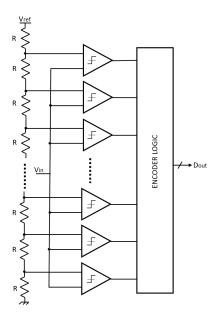

Figure 1.4. Flash ADC structure

Figure 1.4 shows the principle scheme of a Flash converter. Flash ADC converts an analog signal into a digital one by comparing the signal with fixed reference values, determining in which interval of the  $2^N$  is the input signal. Mapping the thermometer code to its binary equivalent forms a N binary representation of the input signal [1]. A flash ADC has a large bank of comparators, each consisting of wideband, low-gain preamps followed by a latch. The preamps must provide gains that do not need to be linear or accurate; only the comparator's trip points must be accurate. As a result the speed of a flash ADC can not be reached by any other ADC structure. Another key advantage in Flash ADC architecture is the latency of only one clock cycle, an furthermore does not matter for the linearity of the comparators involved in the structure. The main drawback of Flash converter is due to the number of the comparators required, in fact, the number of comparators doubles for every resolution bit added; at the same time, each comparator must be twice accurate, thus large devices are required to suppress process variation effects,

thus high resolution Flash ADCs require too high silicon area, and also the power consumption makes the flash ADC unsuitable for some applications where the energy efficiency plays a fundamental role for the feasibility.

## 1.1.2 Pipeline ADC

Some of the limitations of the flash ADC are overcome by the pipeline ADC.

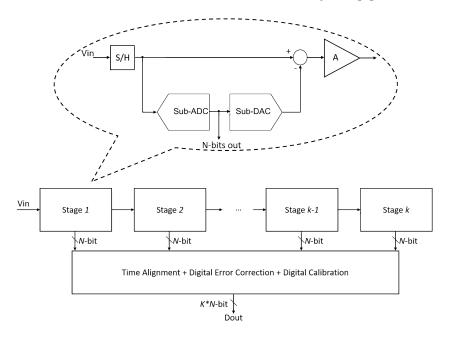

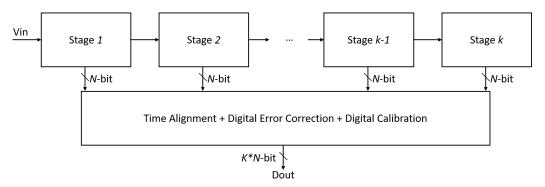

Figure 1.5. Pipeline ADC structure

A pipeline ADC is composed by a chain of  $N_s$  stages, and the conversion of a sample is splitted in  $N_s$  steps. Each stage of the pipeline takes as input an analog signal and provides as output a digital signal that represents a partial conversion of the signal, and also provides an analog output that will be refined by the successive stage. These stages are composed by a sub-ADC, a sub-DAC and an error amplifier. In figure 1.5 a principle schematic is shown. In each stage the analog input,  $V_{in}$ , is first sampled and held steady by a sample-and-hold structure, while the flash sub-ADC in the first stage quantizes it in N bits (N bit is the number of conversion bit of each stage). The output of the sub-ADC is taken as input by the sub-DAC, and the analog output is subtracted from the input. This "residue" is the quantization error of the sub-ADC and then this signal is multiplied by a factor  $2^N$  and fed to the next stage. This gained-up residue continues through the pipeline, providing N bits per stage until it reaches the last sub-ADC, which resolves the last N bits. Because the bits from each stage are determined at different points in time, all the bits corresponding to the same sample are time-aligned with shift registers before being fed to the digital-error-correction logic. Note that when a stage finishes processing

a sample, determining the bits, and passing the residue to the next stage, it can then start processing the next sample received from the sample-and-hold embedded within each stage. This pipelining action is the reason for the high throughput, but conversely to the flash, the pipeline ADC is affected by data latency, because each sample must propagate through the entire pipeline before all its associated bits are available for combining in the digital-error-correction logic. Moreover, the accuracy and the linearity required on the comparator of the pipeline ADC place some constraints that figure out pipelined ADC cannot match the speed of a well-designed flash ADC.

#### 1.1.3 SAR ADC

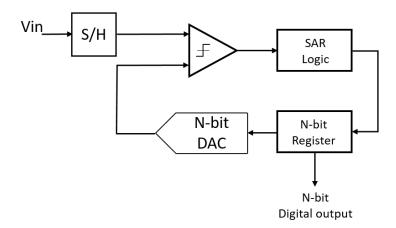

An arising interest in the last years is posed on successive approximation register (SAR) ADCs, that reduce dramatically the power consumption respect to the flash ADC. In a SAR-ADC, the bits are decided by a single high-speed, high-accuracy comparator bit by bit, from the most significative bit (MSB) down to the least significative bit (LSB).

Figure 1.6. SAR ADC block diagram

Figure 1.6 show a SAR ADC structure. A Sample-and-Hold holds the analog input while the sequential binary search is carried out. The SAR ADC compares the analog input with a digital to analog converter (DAC), whose output is updated by previously decided bits and successively approximates the analog input. At the beginning of the conversion phase, the register is initialized to midscale, which forces the decision threshold of the comparator to be  $V_{ref}/2$ . Based on the result of the comparator the MSB remains '1' if the analog value is above  $V_{ref}/2$ , or is changed to '0' if the input is below  $V_{ref}/2$ . By successively repeating the next bit is initialized to '1', and the decision threshold will be  $V_{ref}/4$  or  $3V_{ref}/4$ . The iterative algorithm is repeated N times, where N is the resolution of the SAR ADC. The successive approximation algorithm makes the SAR ADC more energy efficient respect to the

Flash ADC which use a brute force approach to perform the conversion. The other significant advantage of the SAR ADC is that it uses only one comparator, and a few other analog components for a N-bit conversion. The serial nature of SAR limits its operating speed, and still slower for very high resolutions (14 to 16 bits). This issue is solved in pipelined ADC that employs a parallel structure in which each stage works on 1 to a few bits (of successive samples) concurrently. Although there is only one comparator in a SAR, this comparator must be fast, clocked at approximately the product of number of bits for the sample rate  $f_{CK} = Nf_S$ , and as accurate as the ADC itself. This is another issue overcomed in pipeline structure where none of the comparators inside a pipelined ADC needs this degree of speed or accuracy. Thus, although the SAR ADC allows for a significant reduction of the analog components it comes at the cost of restricting the maximum sampling rate to only a fraction of the maximum available in a given technology. It should be noted that while the SAR determines 1-bit of the final digital output every clock cycle, the DAC is required to settle to the full accuracy of the ADC every clock cycle. Also, the comparator is required to be able to resolve inputs as small as the LSB of the ADC. As a result, much effort is required to optimize the DAC and the comparator blocks for high speed and high accuracy.

#### 1.1.4 Sigma-Delta ADC

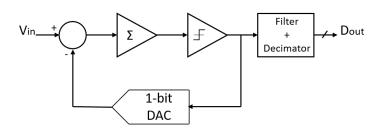

The Sigma Delta ( $\Sigma\Delta$ ) converter is a completely different kind of converter. First of all, it is an over-sampling converter: the signal occupies only a fraction of the Nyquist band. Second, it uses a special feedback loop to concentrate the power of the nonlinear terms in bands outside that of the input signal. Finally, it uses digital filters and decimators to filter the non-linear terms and reduce the conversion speed to the Nyquist limit. Figure 1.7 shows the basic architecture of a  $\Delta\Sigma$  ADC. This architecture is called "first-order single-bit" converter, because it uses only one feedback loop, and this loop uses a single-bit DAC.

Figure 1.7.  $\Sigma\Delta$  ADC block diagram

The integrator is put into a feedback loop and, due to its high gain at low frequencies, it reduces the error at these frequencies (being the error the difference between the input analog voltage and the output digital voltage, converted by the DAC), and pushes all the errors at high frequencies. Despite the fact that the output voltage is a digital single-bit stream, and it doesn't seem to resemble the input continuous-time signal in the time domain, in the frequency domain the difference between input and output is concentrated at high frequencies. But if the signal is at low frequencies, most of the distortion can be filtered, thus obtaining a high resolution converter. Traditionally, oversampling/sigma-delta-type converters commonly used in digital audio have a limited bandwidth of about 22kHz. Recently some high-bandwidth sigma-delta converters reached a bandwidth in the order of GHz with more than 16 bits of resolution. Sigma-delta converters trade speed for resolution. The need to sample many times (for example, at least 16 times, but often much higher) to produce one final sample causes the internal analog components in the sigma-delta modulator to operate much faster than the final data rate. The digital decimation filter is also nontrivial to design, and consumes a lot of silicon area.

# 1.2 Performance Characterization in ADC Converters

The goodness of an analog to digital converter may be characterised through different parameters, that can be grouped around three main lines which is static, dynamic and frequency domain performances. The static performance defines the goodness of the dc transfer function of the converter, that can be expressed through two significant figure of merit as Differential Non Linearity (DNL) or Integral Non Linearity (INL). Dynamic performanes are related to the behaviour of the converter when a time variable input signal is applied as stimulus. Finally, frequency domain performance defines the linearity of the converter or the effect of the noise in the frequency domine, the main figure of merit in this domain are the Total Harmonic Distortion (THD), the Signal to Noise Ratio (SNR) and their derived the Signal to Noise and Distortion Ratio (SNDR) and the Effective Number of Bits (ENOB). The different characteristics can be more or less interesting, based on the applications: for measure instruments are more important the static performances as the INL and DNL; in telecom field the frequency domain characteristics are more interesting because distortion has more impact on the signal than the static error quantifiable with INL and DNL. The Fast Fourier Transform (FFT) on the output signal of an ADC (reconverted in analog domain by an ideal DAC) shows the distortion above a noise floor, thus the ratio  $\frac{P_{signal}}{P_{distortion}}$  gives a measure of the linearity of the response of an ADC, the principal parameter that gives a measure of the distortion is the Total-Harmonic-Distortion (THD), that represents the ratio between the power of the singular and the sum of all the spectral components distortion. Ideally an ADC does not introduce any distortion, thus the recostructed signal is affected only by quantization error. Also the noise as the distortion is a fundamental parameter,

because defines the lower limit of the dynamic of the signal. The main parameter related to the noise is the Signal-to-Noise Ratio (SNR). By aggregating the effect of the noise and the distortion expressed by SNR and THD we obtain the Signal-to-Noise-and-Distortion-Ratio (SNDR), from the latter one is possible evaluate the Effective-Number-of-Bits (ENOB) which is the number of information bits above the floor due to noise and distortion.

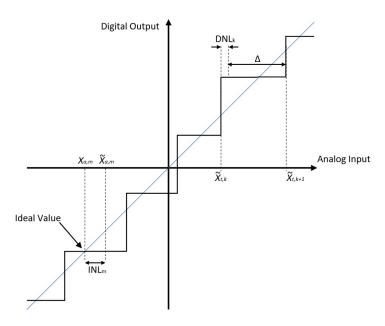

Figure 1.8. Transfer function of a non ideal ADC

To distinguish between the actual and ideal values in the data converters, all actual values are indicated with a  $\tilde{}$ . This means that  $X_{a,k}$  corresponds to the ideal analog value for digital code  $X_{d,k}$  while  $\tilde{X}_{a,k}$  corresponds to the actual value.

#### 1.2.1 Static Characteristics

Static errors, that is those errors that affect the accuracy of the converter when it is converting static (dc) signals, can be completely described by just four terms. These are offset error, gain error, integral nonlinearity and differential nonlinearity. Each can be expressed in LSB units or sometimes as a percentage of the Full-Scale Range (FSR). The linearity of the ADC and its Sample-and-Hold may be limited for a several number of causes, such as nonlinear switch on resistance, clock feedthrough errors, finite amplifier gain, parasitic capacitors or any other error sources present in the circuit.

#### 1.2.1.1 DNL

In an ideal ADC the input dynamic is divided in uniform steps  $\Delta$ . In actual implementation the deviation of the step from the ideal value is called differential nonlinearity (DNL) error. The DNL is defined as the difference of two adjacent levels minus the ideal step size.

$$DNL_k = \widetilde{X}_{t,k+1} - \widetilde{X}_{t,k} - \Delta \tag{1.1}$$

Usually the DNL is normalized respect the ideal value of the step size  $\Delta$ .

$$DNL_k = \frac{\widetilde{X}_{t,k+1} - \widetilde{X}_{t,k} - \Delta}{\Lambda}$$

(1.2)

If the DNL exceeds 1 LSB, there is a possibility that the converter can become nonmonotonic. This means that the magnitude of the output gets smaller for an increase in the magnitude of the input. In an ADC there is also a possibility that there can be missing codes i.e., one or more of the possible  $2^n$  binary codes are never output.

#### 1.2.1.2 INL

The integral nonlinearity error shown in Figure 1.8 (sometimes seen as simply linearity error) is the deviation of the values on the actual transfer function from a straight line. This straight line can be either a best straight line which is drawn so as to minimize these deviations or it can be a line drawn between the end points of the transfer function once the gain and offset errors have been nullified. The second method is called end-point linearity and is the usual definition adopted since it can be verified more directly.

$$INL_k = \frac{\widetilde{X}_{a,k} - X_{a,k}}{\Delta} \tag{1.3}$$

The relation between INL and DNL is given by

$$INL_k = \sum_{l=1}^k DNL_l \tag{1.4}$$

#### 1.2.1.3 Offset Error

The offset error is defined as the difference between the nominal and actual offset points. For an ADC, the offset point is the midstep value when the digital output is zero. This error affects all codes by the same amount and can usually be compensated for by a trimming process. If trimming is not possible, this error is referred to as the zero-scale error. The offset  $X_{offset}$  of a converter is given by

$$X_{offset} = \frac{1}{2^N} \cdot \sum_{K=0}^{2^N - 1} (\tilde{X}_{a,k} - Xa, k)$$

(1.5)

and represent the average of all the errors in the converter. To eliminate the offset from the INL calculations, the offset should be subtracted from all the analog values  $\tilde{X}_{a,k}$ .

#### 1.2.1.4 Gain Error

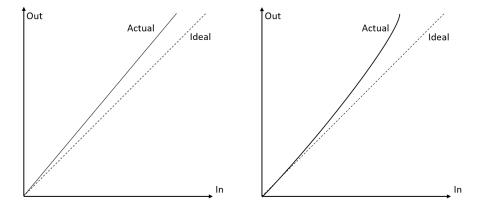

This error represents a difference in the slope of the actual and ideal transfer functions as shown in figure 1.9. This error can be linear or non linear. This error can also usually be adjusted to zero by trimming.

Figure 1.9. Linear and non linear gain error

The actual implementation can present two kind of differences compared to the ideal straight line: the actual output has a linear gain error as shown on the left in figure 1.9 and also non-linearity as in the right of the same figure. The linear gain error does not introduce distortion on the output signal, and can be written as:

$$\widetilde{X}_a = A \cdot X_a + X_{offset} \tag{1.6}$$

where A is the gain. The non-linear gain error is also given by

$$\tilde{X}_a = A_1 \cdot X_a + A_2 \cdot X_a^2 + A_3 \cdot X_a^3 + \dots + X_{offset}$$

(1.7)

the 1.3 can be rewritten taking in account the effect of gain error

$$INL_{k} = \frac{\widetilde{X}_{a,k} - (A \cdot X_{a,k} + X_{offset})}{A \cdot \Delta}$$

(1.8)

## 1.2.2 Frequency Domain Measures

To characterize a data converter, static performances are not sufficient, also is more convenient to characterize the performance in the frequency domain as signal-to-noise ratio (SNR) and spurious-free dynamic range (SNDR).

#### 1.2.2.1 Signal-to-Noise Ratio (SNR)

The signal-to-noise ratio, due to the quantization error is defined as

$$SNR = \frac{P_s}{P_n} = \frac{(\Delta \cdot 2^{N-1})^2}{\Delta^2 / 12} = 1.5 \cdot 2^{2N}$$

(1.9)

where  $P_s$  represents the average power of maximum input signal that not cause saturation;  $P_n$  is the average power of quantization noise. 1.9 can be rewritten in decibel

$$SNR_{dB} = 10 \cdot log\left(\frac{P_s}{P_n}\right) = 6.02 \cdot N + 1.76dB$$

(1.10)

$SNR_{dB}$  is increased by 6 dB for each additional bit of conversion. For a single tone measurement the SNR is the ratio of the power of the input signal and the total noise power, excluding the harmonic components. In the ideal case the SNR value is determined only by the power of quantization error and signal, in real case additional noise source affect the system as example the termal noise and must be taken into account.

#### 1.2.2.2 Spurious Free Dynamic Range (SFDR)

The same non idealities that generate INL and DNL in the static characterization, in case of sinusoidal input generate distortion. Different figures of merit can be defined to characterize the distortion. The ratio of the power of the signal and the power of the largest spurious is called spurious free dynamic range (SFDR), and is expressed as:

$$SFDR(dB_c) = 10 \cdot log\left(\frac{Signal\ Power}{Largest\ Spurious\ Power}\right) = 10 \cdot log\left(\frac{X_1^2}{X_s^2}\right)$$

(1.11)

where  $X_1$  is the rms value of the fundamental and  $X_s$  the rms value of the largest spurious. In some cases the SFDR is defined with full scale input signal as:

$$SFDR(dB_{FS}) = 10 \cdot log \left[ \frac{\left(\frac{FS}{2\sqrt{2}}\right)^2}{X_s^2} \right]$$

(1.12)

#### 1.2.2.3 Harmonic Distorsion $HD_K$

The harmonic distortion referred to the k-th harmonic  $HD_k$  is the ratio between the power of the k-th harmonic and the power of the fundamental frequency of the signal

$$HD_K = 10 \cdot log\left(\frac{k_{-th} \, Harmonic \, Power}{Signal \, Power}\right) = 10 \cdot log\left(\frac{{X_k}^2}{{X_1}^2}\right)$$

(1.13)

where  $X_1$  is the RMS power of the fundamental frequency and  $X_k$  is the RMS power value referred to the k-th harmonic.

#### 1.2.2.4 Total Harmonic Distorsion

The Total Harmonic Distorsion (THD) is the ratio between the sum of the power of all the harmonics and the power of the fundamental frequency in the considered band.

#### 1.2.2.5 Signal-to-noise and Distorsion Ratio (SNDR)

Summing up all the undesired terms such as quantization error (negligible), thermal noise and distortion, a quantity that describes the ratio between the power of the signal and the power of all the undesired terms can be defined. The signal-to-noise and distortion ratio (SNDR) is the ratio of the power of the fundamental and the total noise and distortion power

$$SNDR = 10 \cdot log \left( \frac{Signal\ Power}{Noise\ and\ Distorsion\ Power} \right)$$

(1.14)

#### 1.2.2.6 Effective Number Of Bits (ENOB)

Based on SNDR measure is determined the effective number of bits (ENOB) of an ADC with a full scale sinusoidal input signal as

$$ENOB = \frac{SNDR - 1.76}{6.02} \tag{1.15}$$

both ENOB and SNDR measures are frequency and amplitude dependent. For small amplitude levels the performance are limited by the quantization noise, while for high input amplitude the distortion will limit the performance.

#### 1.2.2.7 Dynamic Range

The Dynamic Range (DR) is defined as the interval between the minimum detectable signal and the full scale (FS) values.

$$DR = 10 \cdot \left(\frac{Maximum \, signal \, power}{Minimum \, signal \, power}\right) \tag{1.16}$$

The Dynamic range is limited upperly by the distortion that appears when the magnitude of the signal cover a significant portion of the signal dynamic of the converter, and is lower limited by the power of the noise that can cover the signal when this is too small.

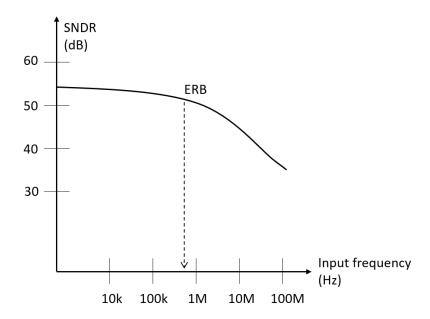

#### 1.2.2.8 Effective Resolution Bandwidth

An important parameter for the data converter is the signal bandwidth that can be handled. The bandwidth is limited by the analog bandwidth of the input circuits in the ADC thus the Sample-and-Hold, or by the Effective-Resolution-Bandwidth (ERB) thus the ADC. The input signal frequency must be smaller than the Nyquist frequency (half the sampling frequency) to avoid aliasing in conventional applications of ADCs. The bandwidth can be larger than the Nyquist frequency for sub-sampling ADCs. To specify the frequency behaviour of the converter it is common to plot the SNDR, SFDR or SNR as function of input frequency as illustrated in 1.10. The effective resolution bandwith is the input frequency where SNDR has dropped 3dB (1/2 bit ENOB).

Figure 1.10. Effective Resolution Bandwidth

#### 1.2.2.9 Inter-Modulation Distortion

When the input signal is multi-tone inter-modulation distortion (IMD) appears. Assume that the frequencies of the the input tone are respectively  $f_1$  and  $f_2$ , and the sampling rate  $f_s$ , intermodulation disortion appear at frequency

$$(k \cdot f_1 + m \cdot f_2) mod(f_s/2) \tag{1.17}$$

where k and m are integer numbers, and further  $k \neq 0$  and  $f_1 \neq f_2$ . The intermodulation distortion is calculated as

$$IMD = 10 \cdot log\left(\frac{\sum X_{k,m}^2}{X_0^2}\right) \tag{1.18}$$

where  $X_0$  is the rms value of the fundamental, and  $X_{k,m}$  is the rms value of the tones.

#### 1.2.3 Dynamic Performance

Several unwanted effects appear when the input signal changes rapidly, these dynamic errors often are frequency dependent and increase when signal amplitude or frequency are increased. Moreover, the same static error that generates INL and DNL causes distortion when the input signal is time variable as example a sinusoidal input. Thus in some applications such as telecommunications this kind of information has much weight than the static errors.

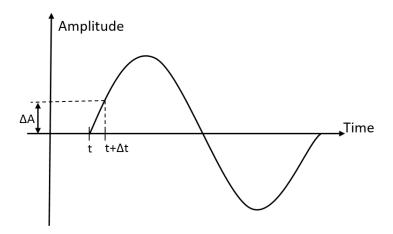

#### 1.2.3.1 Sampling Time Uncertainly

The dynamic performance of an ADC is limited by the precision of the sampling instant in the Sample-and-Hold circuit. Many unwanted phenomena such as switch imperfections, clock jitter, and signal-dependent delay can generate uncertainty on the sample instant.

Figure 1.11. Sampling time uncertainty generates an error on the sampled signal

In figure 1.11 the desired sampling time is t but due to the circuit non-ideality the actual sampling time is  $t + \Delta t$ . This delay causes an error  $\Delta A$  that depends on the slope of the input signal. For a sinusoidal input signal, the worst case is when zero crossing happens.

$$\Delta A_{max} = \Delta t \cdot \frac{\partial}{\partial t} V_{in}(t)|_{t=0} = \omega \cdot A \cdot \cos(\omega t) \cdot \Delta t = \omega \cdot A \cdot \Delta t$$

(1.19)

where A is the amplitude of the sinusoid. The error increases linearly with frequency and is independent of the sampling frequency. Many techniques can be applied to reduce this error, for instance, the bottom plate sampling. Anyway, the performance is limited by clock jitter. Assuming the clock jitter as random noise with variance  $\sigma_t^2$  the error power can be approximated as

$$v_{jn}^2 = \sigma_t^2 \cdot \frac{1}{T} \int_0^T \left( \frac{\partial}{\partial t} V_{in}(t) \right)^2 dt \tag{1.20}$$

where T is the integration time. For a sinusoidal input the power error is

$$v_{in}^2 = (2\pi f_{in}A)^2 \sigma_t^2 / 2 (1.21)$$

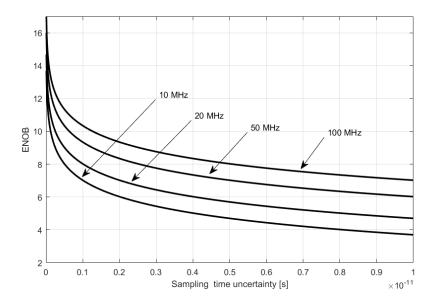

where A is the amplitude and  $f_{in}$  the frequency of the sinusoid. Thus the SNDR is limited by

$$SNDR_{lim} = 10 \cdot log \frac{1}{(2\pi f_{in}\sigma_t)^2}$$

(1.22)

and then also the ENOB is limited

$$ENOB_{lim} = \frac{10 \cdot log \frac{1}{(2\pi f_{in}\sigma_t)^2} - 1.76}{6.02}$$

(1.23)

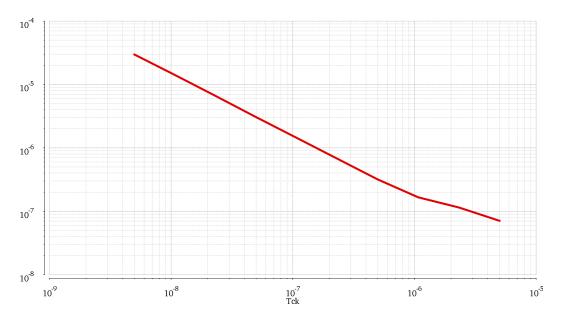

SNDR is independent from the sampling frequency. The obtainable ENOB as function of the clock jitter  $\sigma_t$  is plotted for different input frequencies in figure 1.12. The figure shows the performance decreases rapidly for high sampling rate.

Figure 1.12. ENOB vs sampling time uncertainty for different value of sampling frequencies

#### 1.2.3.2 Thermal Noise

A limiting factor in Sample-and-Hold circuit is the thermal noise. Commonly, in wideband circuits, the thermal noise is dominant on flicker noise because is folded back into the signal band by the sampling technique, this introduces a fundamental limitation. In Sample-and-Hold the thermal noise power is kT/C. Assuming as input a sinusoidal signal with amplitude  $V_{in}$ , the SNDR is

$$SNDR = 10 \cdot log \left( \frac{V_{in}^2}{2 \cdot kT} \cdot C \right) \tag{1.24}$$

The voltage swing is limited by the power supply voltage, then increasing the sampling capacitor is the only way to increase the SNDR. For moderate resolution the minimum capacitor size for the noise requirement is very small, and a larger capacitor value may be chosen for other reasons (such as process error that can generate mismatch that is area dependent). For high resolution a huge capacitor is required to handle the thermal noise, this implies a larger power consumption.

# 1.3 Pipeline ADC

The pipeline ADC has become the most popular ADC architecture for applications that require sampling rates from a few mega samples per second (MSps) up to 600 Msps, and resolutions ranging from eight bits at the faster sample rates up to 16 bits at the lower rates. These conversion frequences and resolutions cover a wide range of applications such as environmental monitoring, biomedical applications and telecommunication. For low sampling frequencies the successive approximation register (SAR) architecture, and oversampling/sigma-delta ADCs dominate the market. For higher sampling rates usually flash ADCs are used. Nonetheless, pipelined ADCs of various forms have improved greatly in speed, resolution, dynamic performance, and power consumption in recent years.

Figure 1.13. Block diagram of an ADC pipeline

In figure 1.13 a principle schematic of a pipelined ADC is shown. In each stage the

analog input, Vin, is first sampled and held steady by a sample-and-hold structure, while the flash sub-ADC quantizes it in N bits (N bit is the number of conversion bit of each stage). The output of the sub-ADC is taken as input by the sub-DAC, and the analog output is subtracted from the input. This residue is the quantization error of the sub-ADC and then this signal is amplified by a factor  $2^N$  and fed to the next stage. This gained-up residue continues through the pipeline, providing N bits per stage until it reaches the last sub-ADC, which resolves the last N bits.

Because the bits from each stage are determined at different points in time, all the bits corresponding to the same sample are time-aligned with shift registers before being fed to the digital-error-correction logic. Note that when a stage finishes processing a sample, determining the bits, and passing the residue to the next stage, it can then start processing the next sample received from the sample-and-hold embedded within each stage. This pipelining action is the reason for the high throughput. The pipeline structure is affected by data latency, because each sample must propagate through the entire pipeline before all its associated bits are available for combining in the digital-error-correction logic.

#### 1.3.1 Component Accuracy

Some errors such as gain error of error-amplifier or non-linearity in sub-DACs are not corrected by digital correction. The Sample-and-Hold at the beginning of the pipeline chain and the first stage's sub-DAC actually require the same accuracy of the whole ADC. The circuits in subsequent stages require less accuracy. This need for reduced accuracy is due to the fact that the later stages' error terms are divided down by the preceding interstage gain. The stages in the pipeline converter can be made progressively smaller to obtain a reduction in power consumption.

Usually, in pipelined ADCs, the Sample-and-Hold, sub-DAC, summation node, and gain amplifier are implemented as a single switched-capacitor circuit block called a multiplying DAC (MDAC). The major factor limiting MDAC accuracy is the intrinsic capacitor mismatch. In general, for about 12 bits of accuracy or higher, some form of capacitor/resistor trimming or digital calibration is required, especially for the first two stages.

#### 1.3.2 The Multiplying DAC

The pipeline ADC is composed of several stages each with a low-resolution ADC, a DAC, and an error amplifier that generates the analog output signal. The output signal of the MDAC is

$$out_i = G_i \cdot (in_i - DAC_i) \tag{1.25}$$

where  $G_i$  is the gain of the MDAC,  $in_i$  the analog input and  $DAC_i$  the output

of the DAC referred to the *i*-th stage. If  $DAC_i = 0$  the MDAC behaves as a Sample-and-Hold amplifier, whereas if  $in_i = 0$  it behaves as a DAC. Therefore the Sample-and-Hold and the DAC circuits can be considered as special cases of the MDAC and are not treated separately.

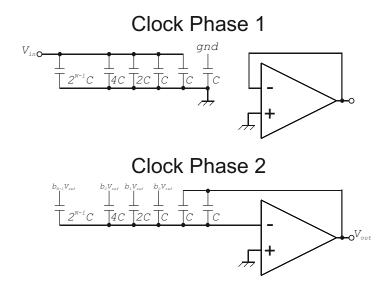

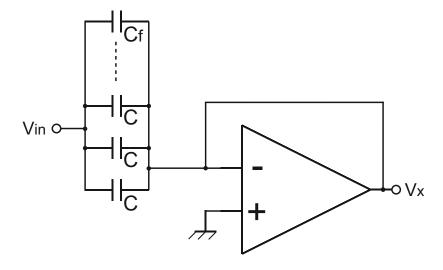

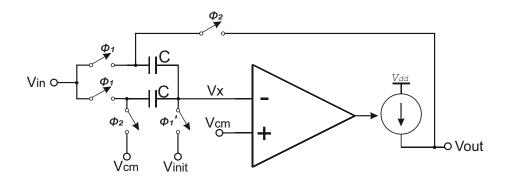

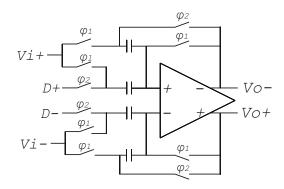

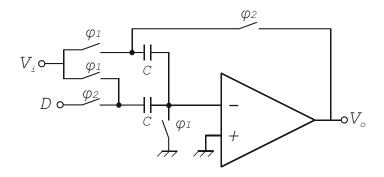

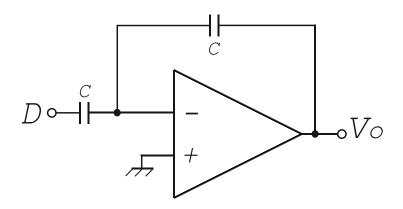

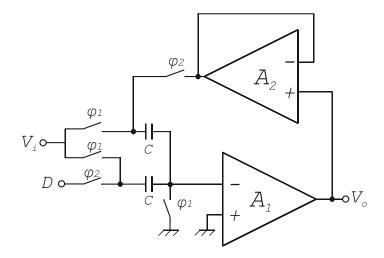

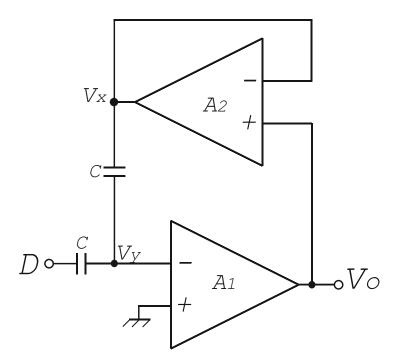

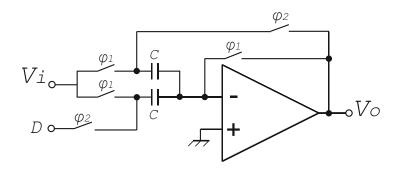

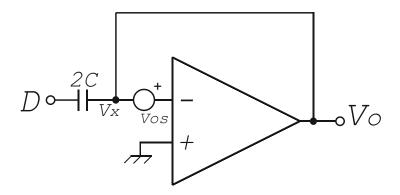

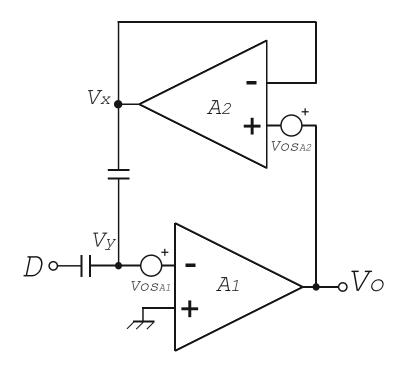

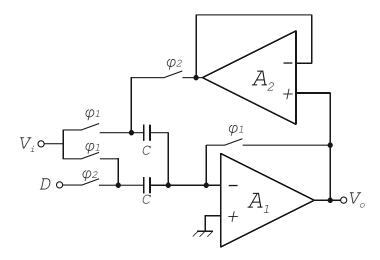

Figure 1.14. The SC MDAC of a pipeline converter

In literature different MDAC structures are available, in this work only the switching capacitors approach is considered. A common implementation of SC-MDAC is shown in 1.14, it has N input bits  $b_{n-1},...,b_0$ , where  $b_{n-1}$  is the MSB and  $b_0$  the LSB. A single bit of digital correction is used and then the residue gain is decreased by a factor 2. In the sampling phase  $\phi_1$ , all capacitors except one are connected to the input voltage of the circuit, collecting the total charge on the top plates of the capacitors

$$q_s = V_{in} \cdot (2^{N-1}C + \dots + C + C) \tag{1.26}$$

On the hold phase two of the capacitors are connected to the output, and the other are connected to the reference voltage  $\pm V_{ref}$  according to the output of the sub-DAC. The total charge stored in this phase is

$$q_{h} = \left(V_{out} + \frac{V_{out}}{A}\right) \cdot 2C + V_{ref} \cdot (2^{N-1} \cdot b_{N-1} \cdot C + \dots + b_{0} \cdot C) + \frac{V_{out}}{A} \cdot (2^{N-1}C + \dots + C) + \frac{V_{out}}{A} \cdot C_{p}$$

(1.27)

where A is the DC-gain of the opamp,  $C_p$  the parasitic capacitor, and  $b_{N-1},...,b_0 = \pm 1$  are determined by the digital output of the sub-ADC. The total charge is con-

served among the phases, then (1.26) is equal to (1.27) thus

$$V_{out} = \frac{V_{in} \cdot 2^{N-1} - \frac{V_{ref}}{2} \cdot (2^{N-1} \cdot b_{N-1} + \dots + b_0)}{1 + \frac{C_{tot}}{2A_0C}}$$

(1.28)

the reference voltages in the DAC are  $V_{ref-} = -\frac{FS}{2}$  and  $V_{ref+} = \frac{FS}{2}$ , where FS is the full-scale input range of the converter.

#### 1.3.2.1 Effect of Finite Opamp Gain and Parasitic Capacitors

The non-ideality of the circuit such as finite opamp gain and parasitic capacitance, can affect the output voltage of the MDAC. From the first order Taylor expansion of (1.28) we get

$$\frac{1}{1+\epsilon} \approx 1 - \epsilon \to \frac{1}{1 + \frac{C_{tot}}{2A_0C}} \approx 1 - \frac{C_{tot}}{2A_0C}$$

(1.29)

Thus the gain error is

$$\epsilon_G = \frac{C_{tot}}{2A_0C} = \frac{2^N + 1 + \frac{C_p}{C}}{2A_0} \approx \frac{2^{N-1}}{A_0}$$

(1.30)

this approximation is valid for large values of N. The gain error is the same for the input signal and sub-DAC output signal, therefore the gain error can be considered as an error at the output of the subtracter.

#### 1.3.2.2 Effect of Mismatch

The residue of an MDAC stage is given by

$$V_{out} = \frac{\sum_{1}^{2^{n}} C_{i}}{C_{f}} V_{in} - \left[ \frac{\sum_{1}^{k} C_{i}}{\sum_{1}^{2^{n}} C_{i}} V_{ref} - \frac{\sum_{k=1}^{2^{n}} C_{i}}{\sum_{1}^{2^{n}} C_{i}} V_{ref} \right]$$

(1.31)

if the values of  $\sum_{i=1}^{2^n} C_i$  and  $C_f$  are different, the transcharateristic of the MDAC will be affected by gain error. The mismatch between sampling capacitors,  $C_i$  also affects the linearity of the DAC. The mismatch between two capacitors is determined by the area of a capacitor

$$mismatch \propto \frac{1}{\sqrt{capacitor\ area}}$$

(1.32)

Thus, to achieve an highly linear ADC, large capacitors are required to minimize the effect due to capacitor mismatch. Commonly, during the design of the MDAC the value of capacitors is not set by the thermal noise requirement, but the high linearity requirements sets a lower bound on the value of capacitors to suppress the effect of mismatch. The layout of the MDAC should be done using design techniques that improves the capacitor matching, such as using arrays of unit size capacitors in a highly symmetric configuration, and use dummy capacitors around the periphery

of the array to overcome the fringe effect [2]. An arbitrarily high level of matching cannot be achieved using good layout techniques alone, hence limiting pipelined ADC resolution to the medium-high range as shown in figure 1.1. A typical solution is to use digital calibration techniques as discuss in chapter 3.

#### 1.3.2.3 Speed

Under the single pole condition, the settling of the output of the opamp is linear, and the error due to finite settling time  $\epsilon_r$  is described by

$$\epsilon_r = e^{-t_s \cdot \omega_{-3dB}} \tag{1.33}$$

where  $t_s$  is the settling time, and  $\omega_{-3dB}$  is the bandwidth of the opamp. Settling error causes a finite gain error on the output signal of MDAC. The maximum settling time is half of the sampling period  $1/f_s$ . Considering the unity-gain bandwidth  $\omega_u$  as

$$\omega_u = \frac{\omega_{-3dB}}{\beta} \tag{1.34}$$

that for a single stage opamp is  $\omega_u = g_m/C_{load}$ . In the previous expression  $\beta$  is the feedback factor that is equal to

$$\beta = \frac{2C}{(2^N + 1)C + C_p} = \frac{2}{(2^N + 1) + C/C_p}$$

(1.35)

The capacitive load for a single stage is

$$C_{load} = \beta \cdot ((2^N - 1)C + C_p) + C_{next}$$

(1.36)

where  $C_{next}$  is the capacitive load of the next stage. Under the hypothesis of identical stages, and for large number of stages N, the (1.36) becomes

$$C_{load} = \beta \cdot ((2^N - 1)C + C_p) + 2^N C \approx 2^N C$$

(1.37)

The maximum speed of the MDAC can be calculated as

$$f_s = \frac{1}{2t_s} = \frac{\omega_{-3dB}}{2ln(1/\epsilon_r)} = \frac{\omega_u \cdot \beta}{2ln(1/\epsilon_r)} = \frac{\frac{g_m}{2^N C} \cdot \frac{2}{(2^N + 1) + C_p/C}}{2ln(1/\epsilon_r)}$$

(1.38)

that can be approximated with

$$f_s \simeq \frac{g_m}{2^{2N}C \cdot ln(1/\epsilon_r)} \tag{1.39}$$

For low gain or large  $\beta$  the linear settling assumption is not valid, and the settling will restricted by slew rate, and the settling time is increased if compared with (1.39).

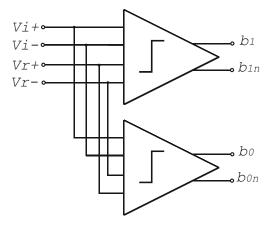

#### 1.3.3 subADC

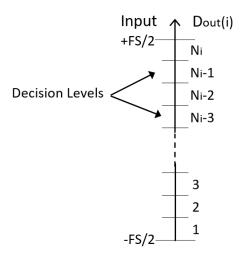

The subADC in *i*-th stage is assumed to have output code  $D_{out}(i)$ , that is an integer number ranging from 0 to  $N_i - 1$ , and can be calculated as

$$D_{out}(i) = \sum_{l=0}^{n_i - 1} b_{i,l} \cdot 2^l$$

(1.40)

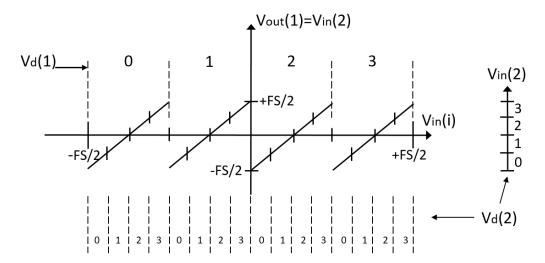

where  $b_{i,l}$  is the l-th output bit of the i-th stage. We assume that the input signal range from -FS/2 to +FS/2 and that the threshold levels are equally spaced over the entire input range as shown in figure 1.15

Figure 1.15. The input dynamic is divided in  $2^N$  levels

Figure 1.15 shows the input range subdivided  $N_i$  times, where each segment corresponds to one output code. The analog value corresponding to one LSB is

$$LSB_i = \frac{FS}{N_i} \tag{1.41}$$

#### 1.3.4 subDAC

The analog output of the subDAC for a certain code is determined by the expression

$$V_{dac}(i) = \left(D_{out}(i) - \frac{N_i - 1}{2}\right) \cdot \frac{FS}{N_i}$$

(1.42)

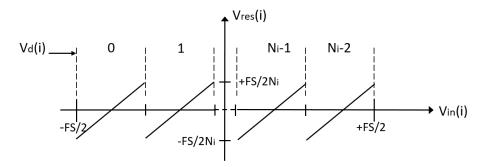

## 1.3.5 Sample-and-Hold and Residue Amplifier

In a pipeline stage, the difference between the analog input and the DAC output is the residue

$$V_{res}(i) = V_{in}(i) - V_{dac}(i) = V_{in}(i) - \left(D_{out}(i) - \frac{N_i - 1}{2}\right) \cdot \frac{FS}{N_i}$$

(1.43)

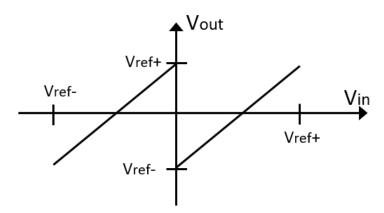

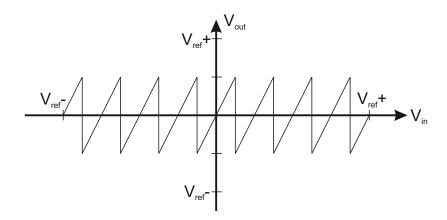

Figure 1.16. Transfer function of an N-bit MDAC

Figure 1.16 shows the transfer function of the subtractor. The output swing is  $N_i$  times smaller than its input. It is therefore necessary to amplify the residue in order to utilize the entire rampe of the following stage. The analog output of one stage can be calculated by

$$V_{out}(i) = V_{res}(i) \cdot G_i = \left[ V_{in}(i) - \left( D_{out}(i) - \frac{N_i - 1}{2} \right) \cdot \frac{FS}{N_i} \right] \cdot G_i$$

(1.44)

Choosing the signal swing equal in each stage, and the gain as  $N_i$ , the output signal can be written as

$$V_{out}(i) = \left[ V_{in}(i) - \left( D_{out}(i) - \frac{N_i - 1}{2} \right) \cdot \frac{FS}{N_i} \right] \cdot N_i$$

(1.45)

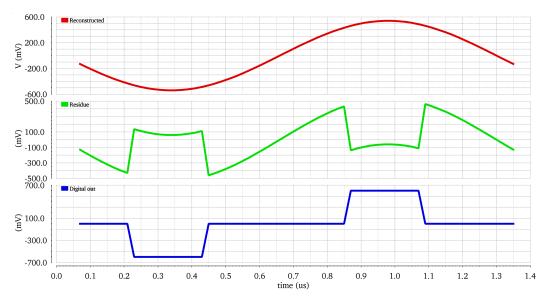

### 1.3.6 Digital Output Recostruction

The digital outputs of all stages must be combined to generate the total output code.

As shown in figure 1.17 the output signal of *i*-th stage feeds the next stage, hence each segment of the sawtooth-shaped output signal of the *i*-th stage will be quantized by the i + 1-th stage. The number of codes in a pipelined ADC where  $G_i = N_i$  can be calculated as

$$N_{tot} = \prod_{i=1}^{m} N_i \tag{1.46}$$

if all resolutions are choosen as  $N_i = 2^{n_i}$  the total number of bits is given by

$$n_{tot} = \prod_{i=1}^{m} n_i (1.47)$$

using the (1.44) the input signal of the first stage can be written as

$$V_{in}(1) = V_{dac}(1) + \frac{V_{out}(1)}{G_1}$$

(1.48)

**Figure 1.17.** Analog output of first stage and corresponding digital output codes of a two stage ADC

since  $V_{in}(2) = V_{out}(1)$  we can use again (1.44) to get

$$V_{in}(1) = V_{dac}(1) + \frac{V_{dac}(2)}{G_1} + \frac{V_{out}(2)}{G_1 \cdot G_2}$$

(1.49)

repeating iteratively for all the stages we get

$$V_{in}(1) = V_{dac}(1) + \frac{V_{dac}(2)}{G_1} + \dots + \frac{V_{dac}(i)}{G_1 \dots G_{i-1}} + \dots + \frac{V_{dac}(m)}{G_1 \dots G_{m-1}} + V_{res}(m)$$

(1.50)

the residue of the last stage  $V_{res}(m)$  corresponds to the quantization error of the converter. Using (1.42) and (1.50) we get

$$V_{in}(1) = \sum_{i=1}^{m} \left[ \left( D_{out}(i) - \frac{N_i - 1}{2} \right) \cdot \frac{FS}{N_i} \cdot \frac{1}{\prod_{k=1}^{i-1} G_k} \right] + V_{res}(m)$$

(1.51)

The total output code of a converter is

$$D_{out} = \sum_{i=1}^{m} \left( D_{out}(i) \cdot \frac{N_m}{N_i} \cdot \prod_{k=i}^{m-1} G_k \right)$$

(1.52)

when  $G_k = N_i$ , (1.52) becomes

$$D_{out} = \sum_{i=1}^{m} \left( D_{out}(i) \cdot \prod_{k=i+1}^{m} N_k \right)$$

(1.53)

#### 1.3.7 Digital Error Correction

To reduce the accuracy requirement of the sub-ADC and sub-DAC, the pipeline ADCs employs a technique called "digital error correction". In a pipeline ADC the

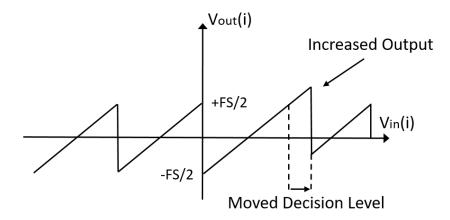

main issue is due to the offset in the sub-ADC, because, if one of the comparators in the first N-bit flash ADC has a significant offset, its threshold is moved, as shown in figure 1.18. Thus, when an analog input is close to the trip point, an incorrect code is provided to sub-DAC, consequently an incorrect DAC output would result, that produces a wrong residue.

Figure 1.18. Moved ADC decision level increases signal swing.

As long as the amplified residue does not saturate the subsequent stage, the LSB code generated by the remaining pipeline will give the correct ADC output code. Much smaller is the residue gain, and more larger is the acceptable error. The maximum decision deviation is given by

$$\Delta V = \pm \frac{FS}{2} \left( \frac{1}{G_i} - \frac{1}{N_i} \right) \tag{1.54}$$

if the residue gain is 2 the decision deviation become

$$\Delta V = \pm \frac{FS}{2N_i} \tag{1.55}$$

Hence, the error in  $ADC_i$  can be  $\pm LSB_1/2$ , without causing a large conversion error. The implication is that none of the sub-ADCs has to be accurate as the entire ADC. In fact, the sub-ADC in each stage requires only N bits of accuracy.

## 1.4 MDAC Implementation

Splitting the conversion in a pipeline chain allows an optimization of the conversion speed respect to the speed of the used circuit. The first stage need the maximum accuracy, the latter stages can be designed with reduced accuracy without influencing the overall resolution. Different architectures can be used to achieve the required resolution. In this section different architecture will be discussed.

#### 1.4.1 1 bit MDAC

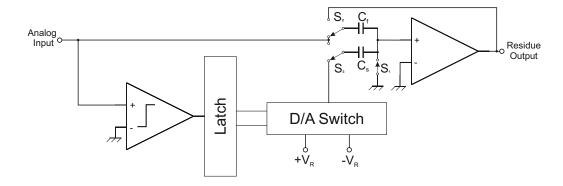

The implementation of 1-bit MDAC is shown in figure 1.19, and the transfer function is reported in figure 1.20. As shown the subADC is reduced to a zero crossing comparator.

Figure 1.19. Single bit MDAC

Figure 1.20. 1-bit residue signal

The result of the comparation drives the sub DAC, that is a switch that connects  $+V_R$  or  $-V_R$  to the subtractor. During the sampling phase switch  $S_1$  is closed and

switches  $S_2$  and  $S_3$  connects the analog input to the sampling capacitors to store the analog input. During the next phase,  $S_1$  is opened, and  $S_2$  connect the capacitor  $C_2$  between the input and the output of the opamp. Switch  $S_3$  connects the capacitor  $C_1$  to the subDAC. During this phase the reference voltage  $V_R$  is added or subtracted to the analog input signal. The analog output result is stored on the capacitor  $C_2$ . Under the condition of charge conservation between the two phases, the output voltage can be written as

$$V_{out} = \left(1 + \frac{C_1}{C_2}\right) \cdot V_{in} + D \cdot V_R \tag{1.56}$$

where D is the output data of the subADC and has value  $\pm 1$ . Choosing  $C_1 = C_2$  then a gain of 2 is obtained. The matching between the two capacitors is a keypoint to determine the accuracy. Figure 1.20 shows the ideal transfer function of the 1-bit MDAC. When the circuit is affected by offset or the gain is larger than 2, the following stage is fed with an error affected signal.

#### 1.4.2 1.5 bit MDAC

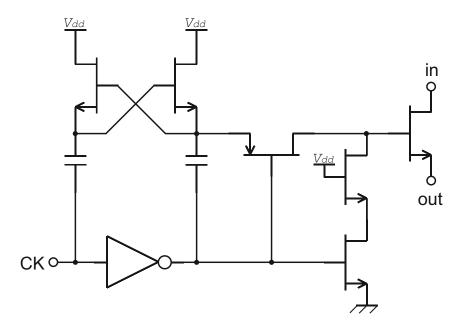

An improvement of this MDAC structure is the 1.5-bit MDAC.

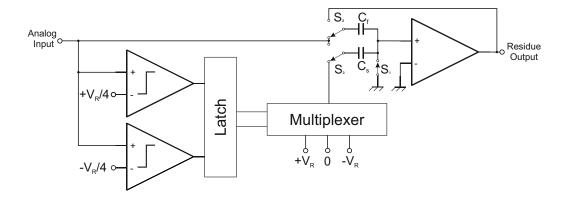

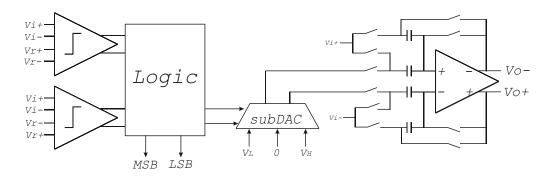

Figure 1.21. 1.5 bit MDAC implementation

As shown in figure 1.21 the subADC in this structure has 2 levels that are set on  $+\frac{V_r}{4}$  and  $-\frac{V_r}{4}$ . The subDAC consists of a three-level multiplexer with reference voltages  $+V_R$ , 0 and  $-V_R$ . During the sampling phase the switch  $S_1$  is closed to ground and through  $S_2$  and  $S_3$  the input signal is stored on the capacitors  $C_s$  and  $C_f$ . During the next phase called "error amplification phase" the operation performed depends on the data of the subADC

$$V_{residue} = \begin{cases} \left(1 + \frac{C_s}{C_f}\right) V_{in} - V_R, & \text{if } V_{in} > \frac{V_R}{4} \\ \left(1 + \frac{C_s}{C_f}\right) V_{in}, & \text{if } -\frac{V_R}{4} < V_{in} < +\frac{V_R}{4} \\ \left(1 + \frac{C_s}{C_f}\right) V_{in} + V_R, & \text{if } V_{in} > -\frac{V_R}{4} \end{cases}$$

(1.57)

In this phase the switch  $S_1$  is open, and the capacitor  $C_f$  is connected as a feedback element over the opamp, while capacitor  $C_s$  is connected at the output of the subDAC. Also in this architecture the capacitors  $C_s$  and  $C_f$  are equal to set the gain of the stage exactly to 2x.

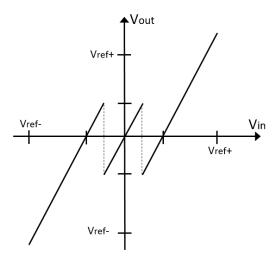

Figure 1.22. 1.5-bit residue signal

The transfer function of this stage is reported in figure 1.22. The 2-level ADC in this system enables correction of signal errors due to non exact gain, offset and switch charge transfer. In a piplined ADC with digital correction the residue gain is reduced to introduce redundancy.

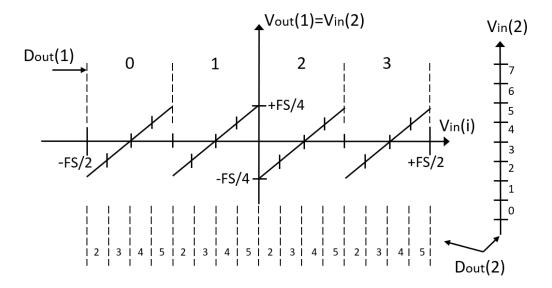

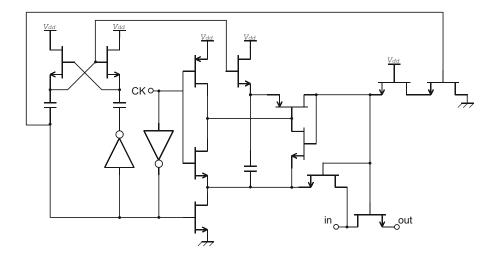

**Figure 1.23.** Analog output of the first stage and corresponding digital output codes for a two stage ADC with reduced residue gain.

Figure 1.23 illustrates two stage ADC, where the first stage has 4 codes and

the second stage has 8 codes. The residue gain has been reduced from 4 to 2. The output signal swing of the first stage is now only half the input range of the following stage. This means that the codes 0,1,6 and 7 will never be used. The gain is usually reduced by a factor 2 but can in principle be chosen arbitrarily. However, it is usually desirable to have the same step size for all the codes. The gain is then restricted to values that give the correct step size at the decision levels in the first stage.

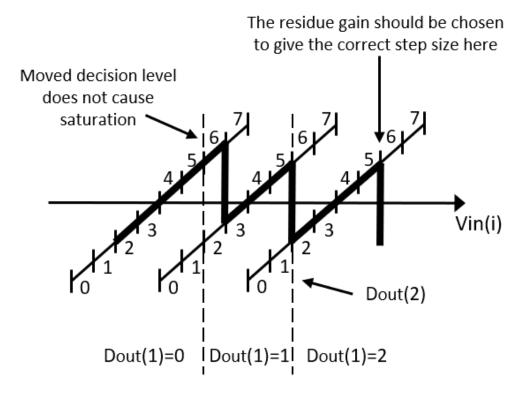

**Figure 1.24.** A moved decision line does not cause saturation in the following stage when the residue gain is reduced.

Figure 1.24 shows the output when one of the decision lines has been moved. In this figure it is seen that moving the decision level will not cause saturation in the following stage since there are now the redundant codes **0**, **1** and **6**, **7** in stage 2. The digital correction can correct errors in the comparators as long as the residue is within the FS range of the following stage. The smaller the residue gain, the larger errors can be accepted. The maximum decision line deviation is given by

$$\Delta V = \pm \frac{FS}{2} \left( \frac{1}{G_i} \frac{1}{N_i} \right) \tag{1.58}$$

If the gain factor is reduced by a factor 2 we get

$$\Delta V = \pm \frac{FS}{2N_i} \tag{1.59}$$

Hence the error in the  $ADC_i$  can be  $\pm LSB_i/2$ , without causing a large conversionerror. A drawback of the digital correction is, as was illustrated by the example above, that several code combinations give the same total output code. The total resolution of the converter is thus decreased when digital correction is introduced unless more stage are added.

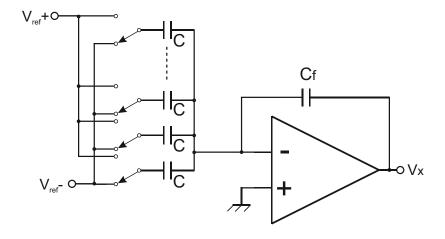

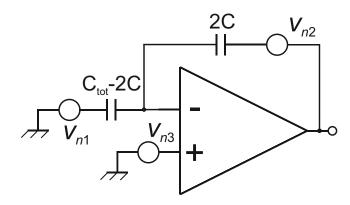

#### 1.4.3 Multi bit MDAC

Usually pipeline ADCs with more than 12 bit resolution use at the first stage a multi-bit quantizer. Then the ADC is completed with 1.5 bit stages.

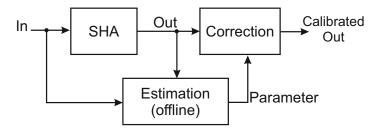

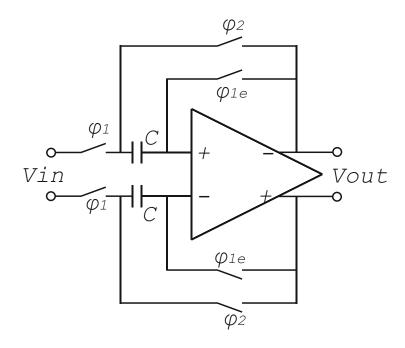

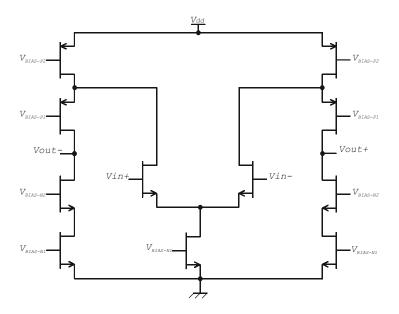

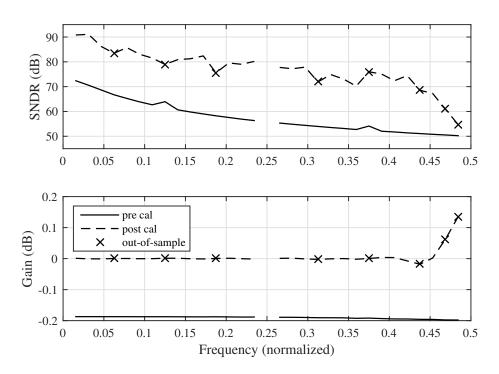

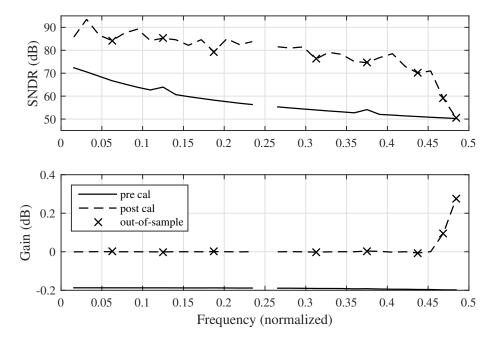

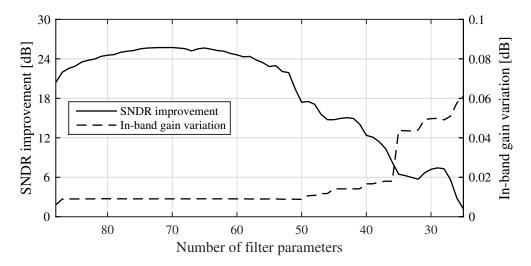

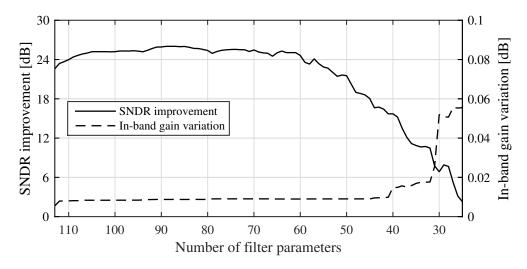

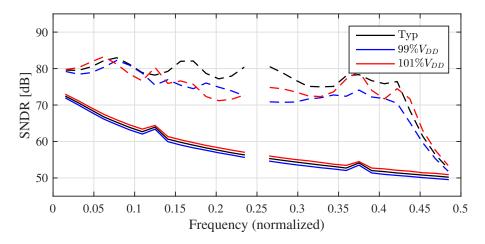

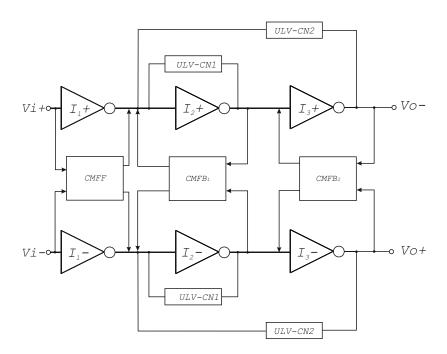

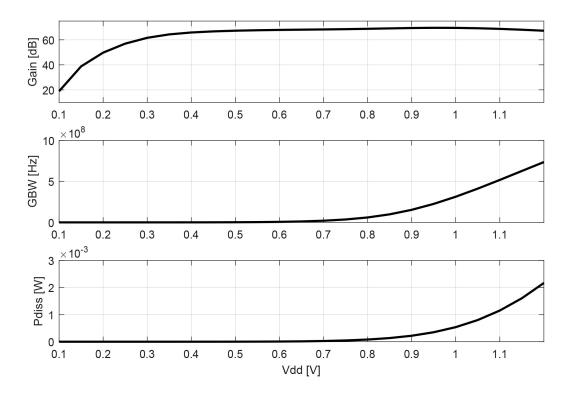

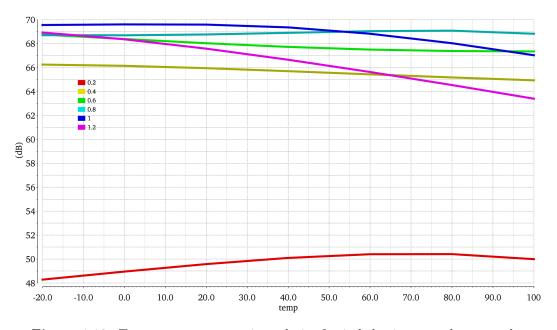

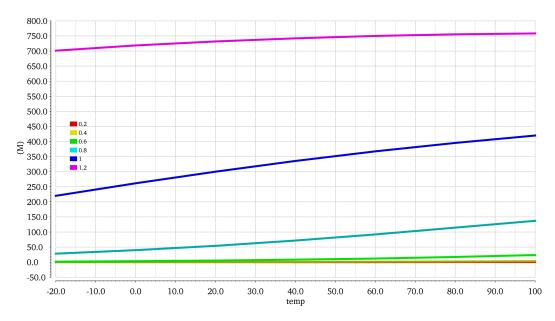

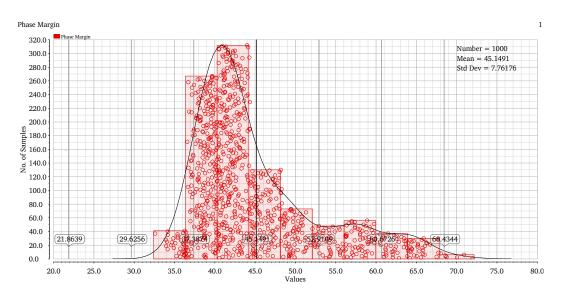

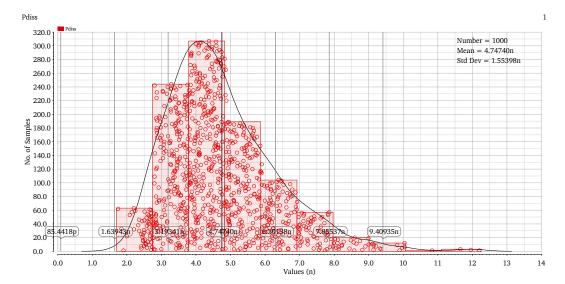

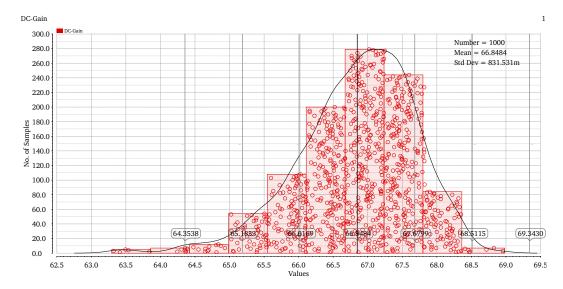

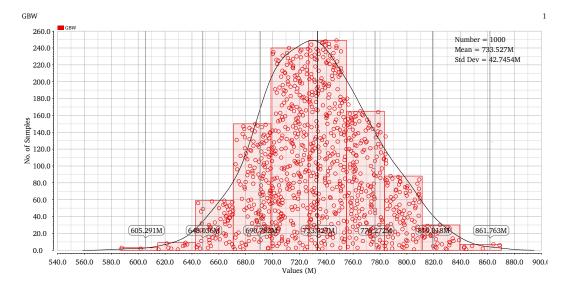

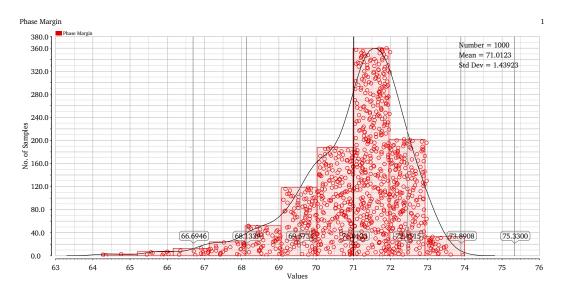

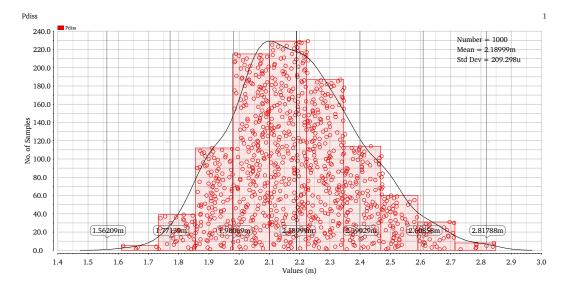

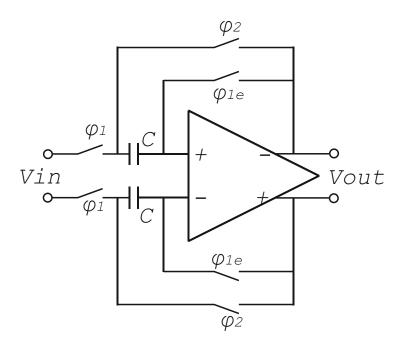

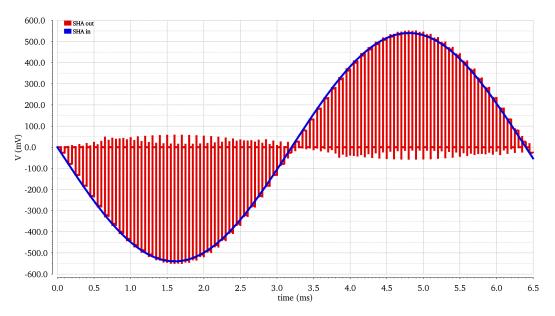

Figure 1.25. Multi-bit MDAC during the sampling phase